|

|

PDF S93C46B Data sheet ( Hoja de datos )

| Número de pieza | S93C46B | |

| Descripción | (S93Cx6B) CMOS SERIAL E2PROM | |

| Fabricantes | Seiko Instruments | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de S93C46B (archivo pdf) en la parte inferior de esta página. Total 42 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

Rev. 3.1_01

CMOS SERIAL E2PROM

S-93C46B/56B/66B

The S-93C46B/56B/66B is a high speed, low current

consumption, 1/2/4 K-bit serial E2PROM with a wide

operating voltage range. It is organized as 64-word

× 16-bit, 128-word × 16-bit, 256-word × 16-bit,

respectively. Each is capable of sequential read, at

which time addresses are automatically incremented

in 16-bit blocks. The instruction code is compatible

with the NM93CS46/56/66.

Features

• Low current consumption

Standby: 1.5 µA Max. (VCC = 5.5 V)

Operating: 0.8 mA Max. (VCC = 5.5 V)

0.4 mA Max. (VCC = 2.5 V)

• Wide operating voltage range Read:

1.8 to 5.5 V (at −40 to +85°C)

Write:

2.7 to 5.5 V (at −40 to +85°C)

• Sequential read capable

• Write disable function when power supply voltage is low

• Function to protect against write due to erroneous instruction recognition

• Endurance:

107 cycles/word* (at +25°C) write capable,

106 cycles/word* (at +85°C)

3 × 105 cycles/word* (at +105°C)

* For each address (Word: 16 bits)

• Data retention: 10 years (after rewriting 106 cycles/word at +85°C)

• S-93C46B:

1 K-bit NM93CS46 instruction code compatible

• S-93C56B:

2 K-bit NM93CS56 instruction code compatible

• S-93C66B:

4 K-bit NM93CS66 instruction code compatible

• High-temperature operation: +105°C Max. supported

(Only S-93Cx6BD0H-J8T2, S-93Cx6BD0H-T8T2)

Packages

Package name

8-Pin DIP

8-Pin SOP(JEDEC)

8-Pin TSSOP

SNT-8A

Package

DP008-F

FJ008-A

FT008-A

PH008-A

Drawing code

Tape

FJ008-D

FT008-E

PH008-A

Reel

FJ008-D

FT008-E

PH008-A

Caution This product is intended to use in general electronic devices such as consumer electronics,

office equipment, and communications devices. Before using the product in medical

equipment or automobile equipment including car audio, keyless entry and engine control

unit, contact to SII is indispensable.

Seiko Instruments Inc.

1

1 page

www.DataSheet4U.com

Rev.3.1_01

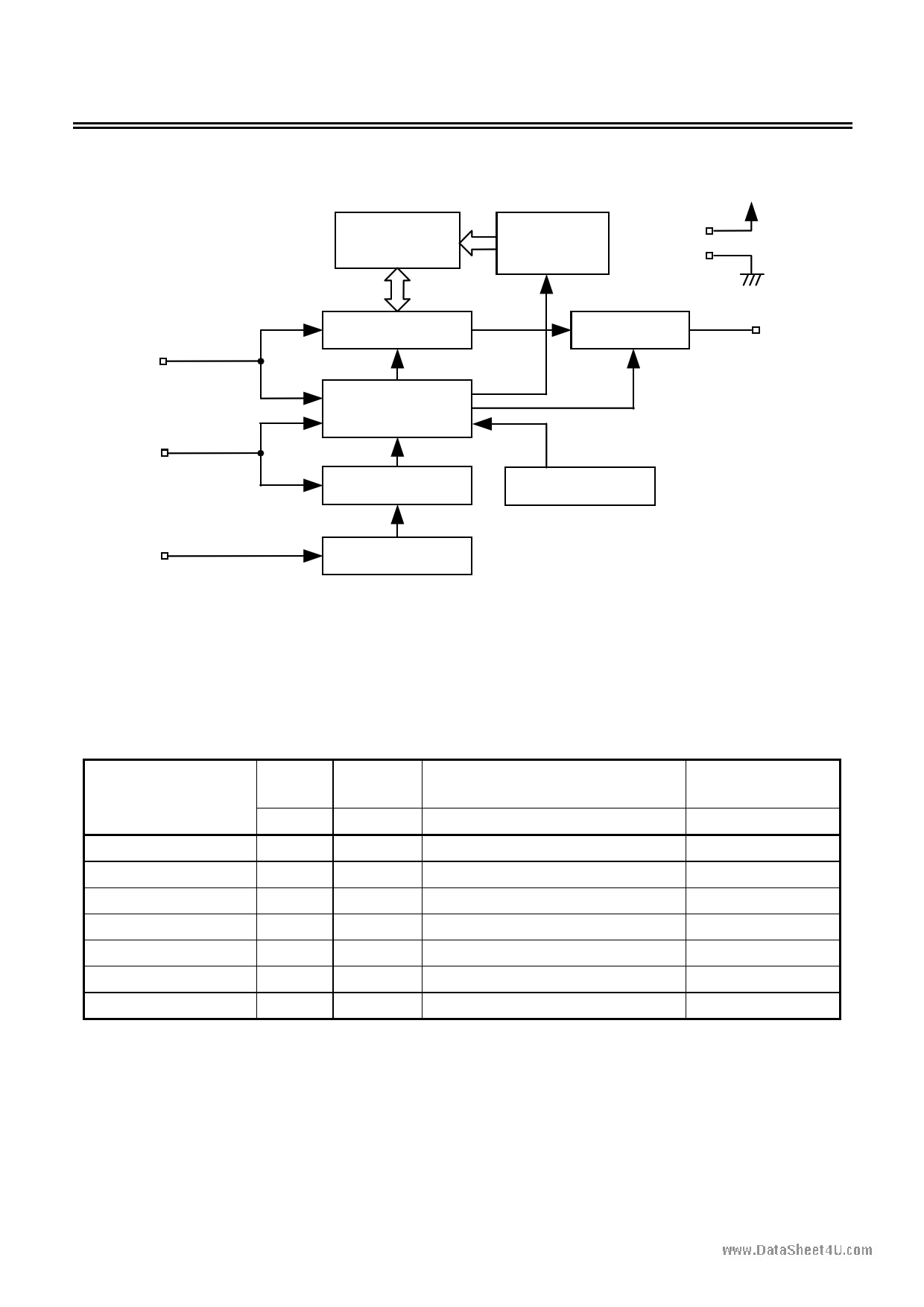

Block Diagram

CMOS SERIAL E2PROM

S-93C46B/56B/66B

Memory array

Address

decoder

VCC

GND

Data register

Output buffer

DO

DI

Mode decode logic

CS

Clock pulse

monitoring circuit

Voltage detector

SK Clock generator

Figure 6

Instruction Sets

1. S-93C46B

Table 6

Instruction

Start Bit Operation

Code

Address

Data

SK input clock

1 23456789

10 to 25

READ (Read data)

1 1 0 A5 A4 A3 A2 A1 A0 D15 to D0 Output*1

WRITE (Write data)

1 0 1 A5 A4 A3 A2 A1 A0 D15 to D0 Input

ERASE (Erase data)

1 1 1 A5 A4 A3 A2 A1 A0

WRAL (Write all)

1 0 0 0 1 x x x x D15 to D0 Input

ERAL (Erase all)

1 0010xxxx

EWEN (Write enable) 1 0 0 1 1 x x x x

EWDS (Write disable)

1

00 00 x x x x

*1. When the 16-bit data in the specified address has been output, the data in the next address is output.

Remark x: Don’t care

Seiko Instruments Inc.

5

5 Page

www.DataSheet4U.com

Rev.3.1_01

CMOS SERIAL E2PROM

S-93C46B/56B/66B

Operation

All instructions are executed by inputting DI in synchronization with the rising edge of SK after CS goes

high. An instruction set is input in the order of start bit, instruction, address, and data.

Instruction input finishes when CS goes low. A low level must be input to CS between commands during

tCDS. While a low level is being input to CS, the S-93C46B/56B/66B is in standby mode, so the SK and DI

inputs are invalid and no instructions are allowed.

Start Bit

A start bit is recognized when the DI pin goes high at the rise of SK after CS goes high. After CS goes high,

a start bit is not recognized even if the SK pulse is input as long as the DI pin is low.

1. Dummy clock

SK clocks input while the DI pin is low before a start bit is input are called dummy clocks. Dummy

clocks are effective when aligning the number of instruction sets (clocks) sent by the CPU with those

required for serial memory operation. For example, when a CPU instruction set is 16 bits, the number

of instruction set clocks can be adjusted by inserting a 7-bit dummy clock for the S-93C46B and a 5-bit

dummy clock for the S-93C56B/66B.

2. Start bit input failure

• When the output status of the DO pin is high during the verify period after a write operation, if a high

level is input to the DI pin at the rising edge of SK, the S-93C46B/56B/66B recognizes that a start bit

has been input. To prevent this failure, input a low level to the DI pin during the verify operation

period (refer to “4.1 Verify operation”).

• When a 3-wire interface is configured by connecting the DI input pin and DO output pin, a period in

which the data output from the CPU and the serial memory collide may be generated, preventing

successful input of the start bit. Take the measures described in “ 3-Wire Interface (Direct

Connection between DI and DO)”.

Seiko Instruments Inc.

11

11 Page | ||

| Páginas | Total 42 Páginas | |

| PDF Descargar | [ Datasheet S93C46B.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| S93C46A | CMOS SERIAL E2PROM | Seiko Instruments |

| S93C46B | (S93Cx6B) CMOS SERIAL E2PROM | Seiko Instruments |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |