|

|

PDF 8T49NS010 Data sheet ( Hoja de datos )

| Número de pieza | 8T49NS010 | |

| Descripción | Clock Synthesizer and Fanout Buffer/Divider | |

| Fabricantes | Integrated Device Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de 8T49NS010 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Clock Synthesizer

and Fanout Buffer/Divider

8T49NS010

DATA SHEET

General Description

The 8T49NS010 is a Clock Synthesizer and Fanout Buffer/Divider.

When used with an external crystal, the 8T49NS010 generates high

performance timing geared towards the communications and data-

com markets, especially for applications demanding extremely low

phase noise jitter, such as 10, 40 and 100GE.

The 8T49NS010 provides versatile frequency configurations and

output formats and is optimized to deliver excellent phase noise

performance. The device delivers an optimum combination of high

clock frequency and low phase noise performance, combined with

high power supply noise rejection.

The 8T49NS010 supports two types of output levels. FORMAT #1

Outputs provide an output level with 750mV typical swing, and

requires external DC termination. FORMAT #2 Outputs provide a

similar swing level which does not require DC termination.

The device can be configured through an I2C serial interface and is

offered in a lead-free (RoHS6) 56-pin VFQFN package.

The extended temperature range supports telecommunication and

networking end equipment requirements.

Features

• Ten differential outputs

• The input operates in full differential mode (LVDS, LVPECL) or

single-ended LVCMOS mode

• Can be driven from a crystal or differential clock

• Support of output power-down

• Excellent clock output phase noise

Offset Output Frequency Single-side Band Phase Noise

100kHz

156.25MHz

-144 dBc/Hz

• Phase Noise RMS, 12kHz to 20MHz integration range:

84fs (typical)

• LVCMOS compatible I2C serial interface

• I2C control inputs are 3.3V tolerant

• Full 3.3V supply voltage

• Lead-free (RoHS 6) 56-pin VFQFN packaging

• -40°C to 85°C ambient operating temperature

Additional Ordering Information

Part/Order Number

Package

8T49NS010-156NLGI

56-pin VFQFN

Output Frequency (MHz)

156.25, 312.5, 625, 1250

8T49NS010 REVISION 1 11/19/14

1 ©2014 Integrated Device Technology, Inc.

1 page

8T49NS010 DATA SHEET

Table 1. Pin Descriptions1 (Continued)

Number

Name

Type

46

nCLK_IN

Input

Pullup/

Pulldown

Description

Inverting differential clock input. Internal resistor bias to VDD_x/2.

47

CLK_IN

Input

Pulldown Non-inverting differential clock input.

48

VDD_I2C

Power

Power Supply Voltage for I2C.

49

REF_SEL

Input

Pulldown

Selects between XTAL and CLK. 0 select Xtal (with x2)and 1 selects CLK

input. Refer to Table 4A. LVCMOS interface levels.

50 CAP

51

VDD_XTAL

Power

52 XTAL_IN

Bypass capacitor for internal reference. Should connect cap between this

pin and VDD_I2C pin 48.

Power Supply for crystal.

Crystal oscillator interface, XTAL_IN is the input.

53 XTAL_OUT

Crystal oscillator interface, XTAL_OUT is the output.

54

VSS_XTAL

Power

Power Supply Ground for XTAL circuit. Return for pin 51

55

FB_SEL

Input

Pulldown Feedback Divider select. Refer to Table 4B. LVCMOS interface levels.

56

OUTPUT

TYPE

Input

Pulldown

Selects between FORMAT #1 or FORMAT #2 (with no DC termination)

output levels. “0” selects FORMAT #2 and “1” selects FORMAT #1 type

output structure. Refer to Table 5K. LVCMOS interface levels.

ePad

VEE_EP

Power

Negative supply. Exposed pad must be connected to ground. Return for all

outputs and core supplies Pins 3, 8, 20, 35, 40.

NOTE 1.Pulldown and Pullup refer to internal input resistors. See Table 2, Pin Characteristics, for typical values

Table 2. Input Characteristics

Symbol

Parameter

CIN Input Capacitance

RPULLDOWN Input Pulldown Resistor

RPULLUP

Input Pullup Resistor

Test Conditions

Minimum

Typical

3.5

51

51

Maximum

Units

pF

k

k

Table 3. Output Characteristics

Symbol

Parameter

ROUT

Output

Impedance

SDATA

Test Conditions

VDD_I2C = 3.3V ± 5%

Minimum

Typical

60

Maximum Units

REVISION 1 11/19/14

5 CLOCK SYNTHESIZER AND FANOUT BUFFER/DIVIDER

5 Page

8T49NS010 DATA SHEET

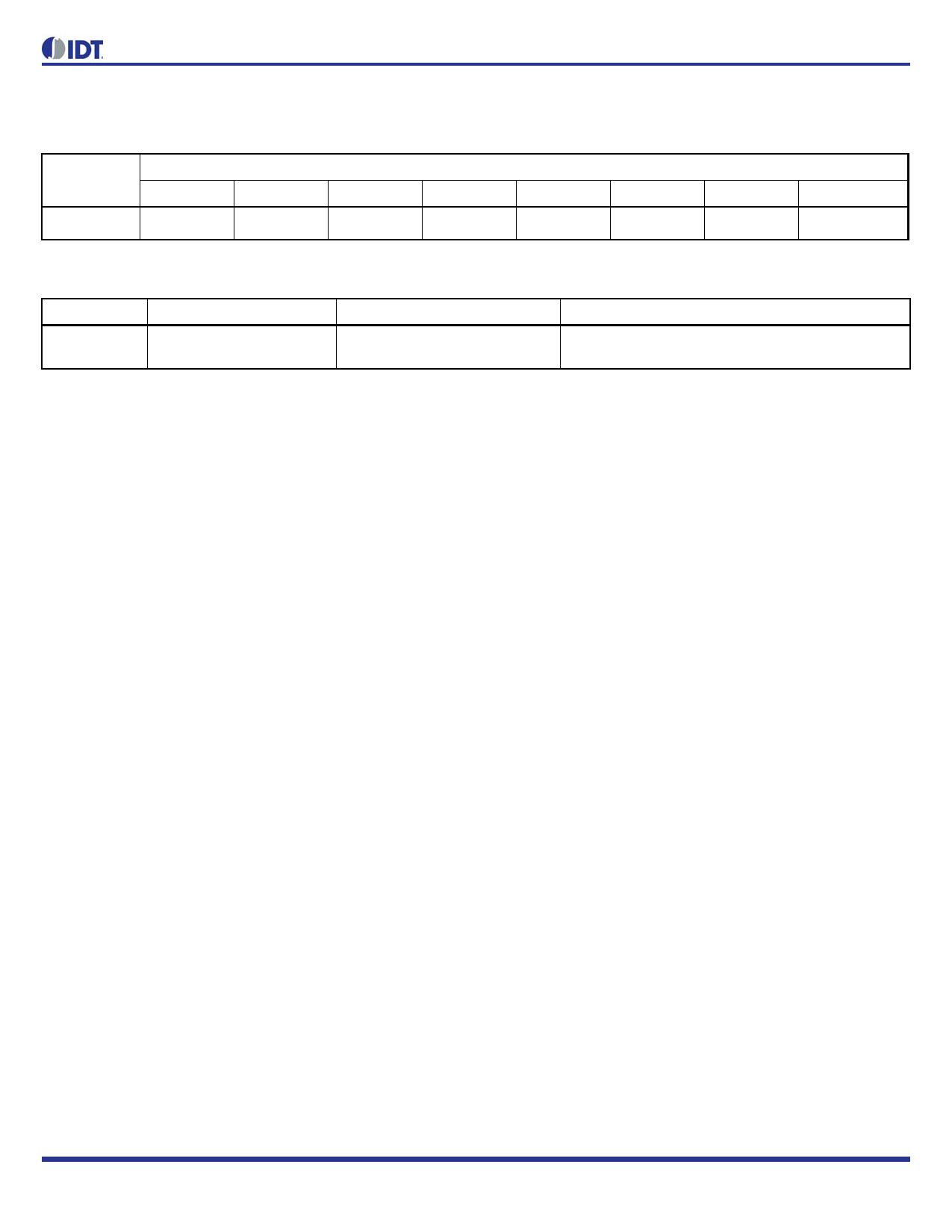

Table 5P. Programming Selection Control Register Bit Allocation

Register Bit

Register D7 D6 D5 D4 D3

27

Reserved

Reserved

Reserved

Reserved

Reserved

D2

Reserved

D1

Reserved

D0

PIN_OVERRIDE

Table 5Q. Programming Selection Control Register Function Description

Bits Name

Factory Default

Function

PIN_OVERRIDE

Programming Source

Selection

0

0 = Programming from Pins (Default)

1 = Programming from I2C Bits

REVISION 1 11/19/14

11 CLOCK SYNTHESIZER AND FANOUT BUFFER/DIVIDER

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet 8T49NS010.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 8T49NS010 | Clock Synthesizer and Fanout Buffer/Divider | Integrated Device Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |