|

|

PDF ISL94203 Data sheet ( Hoja de datos )

| Número de pieza | ISL94203 | |

| Descripción | 3-to-8 Cell Li-ion Battery Pack Monitor | |

| Fabricantes | Intersil | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ISL94203 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

DATASHEET

3-to-8 Cell Li-ion Battery Pack Monitor

ISL94203

The ISL94203 is a Li-ion battery monitor IC that supports from

3 to 8 series connected cells. It provides full battery monitoring

and pack control. The ISL94203 provides automatic shutdown

and recovery from out of bounds conditions and automatically

controls pack cell balancing.

The ISL94203 is highly configurable as a stand-alone unit, but

can be used with an external microcontroller, which

communicates to the IC through an I2C interface.

Applications

• Power tools

• Battery back-up systems

• E-bikes

Features

• Eight cell voltage monitors support Li-ion CoO2, Li-ion

Mn2O4 and Li-ion FePO4 chemistries

• Stand-alone pack control - No microcontroller needed

• Multiple voltage protection options

(Each programmable to 4.8V; 12-bit digital value)

and selectable overcurrent protection levels

• Programmable detection/recovery times for overvoltage,

undervoltage, overcurrent and short circuit conditions

• Configuration/calibration registers maintained in EEPROM

• Open battery connect detection

• Integrated charge/discharge FET drive circuitry with built-in

charge pump supports high-side N-channel FETs

• Cell balancing uses external FETs with internal state

machine or external microcontroller

• Enters low power states after periods of inactivity. Charge or

discharge current detection resumes normal scan rates

P+

43V 43V

GND

VBATT

VC8

CB8

VC7

CB7

VC6

CB6

VC5

CB5

VC4

CB4

VC3

CB3

VC2

CB2

VC1

CB1

VC0

VSS

ISL94203

PSD

FETSOFF

INT

RGO

SD

EOC

SCL

SDA

TEMPO

xT1

xT2

VREF

ADDR

FIGURE 1. TYPICAL APPLICATION DIAGRAM

CHRG

P-

August 17, 2015

FN7626.4

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774 | Copyright Intersil Americas LLC. 2012, 2015. All Rights Reserved

Intersil (and design) is a trademark owned by Intersil Corporation or one of its subsidiaries.

All other trademarks mentioned are the property of their respective owners.

1 page

ISL94203

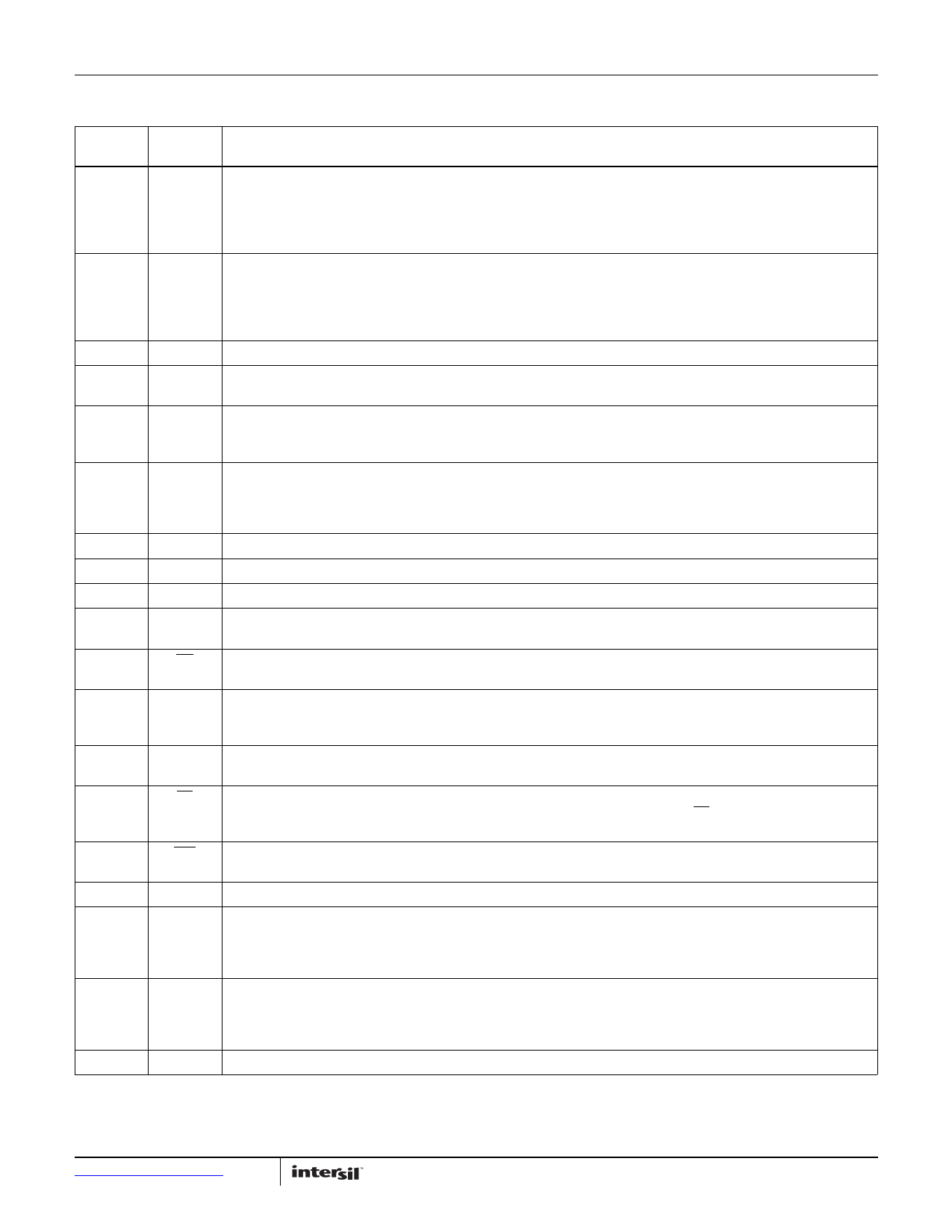

Pin Descriptions

PIN

NUMBER

SYMBOL

DESCRIPTION

1, 3, 5, 7, 9,

11, 13, 15,

17

VC8, VC7,

VC6, VC5,

VC4, VC3,

VC2, VC1,

VC0

Battery cell n voltage input. This pin is used to monitor the voltage of this battery cell. The voltage is level shifted to a ground

reference and is monitored internally by an ADC converter. VCn connects to the positive terminal of a battery cell (CELLN)

and VC(n-1) the negative terminal of CELLN (VSS connects with the negative terminal of CELL1).

2, 4, 6, 8,

10, 12, 14,

16

CB8, CB7,

CB6, CB5,

CB4, CB3,

CB2, CB1

Cell balancing FET control output n. This internal drive circuit controls an external FET used to divert a portion of the current

around a cell while the cell is being charged or adds to the current pulled from a cell during discharge in order to perform a

cell voltage balancing operation. This function is generally used to reduce the voltage on an individual cell relative to other

cells in the pack. The cell balancing FETs are turned on or off by an internal cell balance state machine or an external

controller.

18, 28, 29

VSS Ground. This pin connects to the most negative terminal in the battery string.

19 VREF Voltage Reference Output. This output provides a 1.8V reference voltage for the internal circuitry and for the external

microcontroller.

20, 21

XT1, XT2

Temperature monitor inputs. These pins input the voltage across two external thermistors used to determine the

temperature of the cells and or the power FET. When this input drops below the threshold, an external over-temperature

condition exists.

22 TEMPO Temperature monitor output control. This pin outputs a voltage to be used in a divider that consists of a fixed resistor and

a thermistor. The thermistor is located in close proximity to the cells or the power FET. The TEMPO output is connected

internally to the VREF voltage through a PMOS switch only during a measurement of the temperature, otherwise the TEMPO

output is off.

23, 30

24

25

26, 27

DNC Do Not Connect

ADDR Serial Address. This is an address input for an I2C communication link to allow for two cascaded devices on one bus.

SCL Serial Clock. This is the clock input for an I2C communication link.

SDAI, SDAO Serial Data. These are the data lines for an I2C interface. When connected together they form the standard bidirectional

interface for the I2C bus. When separated, they can use separate level shifters for a cascaded operation.

31 INT Interrupt. This pin goes active low, when there is an external µC connected to the ISL94203 and µC communication fails to

send a slave byte within a watchdog timer period. This is a CMOS type output.

32 PSD Pack Shutdown. This pin goes active high, when any cell voltage reaches the OVLO threshold (OVLO flag). Optionally, PSD is

also set if there is a voltage differential between any two cells that is greater than a specified limit (CELLF flag) or if there

is an open wire condition. This pin can be used for blowing a fuse in the pack or as an interrupt to an external µC.

33 FETSOFF FETSOFF. This input allows an external microcontroller to turn off both Power FET and CB outputs. This pin should be pulled

low when inactive.

34 SD Shutdown. This output indicates that the ISL94203 detected any failure condition that would result in the DFET turning off.

This could be undervoltage, overcurrent, over- temperature, under-temperature, etc. The SD pin also goes active if there is

any charge overcurrent condition. This is an open drain output.

35 EOC End-of-Charge. This output indicates that the ISL94203 detected a fully charged condition. This is defined by any cell voltage

exceeding an EOC voltage (as defined by an EOC value in EEPROM).

36 RGO Regulator Output. This is the 2.5V regulator output.

37 CHMON Charge Monitor. This input monitors the charger connection. When the IC is in the sleep mode, connecting this pin to the

charger wakes up the device. When the IC recovers from a charge overcurrent condition, this pin is used to monitor that the

charger is removed prior to turning on the power FETs. In a single path configuration, this pin and the LDMON pin connect

together.

38 LDMON Load Monitor. This pin monitors the load connection. When the IC is in the sleep mode, connecting this pin to a load wakes

up the device. When the IC recovers from a discharge overcurrent or short circuit condition, this pin is used to monitor that

the load is removed prior to turning on the power FETs. In a single path configuration, this pin and the CHMON pin connect

together.

39, 40, 41 C3, C2, C1 Charge Pump Capacitor Pins. These external capacitors are used for the charge pump driving the power FETs.

Submit Document Feedback

5

FN7626.4

August 17, 2015

5 Page

ISL94203

Electrical Specifications VDD = 26.4V, TA = -40°C to +85°C, unless otherwise specified. Boldface specification limits apply across

operating temperature range, -40°C to +85°C. (Continued)

PARAMETER

SYMBOL

TEST CONDITION

MIN

(Note 7)

MAX

TYP (Note 7) UNITS

OVERCURRENT/SHORT CIRCUIT PROTECTION SPECIFICATIONS

Discharge Overcurrent Detection

Threshold

Discharge Overcurrent Detection

Time

VOCD

tOCDT

VOCD = 4mV [OCD2:0] = 0,0,0

VOCD = 8mV [OCD2:0] = 0,0,1

VOCD = 16mV [OCD2:0] = 0,1,0

VOCD = 24mV [OCD2:0] = 0,1,1

VOCD = 32mV [OCD2:0] = 1,0,0 (DEFAULT)

VOCD = 48mV [OCD2:0] = 1,0,1

VOCD = 64mV [OCD2:0] = 1,1,0

VOCD = 96mV [OCD2:0] = 1,1,1

[OCDTA:OCDT0] = 0A0H (160ms) (DEFAULT)

Range:

0ms to 1023ms 1ms/step

0s to 1023s; 1s/step

2.6

6.4

12.8

20

26.4

42.5

60.3

90

4 5.4 mV

8 9.6 mV

16

19.2

mV

25 30 mV

33

39.6

mV

50 57.5 mV

67

73.7

mV

100 110 mV

160 ms

Short Circuit Detection Threshold

Short Circuit Current Detection Time

VSCD

tSCT

VSCD = 16mV [SCD2:0] = 0,0,0

VSCD = 24mV [SCD2:0] = 0,0,1

VSCD = 32mV [SCD2:0] = 0,1,0

VSCD = 48mV [SCD2:0] = 0,1,1

VSCD = 64mV [SCD2:0] = 1,0,0

VSCD = 96mV [SCD2:0] = 1,0,1 (DEFAULT)

VSCD = 128mV [SCD2:0] = 1,1,0

VSCD = 256mV [SCD2:0] = 1,1,1

[SCTA:SCT0] = 0C8H (200µs) (DEFAULT)

Range:

0µs to 1023µs; 1µs/step

0ms to 1023ms 1ms/step

10.4

18

26

42

60

90

127

249

16

21.6

mV

24 30 mV

33 40 mV

49 56 mV

67 74 mV

100 110 mV

134 141 mV

262 275 mV

200 µs

Charge Overcurrent Detection

Threshold

Overcurrent Charge Detection Time

VOCC

tOCCT

VOCC = 1mV [OCC2:0] = 0,0,0

VOCC = 2mV [OCC2:0] = 0,0,1

VOCC = 4mV [OCC2:0] = 0,1,0

VOCC = 6mV [OCC2:0] = 0,1,1

VOCC = 8mV [OCC2:0] = 1,0,0 (DEFAULT)

VOCC = 12mV [OCC2:0] = 1,0,1

VOCC = 16mV [OCC2:0] = 1,1,0

VOCC = 24mV [OCC2:0] = 1,1,1

[OCCTA:OCCT0] = 0A0H (160ms) (DEFAULT)

Range:

0ms to 1023ms 1ms/step

0s to 1023s; 1s per step

0.2

0.7

2.8

4.5

6.6

9.6

14.5

22.5

1 2.1 mV

2 3.3 mV

4 5.2 mV

6 7.5 mV

8 9.8 mV

12

14.4

mV

17

19.6

mV

25 27.5 mV

160 ms

Charge Monitor Input Threshold

(Falling Edge)

VCHMON µCCMON bit = “1”; CMON_EN bit = “1”

8.2 8.9 9.8 V

Load Monitor Input Threshold

(Rising Edge)

VLDMON µCLMON bit = “1”; LMON_EN bit = “1”

0.45

0.6

0.75

V

Load Monitor Output Current

ILDMON µCLMON bit = “1”; LMON_EN bit = “1”

62 µA

Submit Document Feedback 11

FN7626.4

August 17, 2015

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet ISL94203.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ISL94200 | Multi-Cell Li-ion Battery Pack OCP/Analog Front-End | Intersil |

| ISL94201 | Multi-Cell Li-ion Battery Pack Analog Front-End | Intersil |

| ISL94203 | 3-to-8 Cell Li-ion Battery Pack Monitor | Intersil |

| ISL94208 | 4- to 6-Cell Li-ion Battery Management Analog Front-End | Intersil |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |