|

|

PDF NB3N853531E Data sheet ( Hoja de datos )

| Número de pieza | NB3N853531E | |

| Descripción | 3.3V Xtal or LVTTL/LVCMOS Input 2:1 MUX to 1:4 LVPECL Fanout Buffer | |

| Fabricantes | ON Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de NB3N853531E (archivo pdf) en la parte inferior de esta página. Total 9 Páginas | ||

|

No Preview Available !

NB3N853531E

3.3 V Xtal or

LVTTL/LVCMOS Input 2:1

MUX to 1:4 LVPECL Fanout

Buffer

Description

The NB3N853531E is a low skew 3.3 V supply 1:4 clock

distribution fanout buffer. An input MUX selects either a

Fundamental Parallel Mode Crystal or a LVCMOS/LVTTL Clock by

using the CLK_SEL pin (HIGH for Crystal, LOW for Clock) with

LVCMOS / LVTTL levels.

The single ended CLK input is translated to four LVPECL Outputs.

Using the crystal input, the NB3N853531E can be a Clock Generator.

A CLK_EN pin can enable or disable the outputs synchronously to

eliminate runt pulses using LVCMOS/LVTTL levels (HIGH to enable

outputs, LOW to disable outputs).

Features

• Four Differential 3.3 V LVPECL Outputs

• Selectable Crystal or LVCMOS/LVTTL CLOCK Inputs

• Up to 266 MHz Clock Operation

• Output to Output Skew: 30 ps (Max)

• Device to Device Skew 200 ps (Max)

• Propagation Delay 1.8 ns (Max)

• Operating Range: VCC = 3.3 ±5% V( 3.135 to 3.465 V)

• Additive Phase Jitter, RMS: 0.053 ps (Typ)

• Synchronous Clock Enable Control

• Industrial Temp. Range (−40°C to 85°C)

• Pb−Free TSSOP−20 Package

• Ambient Operating Temperature Range −40°C to +85°C

• These are Pb−Free Devices

http://onsemi.com

MARKING

DIAGRAM

TSSOP−20

DT SUFFIX

CASE 948E

NB3N

531E

ALYWG

G

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

G = Pb−Free Package

(Note: Microdot may be in either location)

ORDERING INFORMATION

See detailed ordering and shipping information in the

package dimensions section on page 7 of this data sheet.

CLK_EN

Pullup

CLK

Pulldown

XTAL_IN

XTAL_OUT

OSC

CLK_SEL

Pulldown

0

1

D

Q

Figure 1. Simplified Logic Diagram

Q0

Q0

Q1

Q1

Q2

Q2

Q3

Q3

© Semiconductor Components Industries, LLC, 2012

March, 2012 − Rev. 6

1

Publication Order Number:

NB3N853531E/D

1 page

NB3N853531E

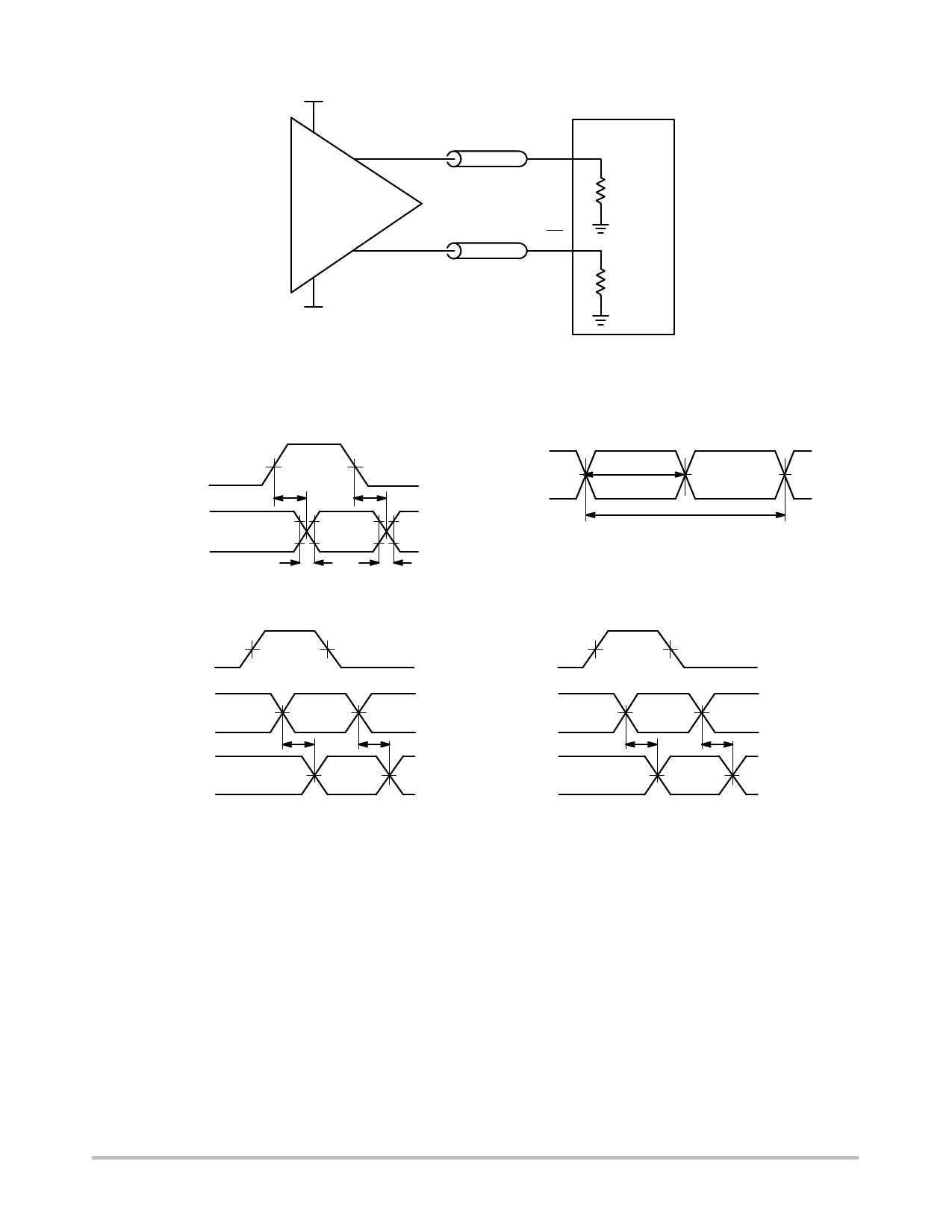

2V

VCC

LVPECL

VEE

−1.3 ± 0.165 V

Zo = 50 W

Qx

Zo = 50 W

Qx

50 W

50 W

Figure 4. Typical Test Setup and Termination for Evaluation. A split supply of VCC = 2.0 V and VEE = −1.3 +0.165 V

allows a convenient direct connection termination into typical oscilloscope 50 W to GND impedance modules.

For Application termination schemes see AND8020.

Input

Output

VCC/2

VCC/2

tPD

20%

80% 80%

tR

Propagation Delay tPD

tPD

20%

tF

Input

Output

tPW

tPeriod

tSKEWDC % + ǒtPWńtPeriodǓ

Duty Cycle Skew − tSKEWDC

100

Input

CLKx

tSKEW0−0

CLKy

tSKEW0−0

Part #1

Output

tSKEWD−D

Part #2

Output

tSKEWD−D

Output−to−Output Skew tSKEW0−0

Device−to−Device Skew, tSKEWD−D

Figure 5. AC Measurement Reference

http://onsemi.com

5

5 Page | ||

| Páginas | Total 9 Páginas | |

| PDF Descargar | [ Datasheet NB3N853531E.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| NB3N853531E | 3.3V Xtal or LVTTL/LVCMOS Input 2:1 MUX to 1:4 LVPECL Fanout Buffer | ON Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |