|

|

PDF M4A5-64 Data sheet ( Hoja de datos )

| Número de pieza | M4A5-64 | |

| Descripción | High Performance E2CMOS In-System Programmable Logic | |

| Fabricantes | Lattice Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de M4A5-64 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

ispMACH™ 4A CPLD Family

High Performance E2CMOS®

In-System Programmable Logic

FEATURES

◆ High-performance, E2CMOS 3.3-V & 5-V CPLD families

◆ Flexible architecture for rapid logic designs

— Excellent First-Time-FitTM and refit feature

— SpeedLockingTM performance for guaranteed fixed timing

— Central, input and output switch matrices for 100% routability and 100% pin-out retention

◆ High speed

— 5.0ns tPD Commercial and 7.5ns tPD Industrial

— 182MHz fCNT

◆ 32 to 512 macrocells; 32 to 768 registers

◆ 44 to 388 pins in PLCC, PQFP, TQFP, BGA, fpBGA and caBGA packages

◆ Flexible architecture for a wide range of design styles

— D/T registers and latches

— Synchronous or asynchronous mode

— Dedicated input registers

— Programmable polarity

— Reset/ preset swapping

◆ Advanced capabilities for easy system integration

— 3.3-V & 5-V JEDEC-compliant operations

— JTAG (IEEE 1149.1) compliant for boundary scan testing

— 3.3-V & 5-V JTAG in-system programming

— PCI compliant (-5/-55/-6/-65/-7/-10/-12 speed grades)

— Safe for mixed supply voltage system designs

— Programmable pull-up or Bus-FriendlyTM inputs and I/Os

— Hot-socketing

— Programmable security bit

— Individual output slew rate control

◆ Advanced E2CMOS process provides high-performance, cost-effective solutions

◆ Lead-free package options

Lead-

Free

Package

Options

Available!

Publication# ISPM4A Rev: M

Amendment/0

Issue Date: September 2006

1 page

FUNCTIONAL DESCRIPTION

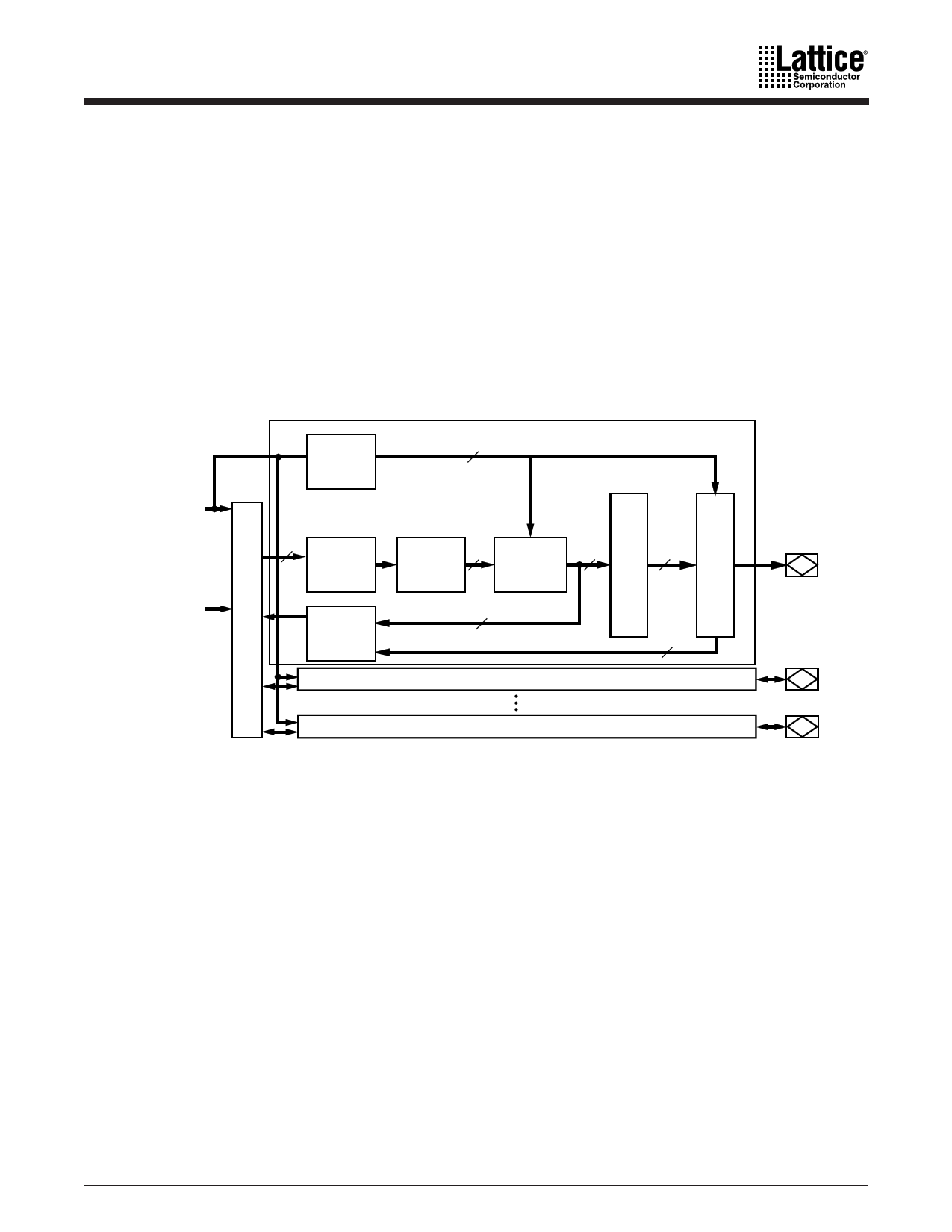

The fundamental architecture of ispMACH 4A devices (Figure 1) consists of multiple, optimized PAL®

blocks interconnected by a central switch matrix. The central switch matrix allows communication between

PAL blocks and routes inputs to the PAL blocks. Together, the PAL blocks and central switch matrix allow

the logic designer to create large designs in a single device instead of having to use multiple devices.

The key to being able to make effective use of these devices lies in the interconnect schemes. In the

ispMACH 4A architecture, the macrocells are flexibly coupled to the product terms through the logic

allocator, and the I/O pins are flexibly coupled to the macrocells due to the output switch matrix. In

addition, more input routing options are provided by the input switch matrix. These resources provide the

flexibility needed to fit designs efficiently.

Clock/Input

Pins

Note 3

Dedicated

Input Pins

Clock

Generator

4

Note 2

PAL Block

33/

34/

36

Logic

Array

Input

Switch

Matrix

Logic 16 Output/ 16

Allocator

Buried

with XOR

Macrocells

16

PAL Block

8

Note 1

16

I/O

Pins

I/O

Pins

PAL Block

Figure 1. ispMACH 4A Block Diagram and PAL Block Structure

I/O

Pins

17466G-001

Notes:

1. 16 for ispMACH 4A devices with 1:1 macrocell-I/O cell ratio (see next page).

2. Block clocks do not go to I/O cells in M4A(3,5)-32/32.

3. M4A(3,5)-192, M4A(3,5)-256, M4A3-384, and M4A3-512 have dedicated clock pins which cannot be used as inputs and do not connect to the central switch

matrix.

ispMACH 4A Family

5

5 Page

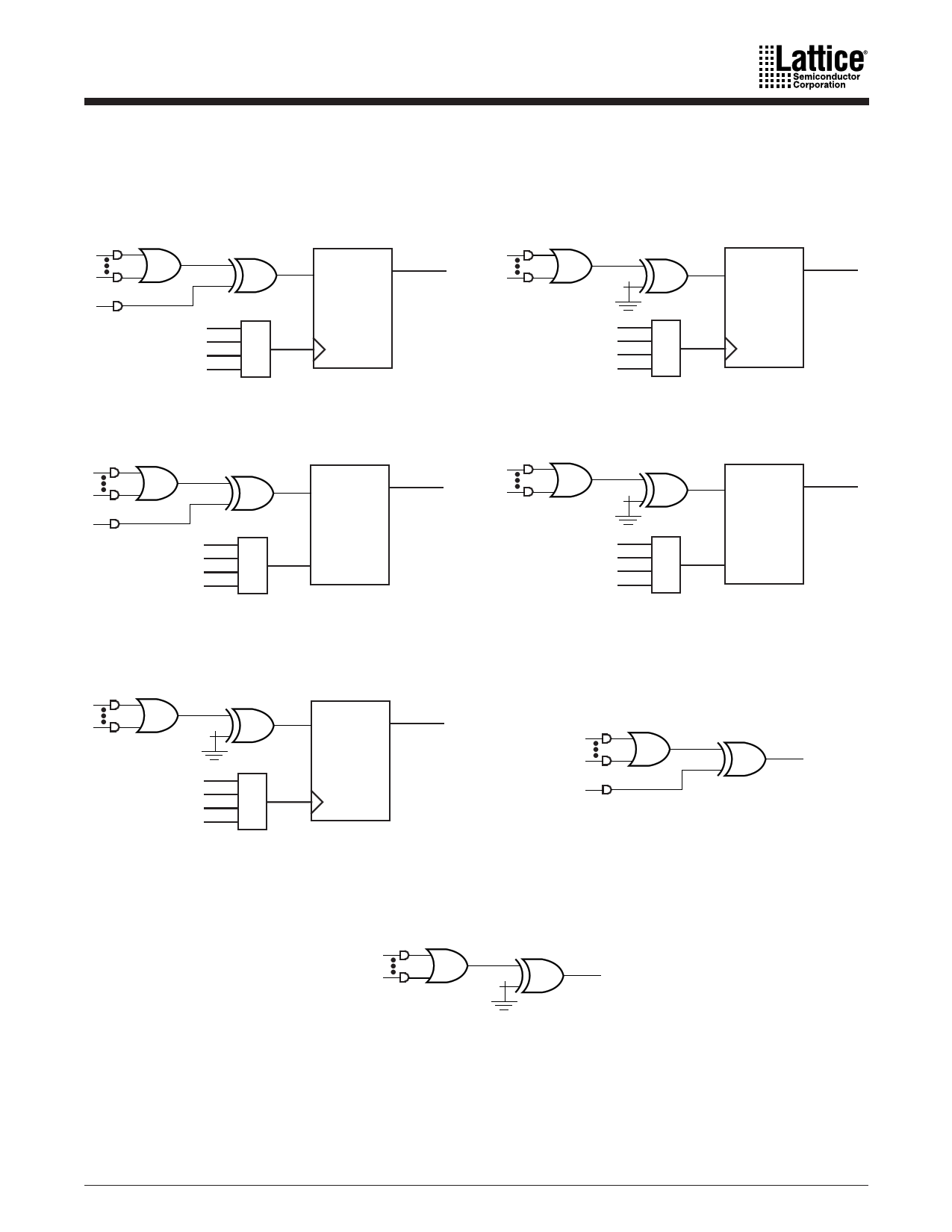

The flip-flop can be configured as a D-type or T-type latch. J-K or S-R registers can be synthesized. The

primary flip-flop configurations are shown in Figure 6, although others are possible. Flip-flop functionality

is defined in Table 8. Note that a J-K latch is inadvisable as it will cause oscillation if both J and K inputs

are HIGH.

AP AR

DQ

AP AR

DQ

a. D-type with XOR

AP AR

LQ

G

c. Latch with XOR

AP AR

TQ

e. T-type with programmable T polarity

b. D-type with programmable D polarity

AP AR

LQ

G

d. Latch with programmable D polarity

f. Combinatorial with XOR

g. Combinatorial with programmable polarity

Figure 6. Primary Macrocell Configurations

ispMACH 4A Family

17466G-011

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet M4A5-64.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| M4A5-64 | High Performance E2CMOS In-System Programmable Logic | Lattice Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |