|

|

PDF HI-3110 Data sheet ( Hoja de datos )

| Número de pieza | HI-3110 | |

| Descripción | Avionics CAN Controller | |

| Fabricantes | Holt Integrated Circuits | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de HI-3110 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

HI-3110, HI-3111, HI-3112, HI-3113

May 2016

Avionics CAN Controller

with Integrated Transceiver

GENERAL DESCRIPTION

The HI-3110 is a standalone Controller Area Network

(CAN) controller with built in transceiver. The device

provides a complete, integrated, cost-effective solution for

avionics applications implementing the CAN 2.0B

specification and can be configured to comply with both the

ARINC 825 (General Standardization of CAN Bus Protocol

for Airborne Use) and CANaerospace standards. The HI-

3110 is capable of transmitting and receiving standard

data frames, extended data frames and remote frames.

The internal transceiver allows direct connection to the

CAN bus without using external components and coupled

with the host Serial Peripheral Interface (SPI), results in

minimal board space.

The HI-3110 provides the optimum solution for

applications where minimum host (MCU) overhead is

required, filtering unwanted messages using a maskable

identifier filter and storing up to 8 messages in the receive

FIFO. A flexible interrupt scheme allows real time

servicing of the FIFO by the host, if required.

Transmissions are handled using an 8 message transmit

FIFO. A Transmit Enable pin can be used by the host to

initiate a transmission. The device also provides monitor

or listen-only mode, low power sleep mode, loopback

mode for self-test and a re-transmission disable capability

(necessary to implement TTCAN protocol).

The HI-3111 is a digital only version of the HI-3110 (no

transceiver). This version provides a “protocol only”

solution for customers who wish to use an external

transceiver and may be used in situations where the

customer requires galvanic isolation between the bus and

digital protocol logic. The HI-3112 provides an option of a

CLKOUT pin instead of a SPLIT pin, which may be used as

the main system clock or as a clock input for other devices

in the system. Finally, the HI-3113 provides all options

(both CLKOUT and SPLIT pins) in a very compact QFN-44

package.

The HI-3110 family is available in industrial and full

extended temperature ranges, with a “RoHS compliant”

lead-free option. The design has been independently

validated by C&S group, GmbH, an ISO/IEC 17025

accredited test house. A copy of the test report is available

from Holt on request.

FEATURES

· Implements CAN version 2.0B with programmable bit

rate up to 1Mbit/sec. ISO 11898-5 compliant.

· Configurable to support ARINC 825 and

CANaerospace Standards.

· Serial Peripheral Interface (SPI) (20MHz).

· Standard, Extended and Remote frames supported.

· 8 maskable identifier filters.

· Filtering on ID and first two data bytes for both

Standard and Extended Identifiers.

· Loopback mode for self-test.

· Monitor (Listen-only) and Low Power Sleep Modes

with automatic wake-up possible.

· 8-message Transmit and Receive FIFOs.

· Internal 16-bit free running counter for time tagging of

transmitted or received messages.

· Permanent dominant timeout protection.

· Short Circuit Protection of -58V to + 58V on CAN_H,

CAN_L and SPLIT pins (ISO 11898-5).

· Re-transmission disable capability.

· Transmit Enable pin.

· Industrial and Full Extended temperature ranges

supported:

Industrial: -40oC to + 85oC.

Extended: -55oC to + 125oC.

PIN CONFIGURATION (Top View)

VLOGIC 1

OSCOUT 2

OSCIN 3

GP1 4

GP2 5

TXEN 6

SPLIT 7

GND 8

CANL 9

3110PSI

3110PST

3110PSM

18 INT

17 MR

16 CS

15 SO

14 SI

13 SCK

12 STAT

11 VDD

10 CANH

18-Pin Plastic SOIC - WB Package

(DS3110 Rev. J)

HOLT INTEGRATED CIRCUITS

www.holtic.com

05/16

1 page

HI-3110, HI-3111, HI-3112, HI-3113

from 5V and the line driver is capable of maintaining a

detectable signal for bus lengths well in excess of

recommended CAN 2.0B standards. The digital logic and IO

can be powered from 3.3V or 5V.

PROTECTION FEATURES

The BUS and SPLIT pins are protected against ESD to over

4KV (HBM) and from shorts between -58V to +58V

continuous, as specified in ISO 11898-5.

In addition, a Permanent Dominant Timeout protection is

implemented by means of an independent counter

monitoring the dominant transmission state and

automatically shutting off the transmission if it exceeds

typically 2ms.

MODES OF OPERATION

The HI-3110 supports five modes of operation, namely,

Initialization Mode, Normal Mode, Loopback Mode, Monitor

Mode and Sleep Mode.

INITIALIZATION MODE

Initialization mode is used to configure the device before

normal operation. Bit timing registers and acceptance

filters and masks can only be modified in this mode.

Initialization mode is the default mode following RESET and

can also be activated by programming the MODE<2:0> bits

to <1xx> in the CTRL0 register. Switching to Initialization

mode resets the receiver and transmitter. During

initialization mode, the error counters are held reset.

NORMAL MODE

Normal mode is the standard operating mode of the HI-3110.

In this mode, the HI-3110 can transmit, receive and

acknowledge messages from the CAN bus, handling all

aspects of the CAN protocol. Normal mode is activated by

programming the MODE<2:0> bits to <000> in the CTRL0

register.

MONITOR MODE

Monitor mode (also known as listen-only or silent mode)

allows the HI-3110 to monitor all bus activity without

disturbing the bus. No messages or dominant bits (such as

ACK or active error frame bits) are transmitted to the bus

while in this mode. Also, the error counters are reset and

deactivated. Messages from the bus are received in the

same way as Normal Mode and messages that are not

acknowledged by another node on the bus are ignored i.e.

any frame containing an error will be ignored. Acceptance

filters can be set up to reject or accept specific messages

into the FIFO and all interrupt flags are set as required in the

usual way. Monitor mode is activated by programming the

MODE<2:0> bits to <010> in the CTRL0 register.

SLEEP MODE

The HI-3110 can be placed in a low power sleep mode if

there is no bus activity and the transmit FIFO is empty. In

this mode, the internal oscillator and all analog circuitry

(transceiver) are off, drawing typically less than 20mA. Note

that the SPI bus is active during sleep mode, so it is possible

for the host to communicate with the HI-3110 while it is

asleep (e.g. load transmit FIFO). Sleep mode is exited by

selecting an alternative mode of operation, or automatic

wake up following bus activity can be enabled by setting the

WAKEUP bit in the CTRL0 register - in this case a low power

receiver monitors the bus for a detectable dominant bit..

The device will wake up in Monitor Mode. Note that it will

take a finite time for the oscillator and analog circuitry to

come back on line. Since the internal oscillator takes a finite

time to wake up, the message which caused the wake-up

may not be stored.

Sleep mode is activated by programming the MODE<2:0>

bits to <011> in the CTRL0 register. However, the actual

mode change will only occur whenever the CAN bus is quiet.

If the chip is transmitting, the mode change is delayed until

the transmission is complete. If there is bus activity, the

mode change is delayed until the receiver protocol control

detects an inter-message gap.

LOOPBACK MODE

CAN PROTOCOL OVERVIEW

Loopback mode is used for self-test. The transceiver digital

input is fed back to the receiver without being transmitted to

the bus. Messages are transmitted from the transmit FIFO

in the usual way and received by the receive FIFO as if they

were received from a remote node on the bus.

The HI-3110 supports Standard, Extended and Remote

Frames, as defined in the CAN specification IS0 11898-

1:2003(E) (also known as CAN 2.0B).

BIT ENCODING

Acceptance filters can be set up to accept or reject specific

messages into the FIFO and all interrupt flags are set as

required in the usual way. While in this mode, any bus

activity is ignored. Loopback is activated by programming

the MODE<2:0> bits to <001> in the CTRL0 register.

CAN frames are encoded according to the Non-Return-To-

Zero (NRZ) method with bit stuffing. NRZ means that the

generated bit level is constant during the total bit time and

consecutive bits do not return to a neutral or rest condition.

HOLT INTEGRATED CIRCUITS

5

5 Page

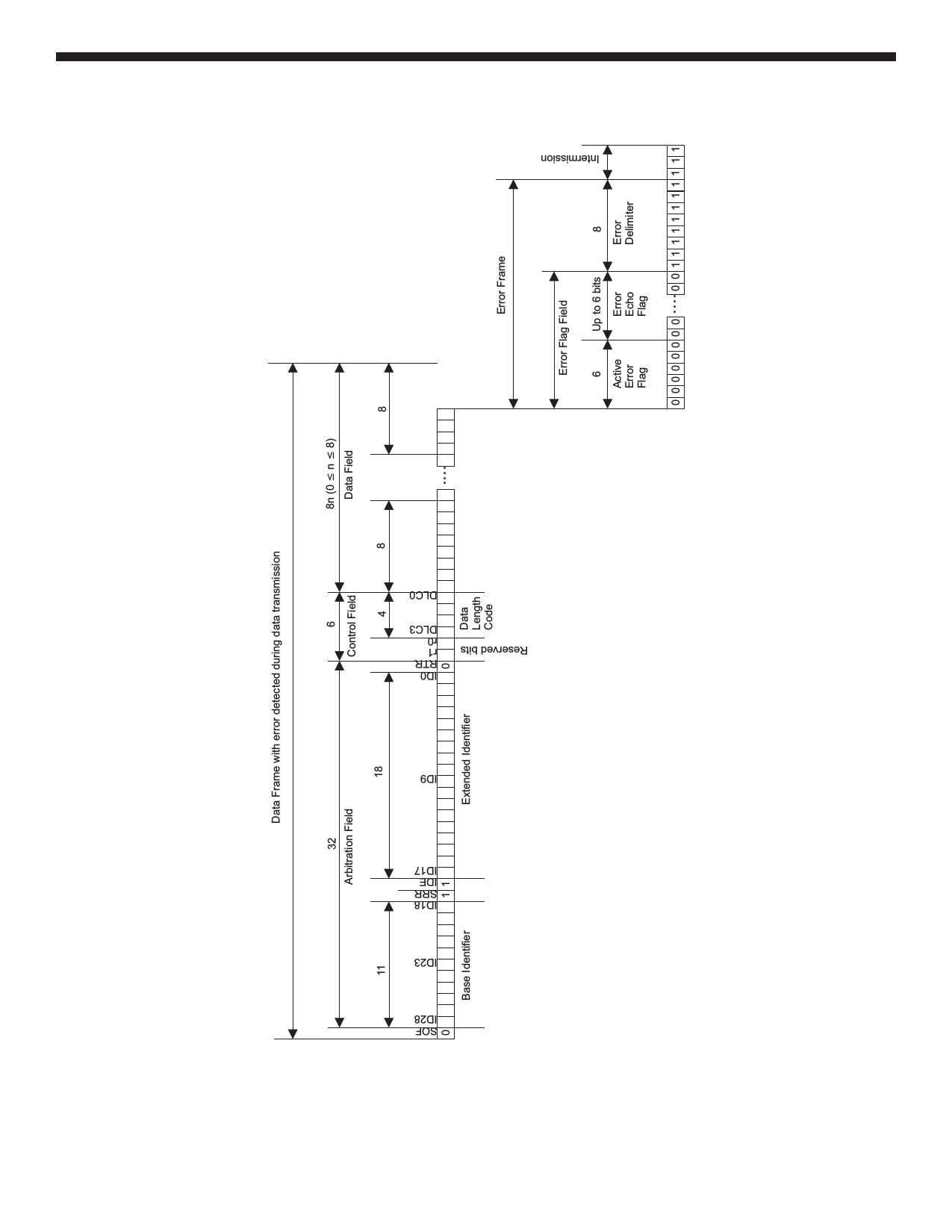

Error Frame

HI-3110, HI-3111, HI-3112, HI-3113

Figure 5. Error Frame Format.

HOLT INTEGRATED CIRCUITS

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet HI-3110.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HI-3110 | Avionics CAN Controller | Holt Integrated Circuits |

| HI-3111 | Avionics CAN Controller | Holt Integrated Circuits |

| HI-3112 | Avionics CAN Controller | Holt Integrated Circuits |

| HI-3113 | Avionics CAN Controller | Holt Integrated Circuits |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |