|

|

PDF HCTS75MS Data sheet ( Hoja de datos )

| Número de pieza | HCTS75MS | |

| Descripción | Radiation Hardened Dual 2-Bit Bistable Transparent Latch | |

| Fabricantes | Intersil Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de HCTS75MS (archivo pdf) en la parte inferior de esta página. Total 9 Páginas | ||

|

No Preview Available !

HCTS75MS

September 1995

Radiation Hardened

Dual 2-Bit Bistable Transparent Latch

Features

• 3 Micron Radiation Hardened SOS CMOS

• Total Dose 200K RAD (Si)

• SEP Effective LET No Upsets: >100 MEV-cm2/mg

• Single Event Upset (SEU) Immunity < 2 x 10-9 Errors/Bit-Day

(Typ)

• Dose Rate Survivability: >1 x 1012 RAD (Si)/s

• Dose Rate Upset >1010 RAD (Si)/s 20ns Pulse

• Latch-Up Free Under Any Conditions

• Military Temperature Range: -55oC to +125oC

• Significant Power Reduction Compared to LSTTL ICs

• DC Operating Voltage Range: 4.5V to 5.5V

• LSTTL Input Compatibility

- VIL = 0.8V Max

- VIH = VCC/2 Min

• Input Current Levels Ii ≤ 5µA at VOL, VOH

Description

The Intersil HCTS75MS is a Radiation Hardened dual 2-bit

bistable transparent latch. Each of the two latches are controlled

by a separate enable input (E) which are active low. E low latches

the output state.

The HCTS75MS utilizes advanced CMOS/SOS technology to

achieve high-speed operation. This device is a member of radia-

tion hardened, high-speed, CMOS/SOS Logic Family.

The HCTS75MS is supplied in a 16 lead Ceramic flatpack

(K suffix) or a SBDIP Package (D suffix).

Ordering Information

PART

NUMBER

HCTS75DMSR

HCTS75KMSR

HCTS75D/

Sample

HCTS75K/

Sample

HCTS75HMSR

TEMPERATURE SCREENING

RANGE

LEVEL

PACKAGE

-55oC to +125oC Intersil Class

S Equivalent

16 Lead SBDIP

-55oC to +125oC Intersil Class 16 Lead Ceramic

S Equivalent Flatpack

+25oC

Sample

16 Lead SBDIP

+25oC

+25oC

Sample

Die

16 Lead Ceramic

Flatpack

Die

Pinouts

16 LEAD CERAMIC DUAL-IN-LINE

METAL SEAL PACKAGE (SBDIP)

MIL-STD-1835 CDIP2-T16, LEAD FINISH C

TOP VIEW

Q0 1 1

D0 1 2

D1 1 3

E2 4

VCC 5

D0 2 6

D1 2 7

Q1 2 8

16 1 Q0

15 1 Q1

14 1 Q1

13 1 E

12 GND

11 2 Q0

10 2 Q0

9 2 Q1

16 LEAD CERAMIC METAL SEAL FLATPACK PACKAGE

(FLATPACK) MIL-STD-1835 CDFP4-F16, LEAD FINISH C

TOP VIEW

Q0 1

D0 1

D1 1

E2

VCC

D0 2

D1 2

Q1 2

1 16

2 15

3 14

4 13

5 12

6 11

7 10

89

1 Q0

1 Q1

1 Q1

1E

GND

2 Q0

2 Q0

2 Q1

Functional Diagram

2(6)

D0

13(4)

E

LATCH 0

DQ

LE LE

16(10

1(11

14(8

3(7)

D1

5 VCC

12 GND

LE LE

DQ

LATCH 1

TRUTH TABLE

15(9

INPUTS

DE

LH

HH

XL

OUTPUTS

QQ

LH

HL

Q0 Q0

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207 | Copyright © Intersil Corporation 1999

470

Spec Number 518625

File Number 3189.1

1 page

Specifications HCTS75MS

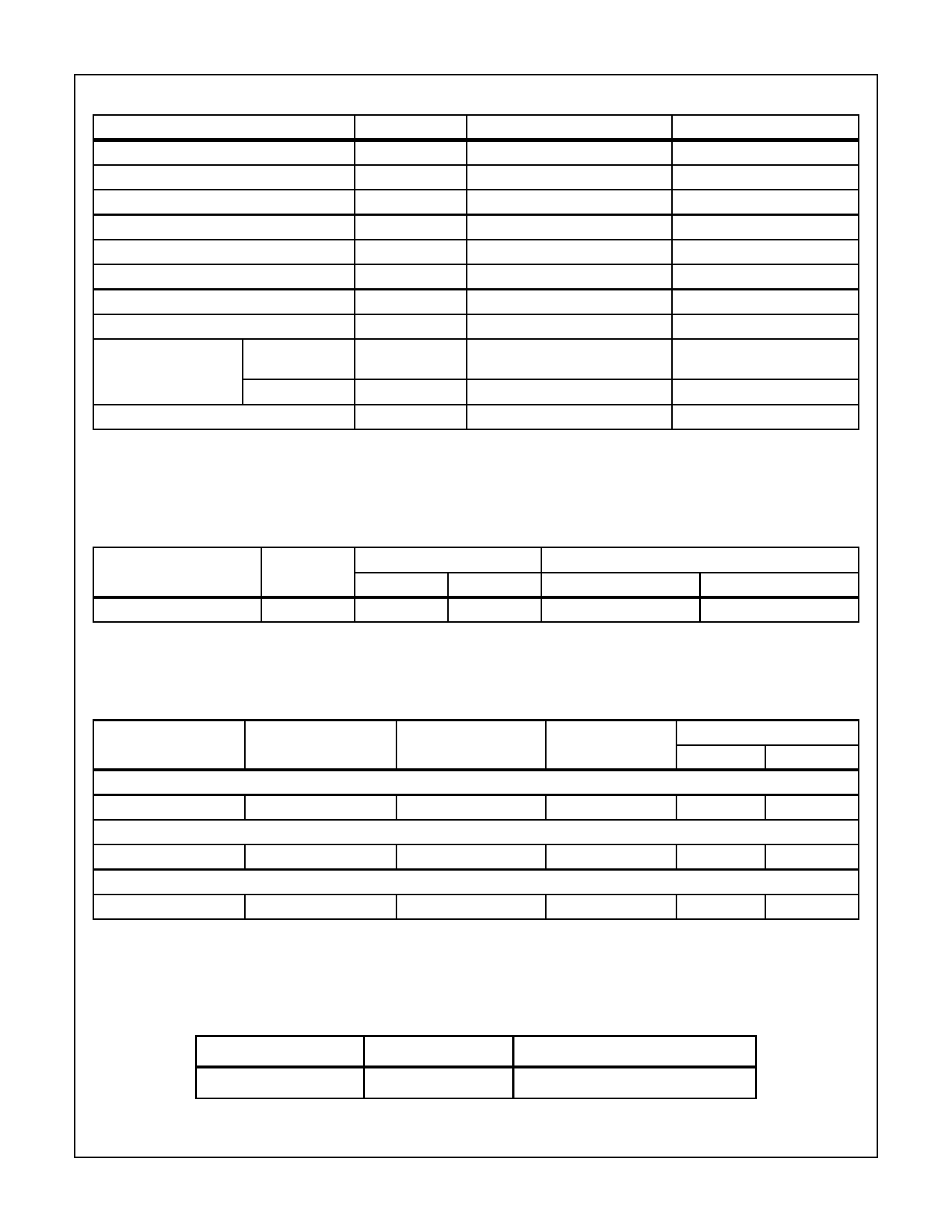

TABLE 6. APPLICABLE SUBGROUPS

CONFORMANCE GROUPS

Initial Test (Preburn-In)

Interim Test I (Postburn-In)

Interim Test II (Postburn-In)

PDA

Interim Test III (Postburn-In)

PDA

Final Test

Group A (Note 1)

Group B

Subgroup B-5

METHOD

100%/5004

100%/5004

100%/5004

100%/5004

100%/5004

100%/5004

100%/5004

Sample/5005

Sample/5005

GROUP A SUBGROUPS

1, 7, 9

1, 7, 9

1, 7, 9

1, 7, 9, Deltas

1, 7, 9

1, 7, 9, Deltas

2, 3, 8A, 8B, 10, 11

1, 2, 3, 7, 8A, 8B, 9, 10, 11

1, 2, 3, 7, 8A, 8B, 9, 10, 11, Deltas

Subgroup B-6

Sample/5005

1, 7, 9

Group D

Sample/5005

1, 7, 9

NOTES:

1. Alternate group A inspection in accordance with method 5005 of MIL-STD-883 may be exercised.

2. Table 5 parameters only.

READ AND RECORD

ICC, IOL/H

ICC, IOL/H

ICC, IOL/H

ICC, IOL/H

Subgroups 1, 2, 3, 9, 10, 11,

(Note 2)

TABLE 7. TOTAL DOSE IRRADIATION

CONFORMANCE

GROUPS

METHOD

TEST

PRE RAD

POST RAD

Group E Subgroup 2

5005

1, 7, 9

Table 4

NOTE:

1. Except FN test which will be performed 100% Go/No-Go.

READ AND RECORD

PRE RAD

POST RAD

1, 9 Table 4 (Note 1)

TABLE 8. STATIC AND DYNAMIC BURN-IN TEST CONNECTIONS

OPEN

GROUND

1/2 VCC = 3V ± 0.5V

VCC = 6V ± 0.5V

STATIC BURN-IN I TEST CONNECTIONS (Note 1)

1, 8, 9, 10, 11, 14, 15, 16

2, 3, 4, 6, 7, 12, 13

-

5

STATIC BURN-IN II TEST CONNECTIONS (Note 1)

1, 8, 9, 10, 11, 14, 15, 16

12

- 2, 3, 4, 5, 6, 7, 13

DYNAMIC BURN-IN TEST CONNECTIONS (Note 2)

-

12

1, 8, 9, 10, 11, 14, 15, 16

5

NOTES:

1. Each pin except VCC and GND will have a resistor of 10KΩ ± 5% for static burn-in

2. Each pin except VCC and GND will have a resistor of 1KΩ ± 5% for dynamic burn-in

OSCILLATOR

50kHz

25kHz

--

--

4, 13

2, 3, 6, 7

TABLE 9. IRRADIATION TEST CONNECTIONS

OPEN

GROUND

VCC = 5V ± 0.5V

1, 8, 9, 14, 15, 16

12

2, 3, 4, 5, 6, 7, 10, 11, 13

NOTE: Each pin except VCC and GND will have a resistor of 47KΩ ± 5% for irradiation testing. Group

E, Subgroup 2, sample size is 4 dice/wafer 0 failures.

Spec Number 518625

474

5 Page | ||

| Páginas | Total 9 Páginas | |

| PDF Descargar | [ Datasheet HCTS75MS.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HCTS75MS | Radiation Hardened Dual 2-Bit Bistable Transparent Latch | Intersil Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |