|

|

PDF MBM29LV800TA-90 Data sheet ( Hoja de datos )

| Número de pieza | MBM29LV800TA-90 | |

| Descripción | 8M (1M X 8/512K X 16) BIT FLASH MEMORY | |

| Fabricantes | Fujitsu | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de MBM29LV800TA-90 (archivo pdf) en la parte inferior de esta página. Total 59 Páginas | ||

|

No Preview Available !

FUJITSU SEMICONDUCTOR

DATA SHEET

DS05-20845-4E

FLASH MEMORY

CMOS

8M (1M × 8/512K × 16) BIT

MBM29LV800TA-70/90/-12/MBM29LV800BA-70/-90/-12

s FEATURES

• Single 3.0 V read, program, and erase

Minimizes system level power requirements

• Compatible with JEDEC-standard commands

Uses same software commands as E2PROMs

• Compatible with JEDEC-standard world-wide pinouts

48-pin TSOP(I) (Package suffix: PFTN – Normal Bend Type, PFTR – Reversed Bend Type)

44-pin SOP (Package suffix: PF)

48-ball FBGA (Package suffix: PBT)

• Minimum 100,000 program/erase cycles

• High performance

70 ns maximum access time

• Sector erase architecture

One 8K word, two 4K words, one 16K word, and fifteen 32K words sectors in word mode

One 16K byte, two 8K bytes, one 32K byte, and fifteen 64K bytes sectors in byte mode

Any combination of sectors can be concurrently erased. Also supports full chip erase

• Boot Code Sector Architecture

T = Top sector

B = Bottom sector

• Embedded EraseTM Algorithms

Automatically pre-programs and erases the chip or any sector

• Embedded ProgramTM Algorithms

Automatically writes and verifies data at specified address

• Data Polling and Toggle Bit feature for detection of program or erase cycle completion

• Ready/Busy output (RY/BY)

Hardware method for detection of program or erase cycle completion

• Automatic sleep mode

When addresses remain stable, automatically switch themselves to low power mode

• Low VCC write inhibit ≤ 2.5 V

• Erase Suspend/Resume

Suspends the erase operation to allow a read in another sector within the same device

(Continued)

Embedded EraseTM and Embedded ProgramTM are trademarks of Advanced Micro Devices, Inc.

1 page

MBM29LV800TA-70/-90/-12/MBM29LV800BA-70/-90/-12

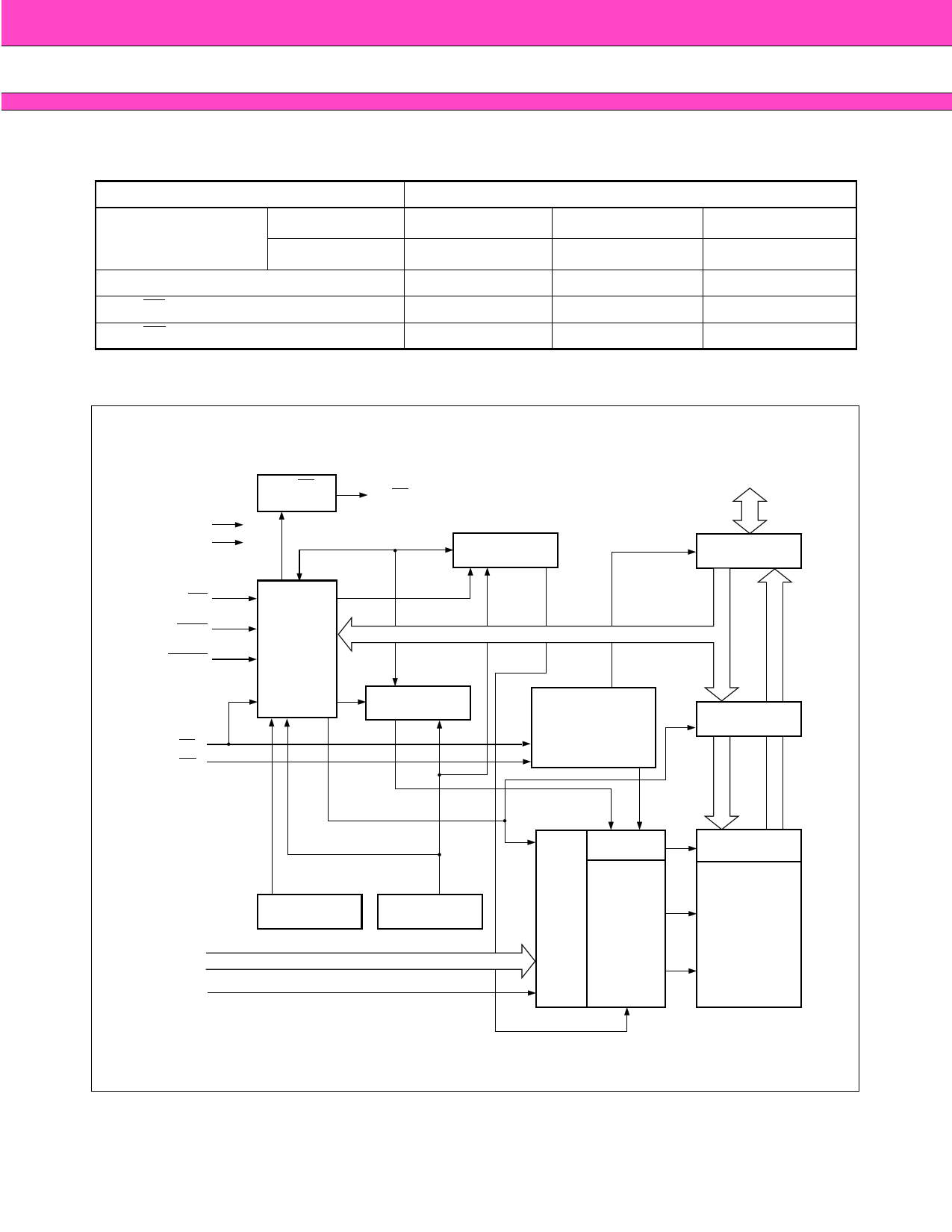

s PRODUCT LINE UP

Part No.

Ordering Part No.

VCC = 3.3 V

+0.3 V

–0.3 V

VCC = 3.0 V

+0.6 V

–0.3 V

Max. Address Access Time (ns)

Max. CE Access Time (ns)

Max. OE Access Time (ns)

s BLOCK DIAGRAM

MBM29LV800TA/MBM29LV800BA

-70 —

—

— -90 -12

70 90 120

70 90 120

30 35

50

V CC

V SS

WE

BYTE

RESET

CE

OE

RY/BY

Buffer

RY/BY

Erase Voltage

Generator

DQ 0 to DQ 15

Input/Output

Buffers

State

Control

Command

Register

Program Voltage

Generator

Chip Enable

Output Enable

Logic

STB Data Latch

A0 to A18

A-1

STB Y-Decoder

Low V CC Detector

Timer for

Program/Erase

Address

Latch

X-Decoder

Y-Gating

Cell Matrix

5

5 Page

MBM29LV800TA-70/-90/-12/MBM29LV800BA-70/-90/-12

s FUNCTIONAL DESCRIPTION

Read Mode

The MBM29LV800TA/BA have two control functions which must be satisfied in order to obtain data at the outputs.

CE is the power control and should be used for a device selection. OE is the output control and should be used

to gate data to the output pins if a device is selected.

Address access time (tACC) is equal to the delay from stable addresses to valid output data. The chip enable

access time (tCE) is the delay from stable addresses and stable CE to valid data at the output pins. The output

enable access time is the delay from the falling edge of OE to valid data at the output pins. (Assuming the

addresses have been stable for at least tACC-tOE time.) When reading out a data without changing addresses after

power-up, it is necessary to input hardware reset or change CE pin from “H” or “L”

Standby Mode

There are two ways to implement the standby mode on the MBM29LV800TA/BA devices, one using both the CE

and RESET pins; the other via the RESET pin only.

When using both pins, a CMOS standby mode is achieved with CE and RESET inputs both held at VCC ± 0.3 V.

Under this condition the current consumed is less than 5 µA. The device can be read with standard access time

(tCE) from either of these standby modes. During Embedded Algorithm operation, VCC active current (ICC2) is

required even CE = “H”.

When using the RESET pin only, a CMOS standby mode is achieved with RESET input held at VSS ± 0.3 V

(CE = “H” or “L”). Under this condition the current is consumed is less than 5 µA. Once the RESET pin is taken

high, the device requires tRH of wake up time before outputs are valid for read access.

In the standby mode the outputs are in the high impedance state, independent of the OE input.

Automatic Sleep Mode

There is a function called automatic sleep mode to restrain power consumption during read-out of

MBM29LV800TA/800BA data. This mode can be used effectively with an application requested low power

consumption such as handy terminals.

To activate this mode, MBM29LV800TA/800BA automatically switch themselves to low power mode when

MBM29LV800TA/800BA addresses remain stably during access fine of 150 ns. It is not necessary to control CE,

WE, and OE on the mode. Under the mode, the current consumed is typically 1 µA (CMOS Level).

Since the data are latched during this mode, the data are read-out continuously. If the addresses are changed,

the mode is canceled automatically and MBM29LV800TA/800BA read-out the data for changed addresses.

Output Disable

With the OE input at a logic high level (VIH), output from the devices are disabled. This will cause the output pins

to be in a high impedance state.

Autoselect

The autoselect mode allows the reading out of a binary code from the devices and will identify its manufacturer

and type. This mode is intended for use by programming equipment for the purpose of automatically matching

the devices to be programmed with its corresponding programming algorithm. This mode is functional over the

entire temperature range of the devices.

To activate this mode, the programming equipment must force VID (11.5 V to 12.5 V) on address pin A9. Two

identifier bytes may then be sequenced from the devices outputs by toggling address A0 from VIL to VIH. All

addresses are DON’T CARES except A0, A1, A6, and A-1. (See Table 4.1.)

11

11 Page | ||

| Páginas | Total 59 Páginas | |

| PDF Descargar | [ Datasheet MBM29LV800TA-90.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| MBM29LV800TA-90 | 8M (1M X 8/512K X 16) BIT FLASH MEMORY | Fujitsu |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |