No Preview Available !

Not recommended for new designs –

Please use 25AA080A/B or 25LC080A/B.

25AA080/25LC080/25C080

8K SPI Bus Serial EEPROM

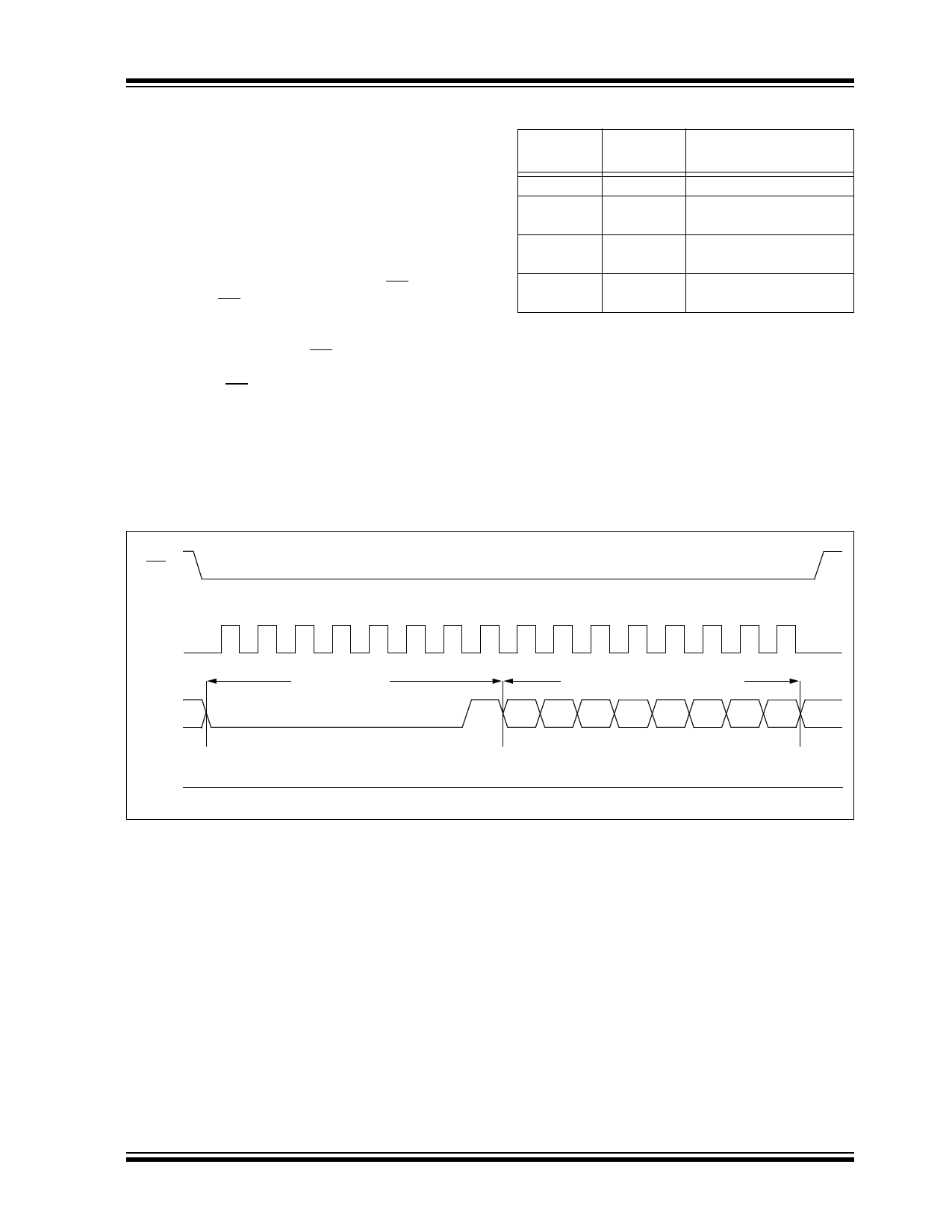

Device Selection Table

Part

Number

25AA080

25LC080

25C080

VCC

Range

1.8-5.5V

2.5-5.5V

4.5-5.5V

Max. Clock

Frequency

1 MHz

2 MHz

3 MHz

Temp.

Ranges

I

I

I,E

Features:

• Low-power CMOS technology:

- Write current: 3 mA maximum

- Read current: 500 A typical

- Standby current: 500 nA typical

• 1024 x 8-bit organization

• 16 byte page

• Write cycle time: 5 ms max.

• Self-timed erase and write cycles

• Block write protection:

- Protect none, 1/4, 1/2 or all of array

• Built-in write protection:

- Power-on/off data protection circuitry

- Write enable latch

- Write-protect pin

• Sequential read

• High reliability:

- Endurance: 1 M cycles

- Data retention: > 200 years

- ESD protection: > 4000V

• 8-pin PDIP and SOIC (150 mil)

• Temperature ranges supported:

- Industrial (I):

-40C to +85C

- Automotive (E) (25C080): -40°C to +125°C

Description:

The Microchip Technology Inc. 25AA080/25LC080/

25C080 (25XX080*) are 8 Kbit Serial Electrically

Erasable PROMs. The memory is accessed via a

simple Serial Peripheral Interface (SPI) compatible

serial bus. The bus signals required are a clock input

(SCK) plus separate data in (SI) and data out (SO)

lines. Access to the device is controlled through a Chip

Select (CS) input.

Communication to the device can be paused via the

hold pin (HOLD). While the device is paused, transi-

tions on its inputs will be ignored, with the exception of

chip select, allowing the host to service higher priority

interrupts.

Package Types

PDIP/SOIC

CS 1

SO 2

WP 3

VSS 4

8 VCC

7 HOLD

6 SCK

5 SI

Block Diagram

Status

Register

HV Generator

I/O Control

Logic

Memory

Control

Logic

X

Dec

EEPROM

Array

Page Latches

SI

SO

CS

SCK

HOLD

WP

VCC

VSS

Y Decoder

Sense Amp.

R/W Control

1997-2012 Microchip Technology Inc.

DS21230E-page 1

25AA080/25LC080/25C080

3.6 Write Status Register (WRSR)

The Write Status Register (WRSR) instruction allows the

user to select one of four levels of protection for the

array by writing to the appropriate bits in the Status reg-

ister. The array is divided up into four segments. The

user has the ability to write-protect none, one, two, or

all four of the segments of the array. The partitioning is

controlled as shown in Table 3-2.

The Write-Protect Enable (WPEN) bit is a nonvolatile

bit that is available as an enable bit for the WP pin. The

Write-Protect (WP) pin and the Write-Protect Enable

(WPEN) bit in the Status register control the program-

mable hardware write-protect feature. Hardware write

protection is enabled when WP pin is low and the

WPEN bit is high. Hardware write protection is disabled

when either the WP pin is high or the WPEN bit is low.

When the chip is hardware write-protected, only writes

to nonvolatile bits in the Status register are disabled.

See Table 3-3 for a matrix of functionality on the WPEN

bit.

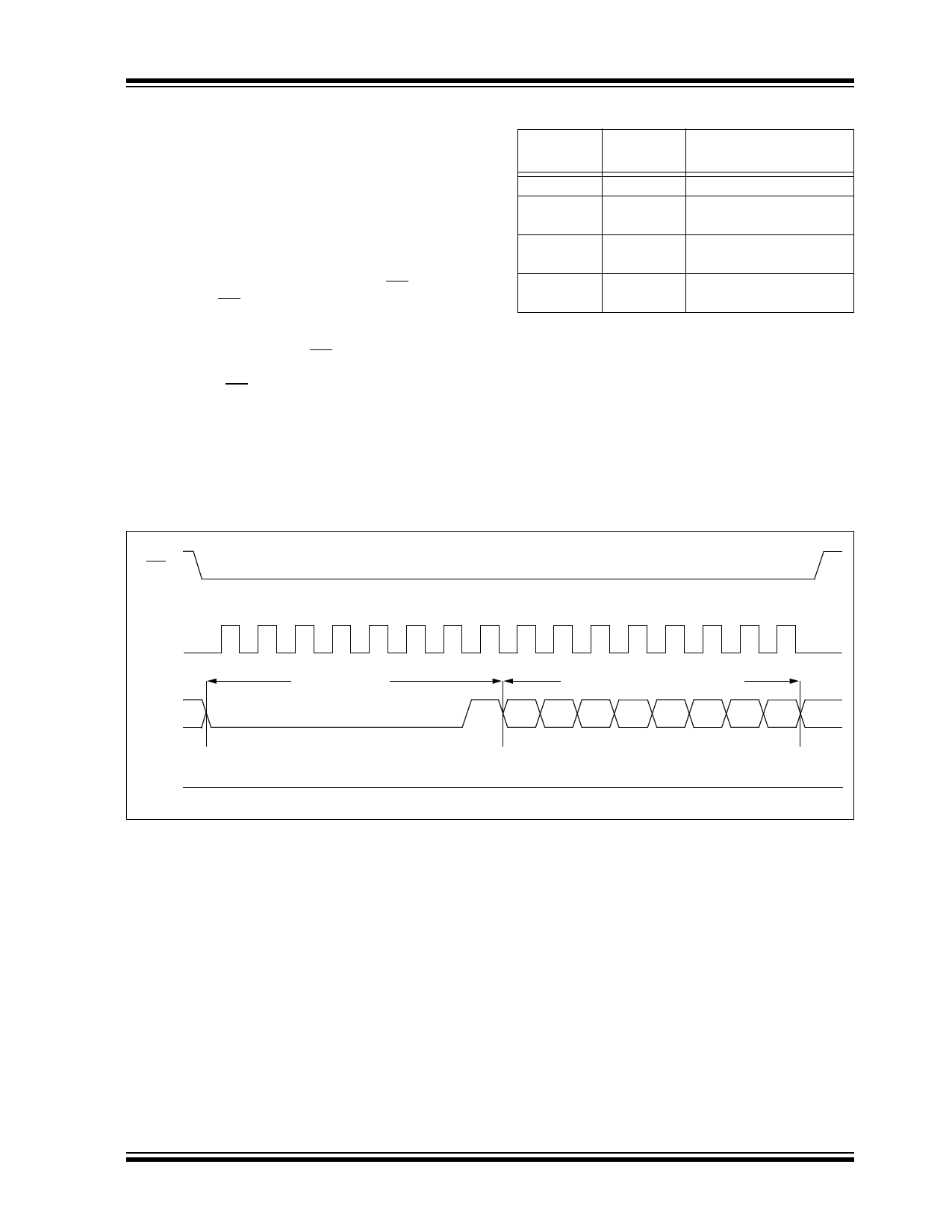

See Figure 3-5 for the WRSR timing sequence.

TABLE 3-2:

BP1

0

0

1

1

ARRAY PROTECTION

BP0

Array Addresses

Write-Protected

0 none

1 upper 1/4

(0300h - 03FFh)

0 upper 1/2

(0200h - 03FFh)

1 all

(0000h - 03FFh)

FIGURE 3-7:

WRITE STATUS REGISTER TIMING SEQUENCE

CS

SCK

SI

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

instruction

data to Status register

0 00 00 0 01 7 6 54 3 2 10

High-impedance

SO

1997-2012 Microchip Technology Inc.

DS21230E-page 11