|

|

PDF IS45S16400J Data sheet ( Hoja de datos )

| Número de pieza | IS45S16400J | |

| Descripción | SYNCHRONOUS DYNAMIC RAM | |

| Fabricantes | ISSI | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de IS45S16400J (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

IS42S16400J

IS45S16400J

1 Meg Bits x 16 Bits x 4 Banks (64-MBIT)

SYNCHRONOUS DYNAMIC RAM

JULY 2014

FEATURES

• Clock frequency: 200, 166, 143, 133 MHz

• Fully synchronous; all signals referenced to a

positive clock edge

• Internal bank for hiding row access/precharge

• Single 3.3V power supply

• LVTTL interface

• Programmable burst length

– (1, 2, 4, 8, full page)

• Programmable burst sequence:

Sequential/Interleave

• Self refresh modes

• Auto refresh (CBR)

• 4096 refresh cycles every 64 ms (Com, Ind, A1

grade) or 16ms (A2 grade)

• Random column address every clock cycle

• Programmable CAS latency (2, 3 clocks)

• Burst read/write and burst read/single write

operations capability

• Burst termination by burst stop and precharge

command

OPTIONS

• Package:

54-pin TSOP II

54-ball TF-BGA (8mm x 8mm)

60-ball TF-BGA (10.1mm x 6.4mm)

• Operating Temperature Range

Commercial (0oC to +70oC)

Industrial (-40oC to +85oC)

Automotive Grade A1 (-40oC to +85oC)

Automotive Grade A2 (-40oC to +105oC)

OVERVIEW

ISSI's 64Mb Synchronous DRAM is organized as 1,048,576

bits x 16-bit x 4-bank for improved performance. The

synchronous DRAMs achieve high-speed data transfer

using pipeline architecture. All inputs and outputs signals

refer to the rising edge of the clock input.

KEY TIMING PARAMETERS

Parameter

Clk Cycle Time

CAS Latency = 3

CAS Latency = 2

Clk Frequency

CAS Latency = 3

CAS Latency = 2

Access Time from Clock

CAS Latency = 3

CAS Latency = 2

-5

5

7.5

200

133

4.8

5.4

-6 -7 Unit

6 7 ns

7.5 7.5 ns

166 143 Mhz

133 133 Mhz

5.4 5.4 ns

5.4 5.4 ns

ADDRESS TABLE

Parameter

4M x 16

Configuration

1M x 16 x 4

banks

Refresh Count

Com./Ind.

A1

A2

4K/64ms

4K/64ms

4K/16ms

Row Addresses

A0-A11

Column Addresses

A0-A7

Bank Address Pins

BA0, BA1

Auto Precharge Pins

A10/AP

Copyright © 2014 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no

liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on

any published information and before placing orders for products.

Integrated Silicon Solution, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be ex-

pected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless Integrated Silicon

Solution, Inc. receives written assurance to its satisfaction, that:

a.) the risk of injury or damage has been minimized;

b.) the user assume all such risks; and

c.) potential liability of Integrated Silicon Solution, Inc is adequately protected under the circumstances

Integrated Silicon Solution, Inc. — www.issi.com 1

Rev. G

7/30/2014

1 page

IS42S16400J

IS45S16400J

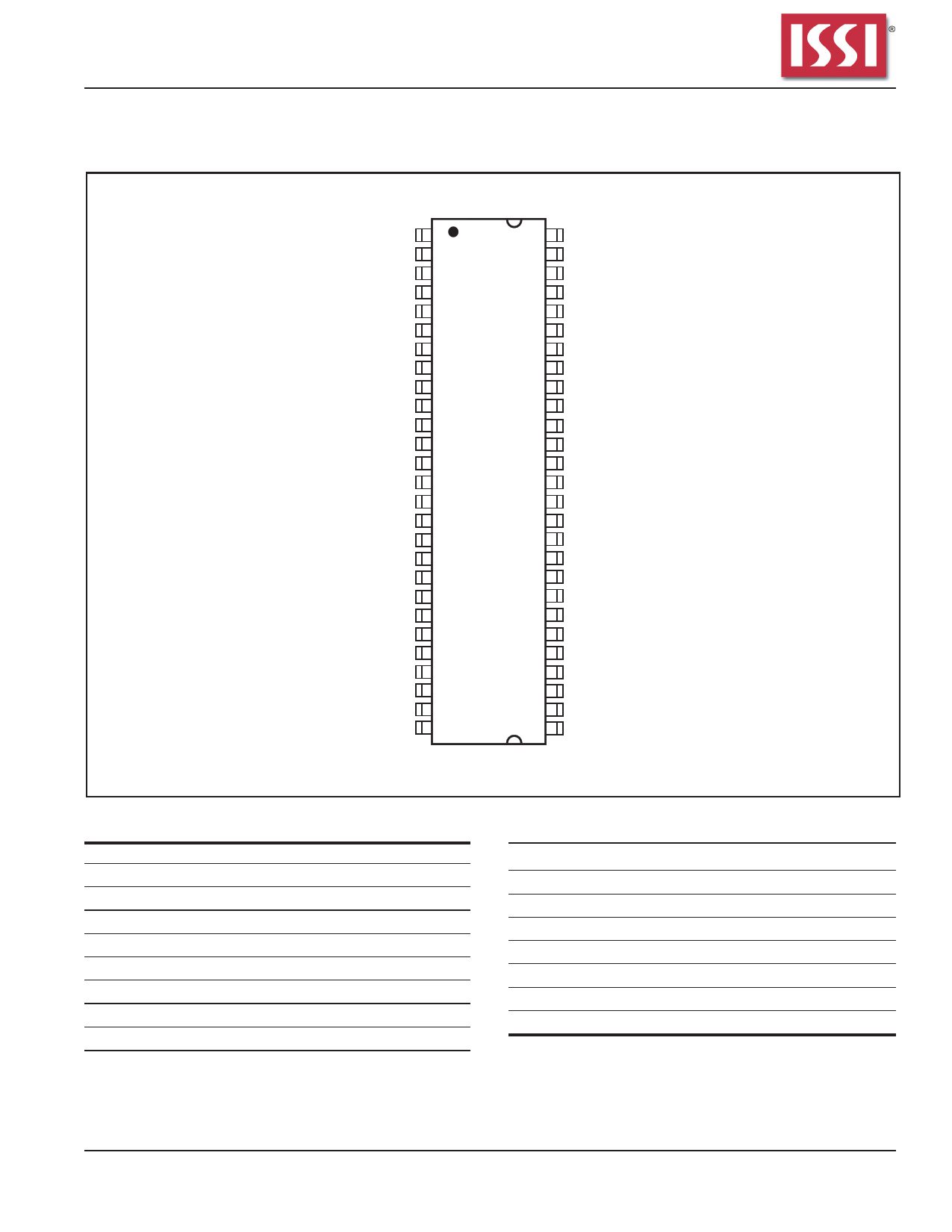

PIN CONFIGURATIONS

54 pin TSOP - Type II

VDD

DQ0

VDDQ

DQ1

DQ2

GNDQ

DQ3

DQ4

VDDQ

DQ5

DQ6

GNDQ

DQ7

VDD

LDQM

WE

CAS

RAS

CS

BA0

BA1

A10

A0

A1

A2

A3

VDD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

54 GND

53 DQ15

52 GNDQ

51 DQ14

50 DQ13

49 VDDQ

48 DQ12

47 DQ11

46 GNDQ

45 DQ10

44 DQ9

43 VDDQ

42 DQ8

41 GND

40 NC

39 UDQM

38 CLK

37 CKE

36 NC

35 A11

34 A9

33 A8

32 A7

31 A6

30 A5

29 A4

28 GND

PIN DESCRIPTIONS

A0-A11

Row Address Input

A0-A7

Column Address Input

BA0, BA1

Bank Select Address

DQ0 to DQ15 Data I/O

CLK

System Clock Input

CKE

Clock Enable

CS

Chip Select

RAS

Row Address Strobe Command

CAS Column Address Strobe Command

WE Write Enable

LDQM x16 Lower Byte, Input/Output Mask

UDQM x16 Upper Byte, Input/Output Mask

Vdd Power

GND Ground

Vddq Power Supply for I/O Pin

GNDq Ground for I/O Pin

NC No Connection

Integrated Silicon Solution, Inc. — www.issi.com 5

Rev. G

7/30/2014

5 Page

IS42S16400J

IS45S16400J

3. Current state definitions:

Idle: The bank has been precharged, and trp has been met.

Row Active: A row in the bank has been activated, and trcd has been met. No data bursts/accesses and no register

accesses are in progress.

Read: A READ burst has been initiated, with auto precharge disabled, and has not yet terminated or been termi-

nated.

Write: A WRITE burst has been initiated, with auto precharge disabled, and has not yet terminated or been termi-

nated.

4. The following states must not be interrupted by a command issued to the same bank. COMMAND INHIBIT or NOP commands,

or allowable commands to the other bank should be issued on any clock edge occurring during these states. Allowable com-

mands to the other bank are determined by its current state and CURRENT STATE BANK n truth tables.

Precharging: Starts with registration of a PRECHARGE command and ends when trp is met. Once trp is met, the bank

will be in the idle state.

Row Activating: Starts with registration of an ACTIVE command and ends when trcd is met. Once trcd is met, the bank will

be in the row active state.

Read w/Auto

Precharge Enabled: Starts with registration of a READ command with auto precharge enabled and ends when trp has been

met. Once trp is met, the bank will be in the idle state.

Write w/Auto

Precharge Enabled: Starts with registration of a WRITE command with auto precharge enabled and ends when trp has been

met. Once trp is met, the bank will be in the idle state.

5. The following states must not be interrupted by any executable command; COMMAND INHIBIT or NOP commands must be

applied on each positive clock edge during these states.

Refreshing: Starts with registration of an AUTO REFRESH command and ends when trc is met. Once trc is met, the

SDRAM will be in the all banks idle state.

Accessing Mode

Register: Starts with registration of a LOAD MODE REGISTER command and ends when tmrd has been met. Once

tmrd is met, the SDRAM will be in the all banks idle state.

Precharging All: Starts with registration of a PRECHARGE ALL command and ends when trp is met. Once trp is met, all

banks will be in the idle state.

6. All states and sequences not shown are illegal or reserved.

7. Not bank-specific; requires that all banks are idle.

8. May or may not be bank-specific; if all banks are to be precharged, all must be in a valid state for precharging.

9. Not bank-specific; BURST TERMINATE affects the most recent READ or WRITE burst, regardless of bank.

10. READs or WRITEs listed in the Command (Action) column include READs or WRITEs with auto precharge enabled and

READs or WRITEs with auto precharge disabled.

11. Does not affect the state of the bank and acts as a NOP to that bank.

Integrated Silicon Solution, Inc. — www.issi.com 11

Rev. G

7/30/2014

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet IS45S16400J.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| IS45S16400C1 | 1 Meg Bits x 16 Bits x 4 Banks (64-MBIT) SYNCHRONOUS DYNAMIC RAM | Integrated Silicon Solution |

| IS45S16400E | 1 Meg Bits x 16 Bits x 4 Banks (64-MBIT) SYNCHRONOUS DYNAMIC RAM | Integrated Silicon Solution |

| IS45S16400F | 1 Meg Bits x 16 Bits x 4 Banks (64-MBIT) SYNCHRONOUS DYNAMIC RAM | Integrated Silicon Solution |

| IS45S16400J | SYNCHRONOUS DYNAMIC RAM | ISSI |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |