|

|

PDF AD9713 Data sheet ( Hoja de datos )

| Número de pieza | AD9713 | |

| Descripción | 100MSPS D/A CONVERTERS | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD9713 (archivo pdf) en la parte inferior de esta página. Total 8 Páginas | ||

|

No Preview Available !

ANALOG DEVICES fAX-ON-DEHAND HOTLINE - Page 23

ANALOG

W DEVICES

12-Bit,100MSPS

UtAConverters

I AD97121AD9713I

FEATURES

100 MSPS Update Rate

ECL/TTL Compatibility

Low Glitch Impulse: 100 pV-s

Fast Settling: 30 ns to %1 LSB

Low Power: 700 mW

FUNCTIONAL BLOCK DIAGRAM

AD9712/AD9713

APPUCA TlONS

ATE

Signal Reconstruction

Arbitrary Waveform Generators

Digital Synthesizers

Signal Generators

OGENERAL DESCRIPTION

BThe AD9712 and AD9713 are I2-bit, high speed digital-

Sto-analog converters constructed in an advanced oxide isolated

bipolar process. The AD9712 is an ECL-compatible device

OfeatUring update rates of 100 MSPS minimum; the TTL-

compatible AD9713 will update at 80 MSPS minimum.

LDesigned for direct digital synthesis, waveform reconstruction,

Eand high resolution imaging applications, both devices feature

low glitch impulse of 100 pV-s; and fast settling times of 30 ns

TEto :!:1 LSB. Both units are characterized for dynamic perfor-

~2o)oo

REFERENCEY

OUT L

o(191

YcONTROL

I AMP IN

The AD9712 and AD9713 are available in 28-pin plastic DIPs

and PLCCs, with an operating temperature range of 0 to + 70°C.

Contact the factory for availability of military-grade devices.

c

~w

0a: .m.:

mance, and have excellent harmonic suppression.

C) %

~iii ;i

Q' a

Q'

Q

~

C

5

<>

~~

61 LATCH ENABLE

ANALOG RETURN 113

!I DIGITAL+V.

rn REFERENCE GROUND

:2J REFERENCE OUT

;1" CONTROL AMP IN

.!!.I CONTROL AMP OUT

m REFERENCE IN

51 ANALOG-V.

Plastic DIPPinout Designations (Top View)

221 REFERENCE GROUND

~ REFERENCE OUT

191 CONTROL AMP IN

I-,,:'

'9"

B~ w0%~,o., .:.:aE5.

:! ~ c:

~.. II!

0

0

PLCC Pinout Designations

REV.A

Information furnished by Analog Devices is believed to be accurate and

reliable. However. no responsibility is assumed by Analog Devices for its

use. nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way. P.O. Box 9106. Norwood. MA 02062-9106

Tel: 617/329-4700 Fax: 617/326-8703 Twx: 710/394-6577

We5t CQut

Central

Atlantic:

714/641-9391

214/231-5094

215/643.7790

http://www.Datasheet4U.com

1 page

-RNRLOGDEVICES fRX-ON-DEHRND HOTLINE

Page 27

AD9712/AD9713

THEORY AND APPUCATIONS

The AD9712 and AD9713 high speed digital-to-analog conven-

ers utilize Most Significant Bit (MSB) decoding and segmenta-

tion techniques to reduce glitch impulse and maintain linearity

without trimming.

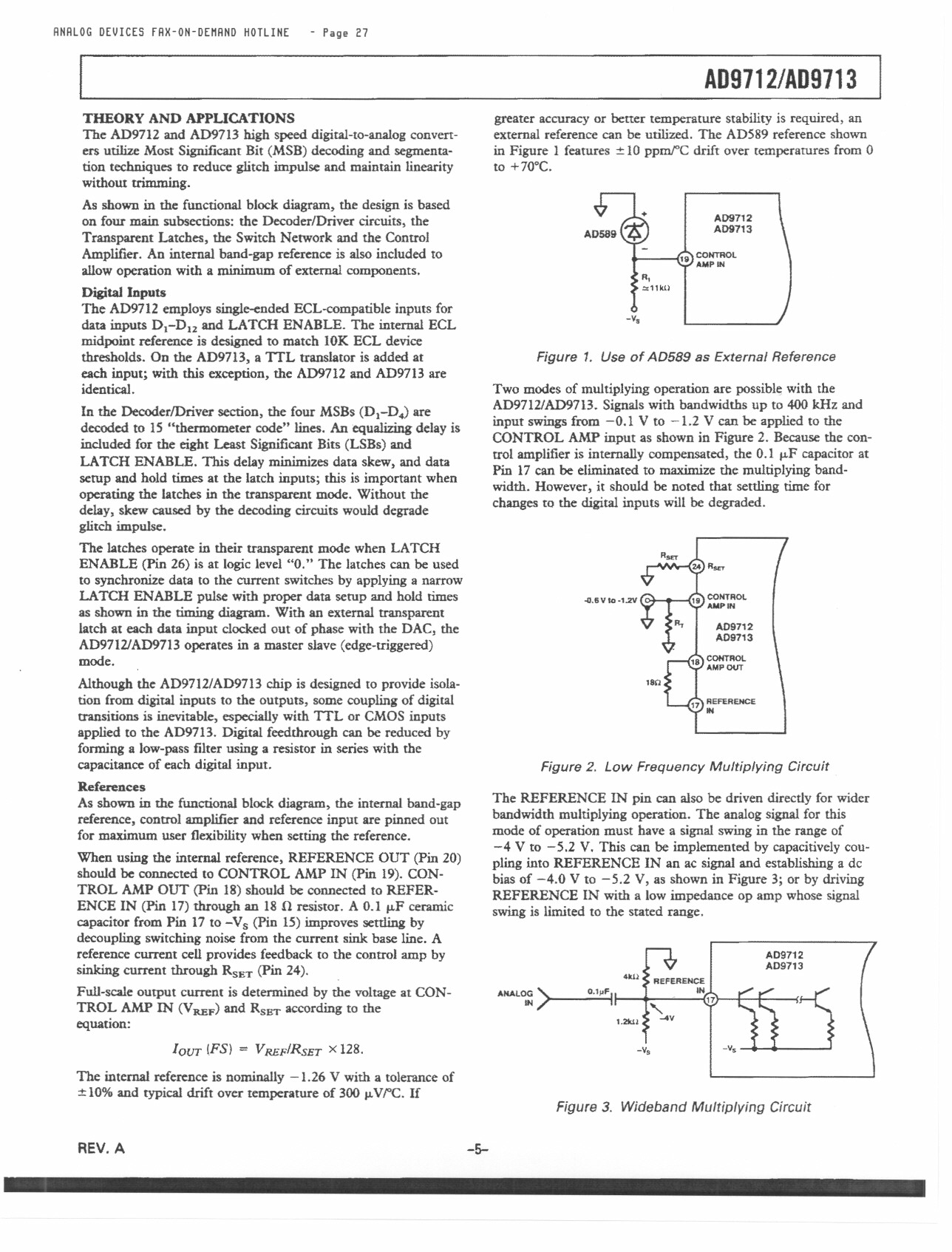

greater accuracy or better temperature stability is required, an

external reference can be utilized. The AD589 reference shown

in Figure I features :t 10 ppm?C drift over temperatUres from 0

to +70°C.

As shown in the functional block diagram, the design is based

on four main subsections: the DecoderlDriver circuits, the

Transparent Latches, the Switch Network and the Control

A09712

A09713

Amplifier. An internal band-gap reference is also included to

allow operation with a minimum of external components.

Digital Inputs

:II1)C4OMNP'TRINOl

R,

::11kl)

The AD9712 employs single-cnded ECL-compatible inputs for

data inpUtS DI-D12 and LATCH ENABLE. The internal ECL

-VI

midpoint reference is designed to match 10K ECL device

thresholds. On the AD9713, a TTL translator is added at

Figure 1. Use of A 0589 8S External Reference

each input; with this exception, the AD9712 and AD9713 are

identical.

In the DecoderlDriver section, the four MSBs (DcDJ are

decoded to 15 "thermometer code" lines. An equalizing delay is

included for the eight Least Significant Bits (LSBs) and

LATCH ENABLE. This delay minimizes data skew, and data

Osetup and hold times at the latch inputs; this is important when

operating the latches in the transparent mode. Without the

Bdelay, skew caused by the decoding circuits would degrade

glitch impulse.

SThe latches operate in their transparent mode when LATCH

OENABLE (Pin 26) is at logic level "0." The latches can be used

to synchronize data to the current switches by applying a narrow

LLATCH ENABLE pulse with proper data setup and hold times

Eas shown in the timing diagram. With an external transparent

latch at each data input clocked out of phase with the DAC, the

TAD97121AD9713 operates in a master slave (edge-triggered)

Emode.

Two modes of multiplying operation are possibl~ with the

AD97121AD9713. Signals with bandwidths up to 400 kHz and

input swings from -0.1 V to -1.2 V can be applied to the

CONTROL AMP input as shown in Figure 2. Because the con-

trol amplifier is internally compensated, the 0.1 J.LFcapacitor at

Pin 17 can be eliminated to maximize the multiplying band-

width. However, it should be noted that settling time for

changes to the digital inputs will be degraded.

.IJ.6Vlo.l.2V

Although the AD97121AD9713 chip is designed to provide isola-

tion from digital inputs to the outputs, some coupling of digital

transitions is inevitable, especially with TTL or CMOS inputs

applied to the AD9713. Digital feedthrough can be reduced by

forming a low-pass filter using a resistor in series with the

capacitance of each digital input.

References

As shown in the functional block diagram, the internal band-gap

reference, control amplifier and reference input are pinned out

for maximum user flexibility when setting the reference.

When using the internal reference, REFERENCE OUT (Pin 20)

should be connected to CONTROL AMP IN (pin 19). CON-

TROL AMP OUT (pin 18) should be connected to REFER-

ENCE IN (Pin 17) through an 18 n resistor. A 0.1 J.LFceramic

capacitor from Pin 17 to -Vs (pin 15) improves settling by

decoupllng switching noise from the current sink base line. A

reference current cell provides feedback to the control amp by

sinking current through Rsn (Pin 24).

Full-scale output current is determined by the voltage at CON-

TROL AMP IN (VREF)and Rsn according to the

equation:

=lOUT IPS) VREFIRsET x 128.

181l

Figure 2. Low Frequency Multiplying Circuit

The REFERENCE IN pin can also be driven directly for wider

bandwidth multiplying operation. The analog signal for this

mode of operation must have a signal swing in the range of

-4 V to -5.2 V. This can be implemented by capacitively cou-

pling into REFERENCE IN an ac signal and establishing a de

bias of -4.0 V to -5.2 V, as shown in Figure 3; or by driving

REFERENCE IN with a low impedance op amp whose signal

swing is limited to the stated range.

>ANAl~

4k1l

O.I~FI

1.2k11

-V.

AD9712

AD9713

-vo

The internal reference is nominally - 1.26 V with a tolerance of

:t 10% and typical drift over temperature of 300 J.Lvrc. If

Figure 3. Wideband Multiplying Circuit

REV. A

-5-

http://www.Datasheet4U.com

5 Page | ||

| Páginas | Total 8 Páginas | |

| PDF Descargar | [ Datasheet AD9713.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD9712 | 100MSPS D/A CONVERTERS | Analog Devices |

| AD9712B | 12-Bit/ 100 MSPS D/A Converters | Analog Devices |

| AD9713 | 100MSPS D/A CONVERTERS | Analog Devices |

| AD9713B | 12-Bit/ 100 MSPS D/A Converters | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |