|

|

PDF RTL8110SCL-GR Data sheet ( Hoja de datos )

| Número de pieza | RTL8110SCL-GR | |

| Descripción | Intergated Gigabit Ethernet Controller | |

| Fabricantes | Realtek Microelectronics | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de RTL8110SCL-GR (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

RTL8110SC-GR

RTL8110SCL-GR

INTEGRATED GIGABIT ETHERNET

CONTROLLER (LOM) (MiniPCI)

www.DataSheet.co.kr

DATASHEET

Rev. 1.3

09 January 2007

Track ID: JATR-1076-21

Realtek Semiconductor Corp.

No. 2, Innovation Road II, Hsinchu Science Park, Hsinchu 300, Taiwan

Tel.: +886-3-578-0211. Fax: +886-3-577-6047

www.realtek.com.tw

Datasheet pdf - http://www.DataSheet4U.net/

1 page

RTL8110SC(L)

Datasheet

List of Figures

FIGURE 1. 128-PIN (L)QFP PIN ASSIGNMENTS ............................................................................................................................3

FIGURE 2. LITTLE-ENDIAN BYTE ORDERING................................................................................................................................9

FIGURE 3. BIG-ENDIAN BYTE ORDERING.....................................................................................................................................9

FIGURE 4. TARGET READ OPERATION........................................................................................................................................10

FIGURE 5. TARGET WRITE OPERATION ......................................................................................................................................11

FIGURE 6. MASTER READ OPERATION .......................................................................................................................................12

FIGURE 7. MASTER WRITE OPERATION......................................................................................................................................13

FIGURE 8. RX LED.....................................................................................................................................................................14

FIGURE 9. TX LED.....................................................................................................................................................................15

FIGURE 10. TX/RX LED ..............................................................................................................................................................16

FIGURE 11. LINK/ACT LED ......................................................................................................................................................17

FIGURE 12. SERIAL EEPROM INTERFACE TIMING......................................................................................................................24

FIGURE 13. OUTPUT TIMING MEASUREMENT CONDITIONS .........................................................................................................25

FIGURE 14. INPUT TIMING MEASUREMENT CONDITIONS.............................................................................................................26

FIGURE 15. 3.3V CLOCK WAVEFORM .........................................................................................................................................26

FIGURE 16. CLOCK SKEW DIAGRAM ...........................................................................................................................................27

FIGURE 17. I/O READ ..................................................................................................................................................................27

FIGURE 18. I/O WRITE.................................................................................................................................................................28

FIGURE 19. CONFIGURATION READ.............................................................................................................................................28

FIGURE 20. CONFIGURATION WRITE ...........................................................................................................................................29

FIGURE 21. BUS ARBITRATION....................................................................................................................................................29

FIGURE 22. MEMORY READ BELOW 4GB....................................................................................................................................30

FIGURE 23. MEMORY WRITE BELOW 4GB ..................................................................................................................................30

FIGURE 24. TARGET INITIATED TERMINATION - DISCONNECT.....................................................................................................31

FIGURE 25. TARGET INITIATED TERMINATION - ABORT ..............................................................................................................31

FIGURE 26. MASTER INITIATED TERMINATION - ABORT .............................................................................................................32

FIGURE 27. PARITY OPERATION – ONE EXAMPLE .......................................................................................................................32

FIGURE 28. MEMORY READ ABOVE 4GB (DAC) ........................................................................................................................33

FIGURE 29. MEMORY WRITE ABOVE 4GB (DAC) .........................w.ww.D.ataSh.eet.c.o.kr.........................................................................................33

Integrated Gigabit Ethernet Controller (LOM) (MiniPCI) v

Track ID: JATR-1076-21 Rev. 1.3

Datasheet pdf - http://www.DataSheet4U.net/

5 Page

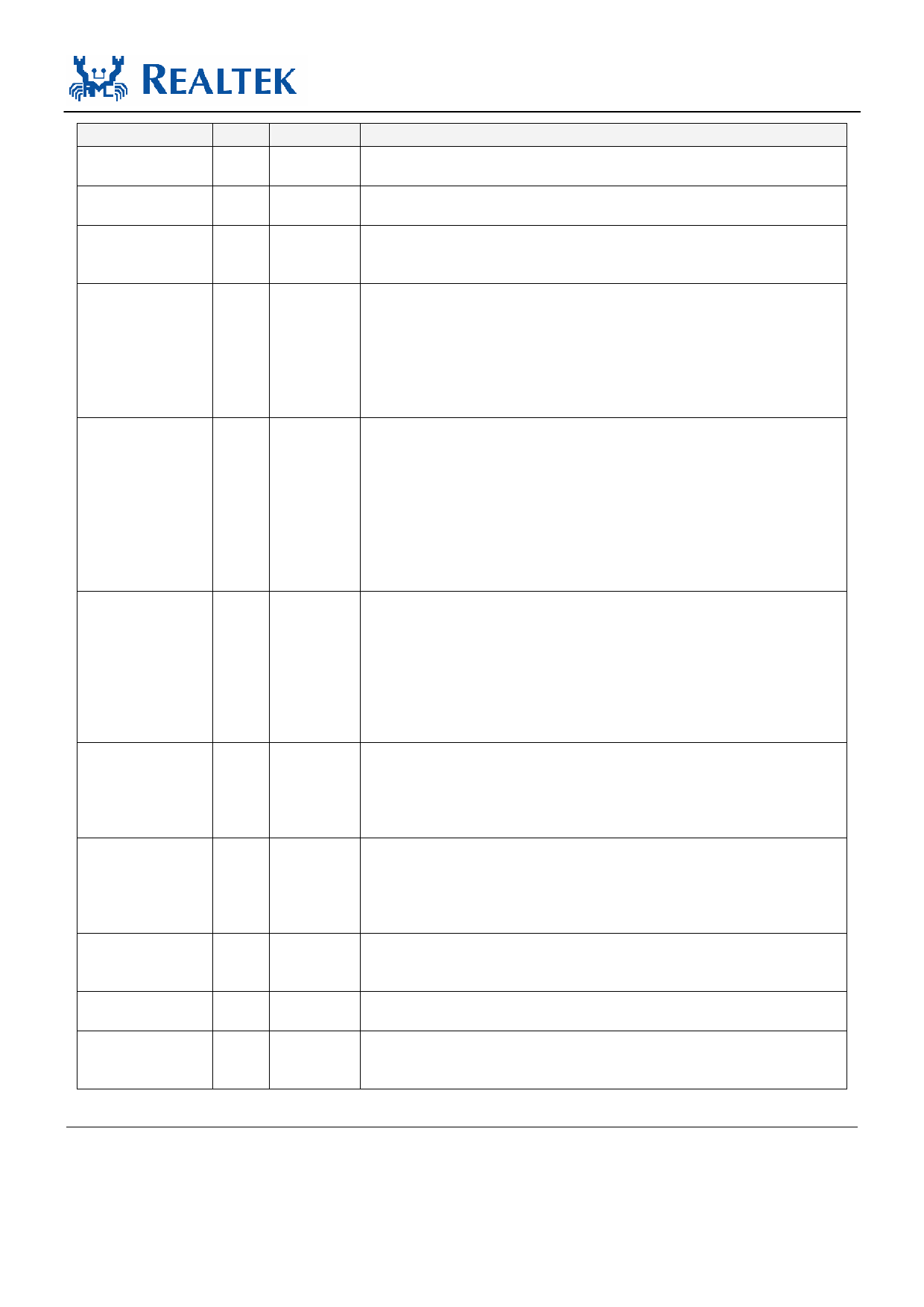

Symbol

REQB

IDSEL

INTAB

IRDYB

TRDYB

PAR

M66EN

PERRB

SERRB

STOPB

PCIRSTB

Type

T/S

I

O/D

S/T/S

S/T/S

T/S

I

S/T/S

O/D

S/T/S

I

RTL8110SC(L)

Datasheet

Pin No

30

46

25

63

67

76

88

70

75

69

27

Description

Request: The RTL8110SC(L) will assert this signal low to request the

ownership of the bus from the central arbiter.

Initialization Device Select: This pin allows the device to identify when

configuration read/write transactions are intended for it.

Interrupt A: Used to request an interrupt. It is asserted low when an

interrupt condition occurs, as defined by the Interrupt Status, Interrupt

Mask.

Initiator Ready: This indicates the initiating agent’s ability to complete the

current data phase of the transaction.

As a bus master, this signal will be asserted low when the device is ready to

complete the current data phase transaction. This signal is used in

conjunction with the TRDYB signal. Data transaction takes place at the

rising edge of CLK when both IRDYB and TRDYB are asserted low. As a

target, this signal indicates that the master has put data on the bus.

Target Ready: This indicates the target agent’s ability to complete the

current phase of the transaction.

As a bus master, this signal indicates that the target is ready for the data

during write operations, or is ready to provide the data during read

operations.

As a target, this signal will be asserted low when the (slave) device is ready

to complete the current data phase transaction. This signal is used in

conjunction with the IRDYB signal. Data transaction takes place at the

rising edge of CLK, when both IRDYB and TRDYB are asserted low.

Parity: This signal indicates even parity across PCIADPIN31-0 and

CBEB3-0 including the PAR pin. PAR is stable and valid one clock after

each address phase. For data phase, PAR is stable and valid one clock after

either IRDYB is asserted on a write transaction or TRDYB is asserted on a

read transaction. Oncewww.DataSheet.co.kr PAR is valid, it remains valid until one clock after

the completion of the current data phase. As a bus master, PAR is asserted

during address and write data phases. As a target, PAR is asserted during

read data phases.

66MHZ_ENABLE: This pin indicates to the device whether the bus

segment is operating at 66 or 33MHz. When this pin (active high) is

asserted, the current PCI bus segment that the device resides on operates in

66MHz mode. If this pin is de-asserted, the current PCI bus segment

operates in 33MHz mode.

Parity Error: This pin is used to report data parity errors during all PCI

transactions except a Special Cycle. PERRB is driven active (low) two

clocks after a data parity error is detected by the device receiving data, and

the minimum duration of PERRB is one clock for each data phase with

parity error detected.

System Error: If an address parity error is detected and Configuration Space

Status register bit 15 (detect parity error) is enabled, the device asserts the

SERRB pin low and bit 14 of the Status register in Configuration Space.

Stop: Indicates that the current target is requesting the master to stop the

current transaction.

Reset: When PCIRSTB is asserted low, the device performs an internal

system hardware reset. PCIRSTB must be held for a minimum period

of 120ns.

Integrated Gigabit Ethernet Controller (LOM) (MiniPCI) 6

Track ID: JATR-1076-21 Rev. 1.3

Datasheet pdf - http://www.DataSheet4U.net/

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet RTL8110SCL-GR.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| RTL8110SCL-GR | Intergated Gigabit Ethernet Controller | Realtek Microelectronics |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |