|

|

PDF MC74HC112A Data sheet ( Hoja de datos )

| Número de pieza | MC74HC112A | |

| Descripción | Dual J-K Flip-Flop | |

| Fabricantes | ON Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de MC74HC112A (archivo pdf) en la parte inferior de esta página. Total 8 Páginas | ||

|

No Preview Available !

MC74HC112A

www.DataSheet4U.com

Dual J-K Flip-Flop with

Set and Reset

High−Performance Silicon−Gate CMOS

The MC74HC112A is identical in pinout to the LS112. The device

inputs are compatible with standard CMOS outputs; with pullup

resistors, they are compatible with LSTTL outputs.

Each flip−flop is negative−edge clocked and has active−low

asynchronous Set and Reset inputs.

The HC112A is identical in function to the HC76, but has a different

pinout.

Features

• Output Drive Capability: 10 LSTTL Loads

• Outputs Directly Interface to CMOS, NMOS, and TTL

• Operating Voltage Range: 2.0 to 6.0 V

• Low Input Current: 1.0 mA

• High Noise Immunity Characteristic of CMOS Devices

• In Compliance with the Requirements Defined by JEDEC Standard

No. 7A

• Similar in Function to the LS112 Except When Set and Reset are

Low Simultaneously

• Chip Complexity: 100 FETs or 25 Equivalent Gates

• Pb−Free Packages are Available*

16

1

http://onsemi.com

MARKING

DIAGRAMS

16

PDIP−16

N SUFFIX

CASE 648

MC74HC112AN

AWLYYWWG

1

16

1

16

1

16

SOIC−16

D SUFFIX

CASE 751B

HC112AG

AWLYWW

1

TSSOP−16

DT SUFFIX

CASE 948F

16

HC

112A

ALYWG

G

1

16

1

SOEIAJ−16

F SUFFIX

CASE 966

16

74HC112A

ALYWG

1

A = Assembly Location

L, WL = Wafer Lot

Y, YY = Year

W, WW = Work Week

G = Pb−Free Package

G = Pb−Free Package

(Note: Microdot may be in either location)

ORDERING INFORMATION

See detailed ordering and shipping information in the package

dimensions section on page 2 of this data sheet.

*For additional information on our Pb−Free strategy and soldering details, please

download the ON Semiconductor Soldering and Mounting Techniques

Reference Manual, SOLDERRM/D.

© Semiconductor Components Industries, LLC, 2009

December, 2009 − Rev. 7

1

Publication Order Number:

MC74HC112/D

1 page

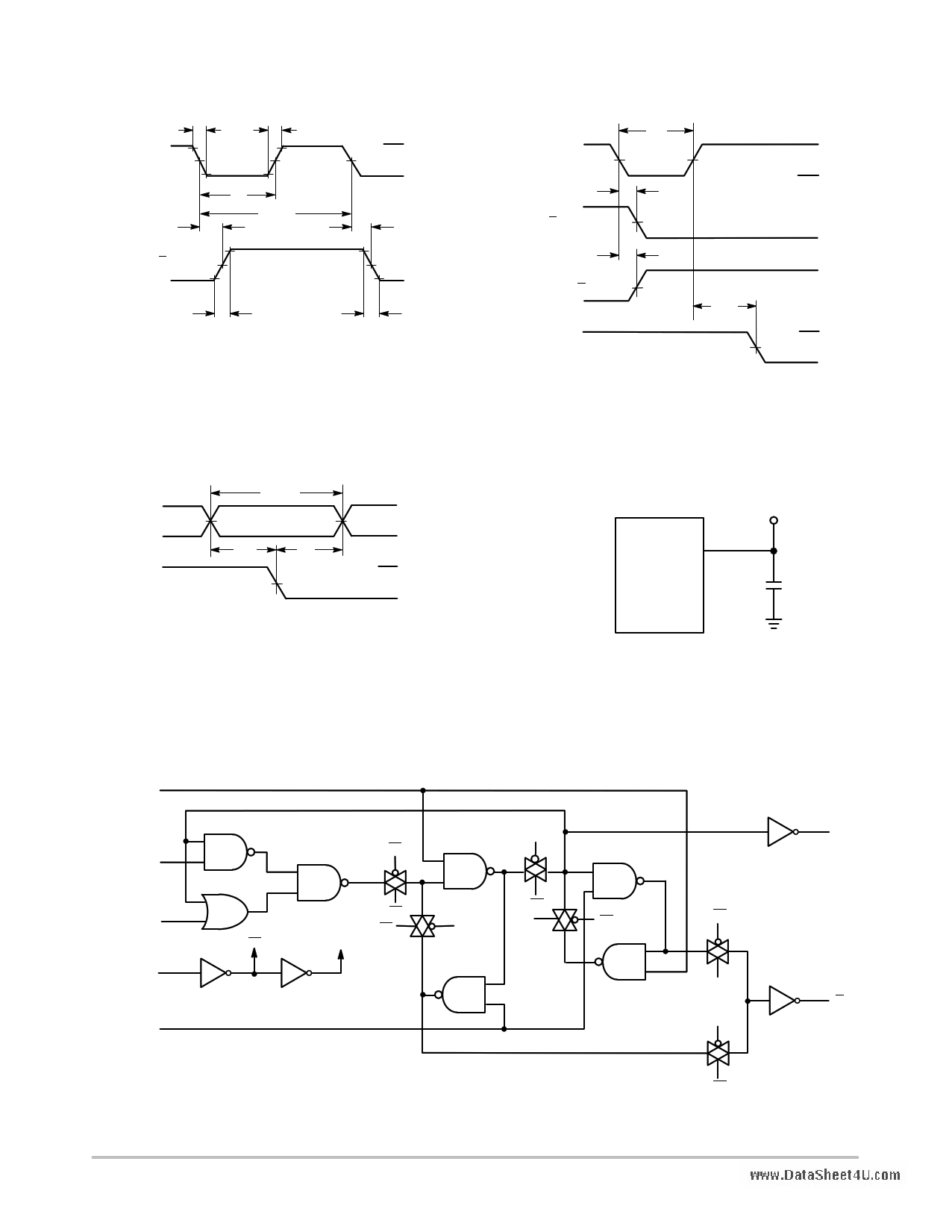

CLOCK

Q or Q

tf

90%

50%

10%

tr

90%

50%

10%

tw

1/fmax

tPLH

tPHL

tTLH tTHL

Figure 1.

MC74HC112A

SWITCHING WAVEFORMS

VCC

SET OR

GND RESET

Q OR Q

Q OR Q

CLOCK

www.DataSheet4U.com

tw

50%

tPHL

50%

tPLH

50%

trec

50%

Figure 2.

VCC

GND

VCC

GND

J OR K

CLOCK

VALID

50%

tsu th

50%

Figure 3.

VCC

GND

VCC

GND

DEVICE

UNDER

TEST

TEST POINT

OUTPUT

CL*

*Includes all probe and jig capacitance

Figure 4. Test Circuit

RESET 15, 14

J 3, 11

K 2,12

1, 13

CLOCK

SET 4, 10

CL

EXPANDED LOGIC DIAGRAM

CL

CL

CL

CL

CL

CL

CL CL

CL

5, 9

Q

CL

CL 6, 7

Q

CL

CL

http://onsemi.com

5

5 Page | ||

| Páginas | Total 8 Páginas | |

| PDF Descargar | [ Datasheet MC74HC112A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| MC74HC112A | Dual J-K Flip-Flop | ON Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |