|

|

PDF IS45LV44002B Data sheet ( Hoja de datos )

| Número de pieza | IS45LV44002B | |

| Descripción | DYNAMIC RAM | |

| Fabricantes | Integrated Silicon Solution | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de IS45LV44002B (archivo pdf) en la parte inferior de esta página. Total 20 Páginas | ||

|

No Preview Available !

IS45LV44002B

4M x 4 (16-MBIT) DYNAMIC RAM

WITH EDO PAGE MODE

ISSI®

www.DataSheet4U.com

SEPTEMBER 2005

FEATURES

• Extended Data-Out (EDO) Page Mode access cycle

• TTL compatible inputs and outputs

• Refresh Interval:

– 2,048 cycles/32 ms

• Refresh Mode: RAS-Only,

CAS-before-RAS (CBR), and Hidden

• Single power supply: 3.3V ± 10%

• Byte Write and Byte Read operation via two CAS

• Automotive Temperature Range

Option A1: -40°C to +85°C

• Lead-free available

DESCRIPTION

The ISSI IS45LV44002B is 4,194,304 x 4-bit high-performance

CMOS Dynamic Random Access Memory. These de-

vices offer an accelerated cycle access called EDO Page

Mode. EDO Page Mode allows 2,048 random accesses

within a single row with access cycle time as short as 20 ns

per 4-bit word.

These features make the IS45LV44002B ideally suited for

high-bandwidth graphics, digital signal processing, high-

performance computing systems, and peripheral

applications.

The IS45LV44002B is packaged in a 24-pin 300-mil SOJ

with JEDEC standard pinouts.

PRODUCT SERIES OVERVIEW

Part No.

IS45LV44002B

Refresh

2K

Voltage

3.3V ± 10%

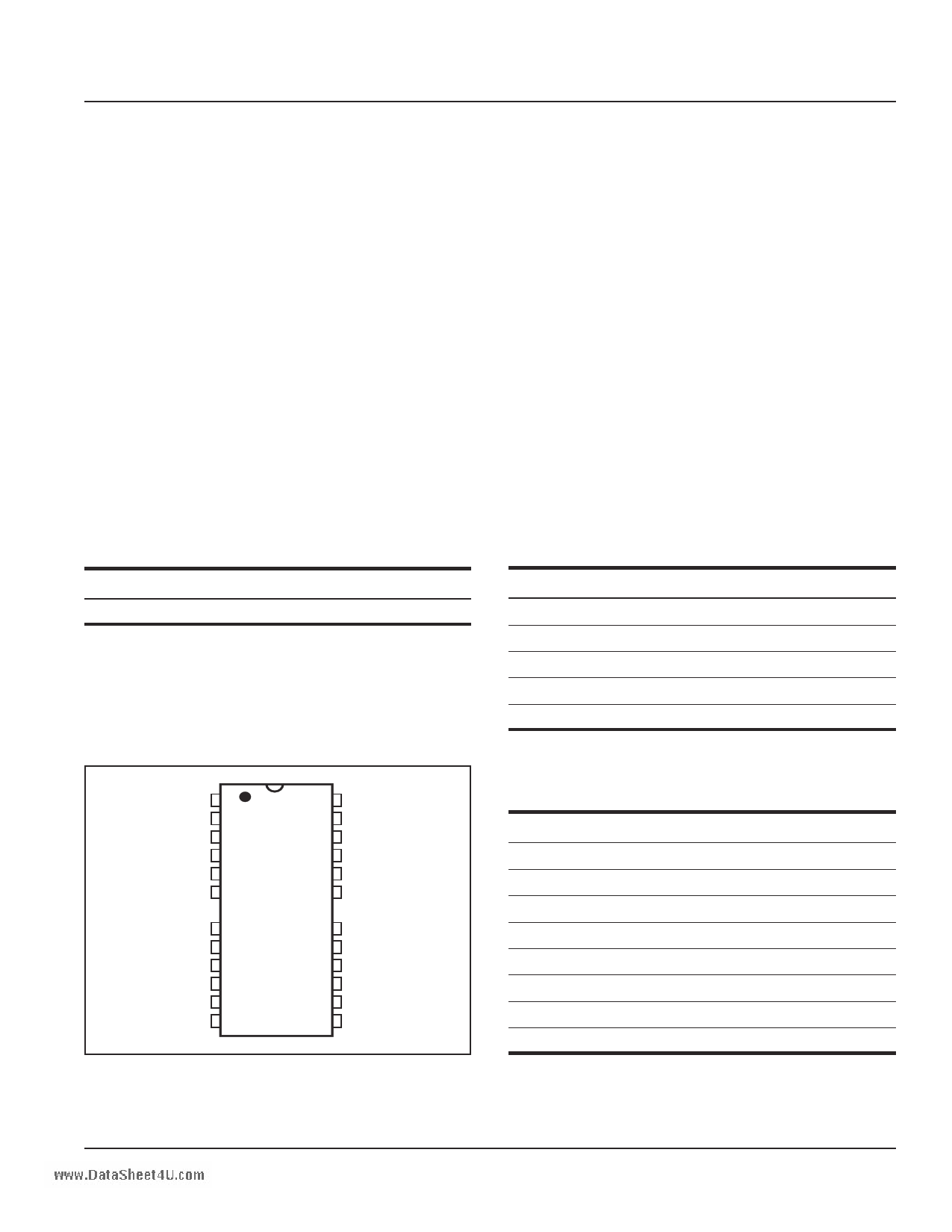

PIN CONFIGURATION: 24-pin SOJ

VDD

I/O0

I/O1

WE

RAS

NC

1

2

3

4

5

6

A10

A0

A1

A2

A3

VDD

7

8

9

10

11

12

24 GND

23 I/O3

22 I/O2

21 CAS

20 OE

19 A9

18 A8

17 A7

16 A6

15 A5

14 A4

13 GND

KEY TIMING PARAMETERS

Parameter

RAS Access Time (tRAC)

CAS Access Time (tCAC)

Column Address Access Time (tAA)

EDO Page Mode Cycle Time (tPC)

Read/Write Cycle Time (tRC)

-50

50

13

25

20

84

Unit

ns

ns

ns

ns

ns

PIN DESCRIPTIONS

A0-A10

I/O0-3

WE

OE

RAS

CAS

VDD

GND

NC

Address Inputs

Data Inputs/Outputs

Write Enable

Output Enable

Row Address Strobe

Column Address Strobe

Power

Ground

No Connection

Copyright © 2005 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time

without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to

obtain the latest version of this device specification before relying on any published information and before placing orders for products.

Integrated Silicon Solution, Inc. — 1-800-379-4774

Rev. A

09/12/05

1

1 page

IS45LV44002B

ISSI ®

www.DataSheet4U.com

ELECTRICAL CHARACTERISTICS(1)

(Recommended Operating Conditions unless otherwise noted.)

Symbol Parameter

Test Condition

Speed Min. Max. Unit

IIL Input Leakage Current

Any input 0V ≤ VIN ≤ VDD

Other inputs not under test = 0V

–5 5 µA

IIO Output Leakage Current Output is disabled (Hi-Z)

0V ≤ VOUT ≤ VDD

–5 5 µA

VOH Output High Voltage Level

IOH = –2.0 mA, VDD = 3.3V

2.4 —

V

VOL Output Low Voltage Level

IOL = 2 mA, VDD = 3.3V

ICC1 Standby Current: TTL

RAS, CAS ≥ VIH

ICC2 Standby Current: CMOS

RAS, CAS ≥ VDD – 0.2V

ICC3 Operating Current:

RAS, CAS,

Random Read/Write(2,3,4)

Address Cycling, tRC = tRC (min.)

Average Power Supply Current

ICC4 Operating Current:

RAS = VIL, CAS,

EDO Page Mode(2,3,4)

Cycling tPC = tPC (min.)

Average Power Supply Current

ICC5 Refresh Current:

RAS-Only(2,3)

RAS Cycling, CAS ≥ VIH

tRC = tRC (min.)

Average Power Supply Current

ICC6 Refresh Current:

RAS, CAS Cycling

CBR(2,3,5)

tRC = tRC (min.)

Average Power Supply Current

— 0.4

V

— 2 mA

— 0.5 mA

-50 — 120 mA

-50 — 90 mA

-50 — 120 mA

-50 — 120 mA

Notes:

1. An initial pause of 200 µs is required after power-up followed by eight RAS refresh cycles (RAS-Only or CBR) before proper device

operation is assured. The eight RAS cycles wake-up should be repeated any time the tREF refresh requirement is exceeded.

2. Dependent on cycle rates.

3. Specified values are obtained with minimum cycle time and the output open.

4. Column-address is changed once each EDO page cycle.

5. Enables on-chip refresh and address counters.

Integrated Silicon Solution, Inc. — 1-800-379-4774

Rev. A

09/12/05

5

5 Page

IS45LV44002B

READ WRITE CYCLE (LATE WRITE and READ-MODIFY-WRITE Cycles)

ISSI ®

www.DataSheet4U.com

RAS

tCRP

CAS

tASR

ADDRESS

WE

I/O

OE

Row

tRWC

tRAS

tRP

tRCD

tCSH

tRSH

tCAS tCLCH

tRAD

tRAH

tAR

tASC

tCAH

tRAL

tACH

tRCS

Column

tRWD

tCWD

tAWD

Row

tCWL

tRWL

tWP

Open

tRAC

tCAC

tCLZ

tAA

tOE

tDS tDH

Valid DOUT Valid DIN

Open

tOD tOEH

Don’t Care

Integrated Silicon Solution, Inc. — 1-800-379-4774

Rev. A

09/12/05

11

11 Page | ||

| Páginas | Total 20 Páginas | |

| PDF Descargar | [ Datasheet IS45LV44002B.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| IS45LV44002B | DYNAMIC RAM | Integrated Silicon Solution |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |