|

|

PDF ISL6506B Data sheet ( Hoja de datos )

| Número de pieza | ISL6506B | |

| Descripción | Multiple Linear Power Controller | |

| Fabricantes | Intersil Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ISL6506B (archivo pdf) en la parte inferior de esta página. Total 8 Páginas | ||

|

No Preview Available !

®

Data Sheet

ISL6506, ISL6506A, ISL6506B

May 2, 2005

www.DataSheet4U.com

FN9141.2

Multiple Linear Power Controller with

ACPI Control Interface

The ISL6506 complements other power building blocks

(voltage regulators) in ACPI-compliant designs for

microprocessor and computer applications. The IC

integrates the control of the 5VDUAL and 3.3VDUAL rails into

an 8 pin EPAD SOIC package. The ISL6506 operating mode

(active outputs or sleep outputs) is selectable through two

digital control pins, S3# and S5#.

A completely integrated linear regulator generates the

3.3VDUAL voltage plane from the ATX supply’s 5VSB output

during sleep states (S3, S4/S5). In active states (during S0

and S1/S2), the ISL6506 uses an external N-channel pass

MOSFET to connect the outputs directly to the 3.3V input

supplied by an ATX power supply, for minimal losses.

The ISL6506 powers up the 5VDUAL plane by switching in

the ATX 5V output through an NMOS transistor in active

states, or by switching in the ATX 5VSB through a PMOS (or

PNP) transistor in S3 sleep state. In S4/S5 sleep states, the

ISL6506 and ISL6506B 5VDUAL output is shut down. In the

ISL6506A, the 5VDUAL output stays on during S4/S5 sleep

states.

Functionally, the ISL6506 and ISL6506B are identical. The

ISL6506B, however, features a 2A current limit on the

internal 3.3V LDO while the ISL6506 has a 1A current limit.

The ISL6506A has a 1A current limit on the internal 3.3V

LDO.

Ordering Information

TEMP.

PART NUMBER RANGE (°C)

PACKAGE

PKG.

DWG. #

ISL6506CB

0 to 70 8 Ld EPSOIC

M8.15C

ISL6506CBZ (Note) 0 to 70 8 Ld EPSOIC (Pb-free) M8.15C

ISL6506ACB

0 to 70 8 Ld EPSOIC

M8.15C

ISL6506ACBZ (Note) 0 to 70 8 Ld EPSOIC (Pb-free) M8.15C

ISL6506BCB

0 to 70 8 Ld EPSOIC

M8.15C

ISL6506BCBZ (Note) 0 to 70 8 Ld EPSOIC (Pb-free) M8.15C

ISL6506BCBZA

(Note)

0 to 70 8 Ld EPSOIC (Pb-free) M8.15C

*Add “-T” suffix to part number for tape and reel packaging.

NOTE: Intersil Pb-free products employ special Pb-free material

sets; molding compounds/die attach materials and 100% matte tin

plate termination finish, which are RoHS compliant and compatible

with both SnPb and Pb-free soldering operations. Intersil Pb-free

products are MSL classified at Pb-free peak reflow temperatures that

meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

Features

• Provides 2 ACPI-Controlled Voltages

- 5VDUAL USB/Keyboard/Mouse

- 3.3VDUAL/3.3VSB PCI/Auxiliary/LAN

• Excellent 3.3VDUAL Regulation in S3/S4/S5

- ±2.0% over temperature

- 1A Capability on ISL6506 and ISL6506A

- 2A Capability on ISL6506B

• Small Size; Very Low External Component Count

• Over-Temperature Shutdown

• Pb-Free Available (RoHS Compliant)

Applications

• ACPI-Compliant Power Regulation for Motherboards

- ISL6506, ISL6506B: 5VDUAL is shut down in S4/S5

sleep states

- ISL6506A: 5VDUAL stays on in S4/S5 sleep states

Pinout

ISL6506 (SOIC)

TOP VIEW

VCC 1

3V3AUX 2

S3# 3

S5# 4

GND

8 N/C

7 5VDLSB

6 DLA

5 GND

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774 | Intersil (and design) is a registered trademark of Intersil Americas Inc.

Copyright © Intersil Americas Inc. 2004-2005. All Rights Reserved.

All other trademarks mentioned are the property of their respective owners.

1 page

5VSB

S3

S5

3.3V, 5V, 12V

DLA

3V3DL

5VDLSB

5VDL

ISL6506, ISL6506A, ISL6506B

5VSB

(1V/DIV)

12VATX (2V/DIV)

5VATX (1V/DIV)

3.3VATX (1V/DIV)

www.DataSheet4U.com

3.3VDUAL

(2V/DIV)

5VDUAL

(1V/DIV)

0V

DLA

(10V/DIV)

FIGURE 2. 5VDUAL AND 3.3VAUX TIMING DIAGRAM;

ISL6506A

Soft-Start

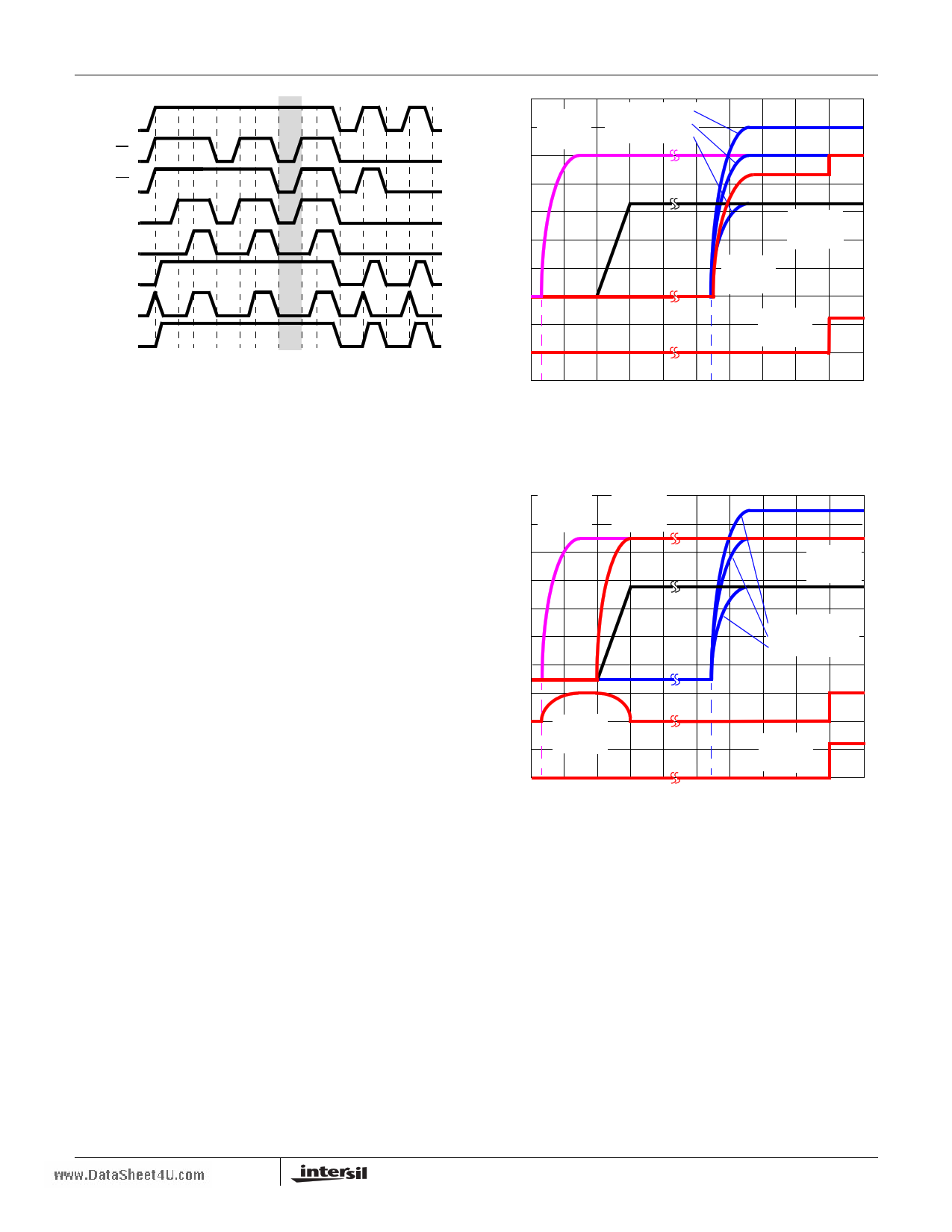

Figures 3 and 4 show the soft-start sequence for the typical

application start-up into a sleep state. At time T0, 5VSB

(bias) is applied to the circuit. At time T1, the 5VSB

surpasses POR level. Time T2, one soft start interval after

T1, denotes the initiation of soft start. The 3.3VDUAL rail is

brought up through the internal standby LDO through an

internal digital soft start function. Figure 4 shows the 5VDUAL

rail initiating a soft start at time T2 as well. The ISL6506A will

draw 7.5µA into the 5VDLSB for a duration of one soft start

period. This current will enhance the P-MOSFET (Q2, refer

to Typical Application Schematic) in a controlled manner. At

time T3, the 3.3VDUAL is in regulation and the 5VDLSB pin

is pulled down to ground. If the 5VDUAL rail has not reached

the level of the 5VSB rail by time T3, then the rail will

experience a sudden step as the P-MOSFET gate is fully

enhanced. The soft start profile of the 5VDUAL may be

altered by placing a capacitor between the gate and drain of

the P-MOSFET. Adding this capacitor will increase the gate

capacitance and slow down the start of the 5VDUAL rail.

At time T4, the system has transitioned into S0 state and the

ATX supplies have begun to ramp up. With the ISL6506/B

(Figure 3), the 5VDUAL rail will begin to ramp up from the

5VATX rail through the body diode of the N-MOSFET (Q3).

The ISL6506A will already have the 5VDUAL rail in

regulation (Figure 4). At time T5, the 12VATX rail has

surpassed the 12V POR level. Time T6 is three soft start

cycles after the 12V POR level has been surpassed. At time

T6, three events occur simultaneously. The DLA pin is forced

to a high impedance state which allows the 12V rail to

enhance the two N-MOSFETs (Q1 and Q3) that connect the

ATX rails to the 3.3VDUAL and 5VDUAL rails. The 5VDLSB

pin is forced to a high impedance state which will turn the

P-MOSFET (Q2) off. Finally, the internal LDO which regulates

the 3.3VAUX rail in sleep states in put in standby mode.

T0 T1 T2 T3

T4 T5

TIME

T6

FIGURE 3. ISL6506 and ISL6506B SOFT-START INTERVAL

IN S4/S5 STATE AND S5 TO S0 TRANSITION

5VSB

(1V/DIV)

5VDUAL

(1V/DIV)

3.3VDUAL

(2V/DIV)

12VATX (2V/DIV)

5VATX (1V/DIV)

3.3VATX (1V/DIV)

0V

5VDLSB

(5V/DIV)

DLA

(10V/DIV)

T0 T1 T2 T3

T4 T5

TIME

T6

FIGURE 4. SOFT START INTERVAL FOR ISL6506A IN S4/S5

AND S5 TO S0 TRANSITION FOR ISL6506A AND

S3 TO S0 TRANSITION FOR ISL6506/A/B

Sleep to Wake State Transitions

Figures 3 and 4, starting at time T4, depict the transitions

from sleep states to the S0 wake state. Figure 3 shows the

transition of the ISL6506/B from the S4/S5 state to the S0

state. Figure 4 shows how the ISL6506/B will transition from

the S3 sleep state into S0 state. Figure 3 also shows how

the ISL6506A transitions from either S3 or S4/S5 in the S0

state. For all transitions, T4 depicts the system transition into

the S0 state. Here, the ATX supplies are enabled and begin

to ramp up. At time T5, the 12VATX rail has exceeded the

POR threshold for the ISL6506/B and ISL6506A. Three soft

start periods after time T5, at time T6, three events occur

5

5 Page | ||

| Páginas | Total 8 Páginas | |

| PDF Descargar | [ Datasheet ISL6506B.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ISL6506 | Multiple Linear Power Controller | Intersil Corporation |

| ISL6506A | Multiple Linear Power Controller | Intersil Corporation |

| ISL6506B | Multiple Linear Power Controller | Intersil Corporation |

| ISL6506BI | Multiple Linear Power Controller | Intersil |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |