|

|

PDF IS64WV12816DBLS Data sheet ( Hoja de datos )

| Número de pieza | IS64WV12816DBLS | |

| Descripción | 128K x 16 HIGH SPEED ASYNCHRONOUS CMOS STATIC RAM | |

| Fabricantes | Integrated Silicon Solution | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de IS64WV12816DBLS (archivo pdf) en la parte inferior de esta página. Total 21 Páginas | ||

|

No Preview Available !

IS61WV12816DALL/DALS

IS61WV12816DBLL/DBLS

IS64WV12816DBLL/DBLS

www.DataSheet4U.com

128K x 16 HIGH SPEED ASYNCHRONOUS

CMOS STATIC RAM

MAY 2008

FEATURES

HIGH SPEED: (IS61/64WV12816DALL/DBLL)

• High-speed access time: 8, 10, 12, 20 ns

• Low Active Power: 135 mW (typical)

• Low Standby Power: 12 μW (typical)

CMOS standby

LOW POWER: (IS61/64WV12816DALS/DBLS)

• High-speed access time: 25, 35 ns

• Low Active Power: 55 mW (typical)

• Low Standby Power: 12 μW (typical)

CMOS standby

• Single power supply

— VDD 1.65V to 2.2V (IS61WV12816DAxx)

— VDD 2.4V to 3.6V (IS61/64WV12816DBxx)

• Fully static operation: no clock or refresh

required

• Three state outputs

• Data control for upper and lower bytes

• Industrial and Automotive temperature support

• Lead-free available

DESCRIPTION

The ISSI IS61WV12816DAxx/DBxx and IS64WV12816DBxx

are high-speed, 2,097,152-bit static RAMs organized as

131,072 words by 16 bits. It is fabricated using ISSI's high-

performance CMOS technology. This highly reliable pro-

cess coupled with innovative circuit design techniques,

yields high-performance and low power consumption de-

vices.

When CE is HIGH (deselected), the device assumes a

standby mode at which the power dissipation can be

reduced down with CMOS input levels.

Easy memory expansion is provided by using Chip Enable

and Output Enable inputs, CE and OE. The active LOW

Write Enable (WE) controls both writing and reading of the

memory. A data byte allows Upper Byte (UB) and Lower

Byte (LB) access.

The IS61WV12816DAxx/DBxx and IS64WV12816DBxx are

packaged in the JEDEC standard 44-pin TSOP Type II and

48-pin Mini BGA (6mm x 8mm).

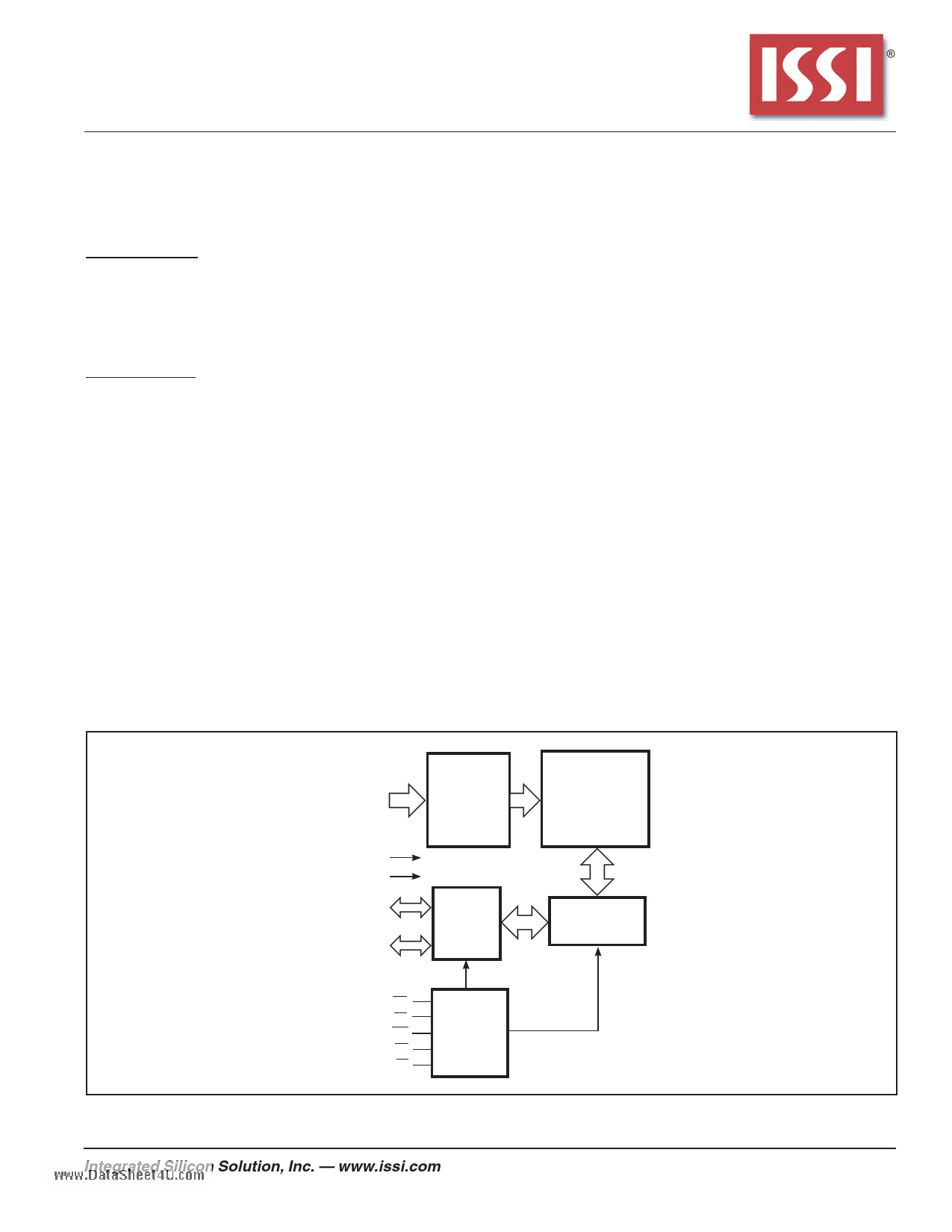

FUNCTIONAL BLOCK DIAGRAM

A0-A16

DECODER

128K x 16

MEMORY ARRAY

VDD

GND

I/O0-I/O7

Lower Byte

I/O8-I/O15

Upper Byte

I/O

DATA

CIRCUIT

COLUMN I/O

CE

OE

WE

CONTROL

CIRCUIT

UB

LB

Copyright © 2006 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time

without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to

obtain the latest version of this device specification before relying on any published information and before placing orders for products.

Integrated Silicon Solution, Inc. — www.issi.com

Rev. C

05/01/08

1

1 page

IS61WV12816DALL/DALS, IS61WV12816DBLL/DBLS,

IS64WV12816DBLL/DBLS

www.DataSheet4U.com

AC TEST CONDITIONS

Parameter

Input Pulse Level

Input Rise and Fall Times

Input and Output Timing

and Reference Level (VRef)

OutputLoad

R1 ( Ω )

R2 ( Ω )

VTM (V)

Unit

(2.4V-3.6V)

0.4V to VDD - 0.3V

1V/ ns

VDD /2

See Figures 1 and 2

1909

1105

3.0V

Unit

(3.3V + 5%)

0.4V to VDD - 0.3V

1V/ ns

VDD + 0.05

2

See Figures 1 and 2

317

351

3.3V

Unit

(1.65V-2.2V)

0.4V to VDD - 0.3V

1V/ ns

0.9V

See Figures 1 and 2

13500

10800

1.8V

AC TEST LOADS

OUTPUT

ZO = 50Ω

50Ω

VDD/2

30 pF

Including

jig and

scope

Figure 1.

VTM

R1

OUTPUT

5 pF

Including

jig and

scope

Figure 2.

R2

1

2

3

4

5

6

7

8

9

10

11

12

Integrated Silicon Solution, Inc. — www.issi.com

Rev. C

05/01/08

5

5 Page

IS61WV12816DALL/DALS, IS61WV12816DBLL/DBLS,

IS64WV12816DBLL/DBLS

www.DataSheet4U.com

AC WAVEFORMS

READ CYCLE NO. 1(1,2) (Address Controlled) (CE = OE = VIL, UB or LB = VIL)

1

ADDRESS

DOUT

t RC

PREVIOUS DATA VALID

t OHA

t AA

t OHA

DATA VALID

READ1.eps

2

3

4

READ CYCLE NO. 2(1,3)

ADDRESS

OE

CE

LB, UB

tLZCE

DOUT

tLZB

HIGH-Z

tRC

tAA tOHA

tDOE

tLZOE

tACE

tHZOE

tHZCE

tBA tRC

tHZB

DATA VALID

VDD

Supply

Current

tPU

50%

Notes:

1. WE is HIGH for a Read Cycle.

2. The device is continuously selected. OE, CE, UB, or LB = VIL.

3. Address is valid prior to or coincident with CE LOW transition.

tPD

50%

ICC

ISB

UB_CEDR2.eps

5

6

7

8

9

10

11

12

Integrated Silicon Solution, Inc. — www.issi.com

Rev. C

05/01/08

11

11 Page | ||

| Páginas | Total 21 Páginas | |

| PDF Descargar | [ Datasheet IS64WV12816DBLS.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| IS64WV12816DBLL | 128K x 16 HIGH SPEED ASYNCHRONOUS CMOS STATIC RAM | Integrated Silicon Solution |

| IS64WV12816DBLS | 128K x 16 HIGH SPEED ASYNCHRONOUS CMOS STATIC RAM | Integrated Silicon Solution |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |