|

|

PDF RTAX2000SL Data sheet ( Hoja de datos )

| Número de pieza | RTAX2000SL | |

| Descripción | RadTolerant FPGAs | |

| Fabricantes | Actel Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de RTAX2000SL (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

RTAX-S/SL RadTolerant FPGAs

www.DataSheet4U.vco5m. 3

Radiation Performance

• SEU-Hardened Registers Eliminate the Need for Triple-

Module Redundancy (TMR)

–

Immune to Single-Event

MeV-cm2/mg

Upsets

(SEU)

to

LETTH

>

37

– SEU Rate < 10-10 Errors/Bit-Day in Worst-Case

Geosynchronous Orbit

• Expected SRAM Upset Rate of <10-10 Errors/Bit-Day with

Use of Error Detection and Correction (EDAC) IP (included)

with Integrated SRAM Scrubber

– Single-Bit Correction, Double-Bit Detection

– Variable-Rate Background Refreshing

• Total Ionizing Dose Up to 300 krad (Si, Functional)

•

Single-Event

cm2/mg

Latch-Up

Immunity

(SEL)

to

LETTH

>

117

MeV-

• TM1019 Test Data Available

• Single Event Transient (SET) – No Anomalies up to 150 MHz

Processing Flows

• B-Flow – MIL-STD-883B

• E-Flow – Actel Extended Flow

• EV-Flow – Class V Equivalent Flow Processing Consistent

with MIL-PRF 38535

Prototyping Options

• Commercial Axcelerator Devices for Functional

Verification

• RTAX-S PROTO Devices with Same Functional and Timing

Characteristics as Flight Unit in a Non-Hermetic Package

RTAX-SL Low Power Option

• Offers Approximately Half the Standby Current of the

Standard RTAX-S Device at Worst-Case Conditions

Table 1 • RTAX-S/SL Family Product Profile

Device

Capacity

Equivalent System Gates

ASIC Gates

Modules

Register (R-cells)

Combinatorial (C-cells)

Flip-Flops (maximum)

Embedded RAM/FIFO (without EDAC)

Core RAM Blocks

Core RAM Bits (K = 1,024)

Clocks (segmentable)

Hardwired

Routed

I/Os

I/O Banks

User I/Os (maximum)

I/O Registers

Package

CCGA/LGA

CQFP

RTAX250S/SL

250,000

30,000

1,408

2,816

2,816

12

54 k

4

4

8

198

744

–

208, 352

Leading-Edge Performance

• High-Performance Embedded FIFOs

• 350+ MHz System Performance

• 500+ MHz Internal Performance

• 700 Mb/s LVDS Capable I/Os

Specifications

• Up to 4 Million Equivalent System Gates or 500 k

Equivalent ASIC Gates

• Up to 20,160 SEU-Hardened Flip-Flops

• Up to 840 I/Os

• Up to 540 kbits Embedded SRAM

• Manufactured on Advanced 0.15 μm CMOS Antifuse

Process Technology, 7 Layers of Metal

• Electrostatic Discharge (ESD) is 2,000 V (HBM MIL-STD-883,

TM3015)

Features

• Single-Chip, Nonvolatile Solution

• 1.5 V Core Voltage for Low Power

• Flexible, Multi-Standard I/Os:

– 1.5 V, 1.8 V, 2.5 V, 3.3 V Mixed Voltage Operation

– Bank-Selectable I/Os – 8 Banks per Chip

– Single-Ended I/O Standards: LVTTL, LVCMOS, 3.3 V PCI

– JTAG Boundary Scan Testing (as per IEEE 1149.1)

– Differential I/O Standards: LVPECL and LVDS

– Voltage-Referenced I/O Standards: GTL+, HSTL Class 1,

SSTL2 Class 1 and 2, SSTL3 Class 1 and 2

– Hot-Swap Compliant with Cold-Sparing Support

(Except PCI)

• Embedded Memory with Variable Aspect Ratio and

Organizations:

– Independent, Width-Configurable Read and Write Ports

– Programmable Embedded FIFO Control Logic

– ROM Emulation Capability

• Deterministic, User-Controllable Timing

• Unique In-System Diagnostic and Debug Capability

RTAX1000S/SL

1,000,000

125,000

6,048

12,096

12,096

36

162 k

4

4

8

418

1,548

624

352

RTAX2000S/SL

2,000,000

250,000

10,752

21,504

21,504

64

288 k

4

4

8

684

2,052

624, 1152

256, 352

RTAX4000S

4,000,000

500,000

20,160

40,320

40,320

120

540 k

4

4

8

840

2,520

1272

352

October 2008

© 2008 Actel Corporation

i

See the Actel website for the latest version of the datasheet.

All RTAX4000S information is preliminary.

1 page

Actel Extended Flow

RTAX-S/SL RadTolerant FPGAs

www.DataSheet4U.com

Table 3 • Actel Extended Flow for RTAX-S/SL 1, 2, 3, 4

Step

1

Screen

Destructive Bond Pull5

Method

2011, Condition D

2 Internal Visual

2010, Condition A

3 Serialization

4 Temperature Cycling

1010, Condition C, 10 cycles minimum

5 Constant Acceleration

2001, Y1 Orientation Only

Condition B for CQ352, LG624, LG1152

Condition D for CQ208

TBD for LG1272

6 Particle Impact Noise Detection

2020, Condition A

7 Radiographic (X-Ray)

2012, One View (Y1 Orientation) Only

8 Pre-Burn-In Electrical Parameters

In accordance with applicable Actel device

specification

9 Dynamic Burn-In

1015, Condition D,

240 hours at 125°C or 120 hours at 150°C

minimum

10 Interim (Post-Dynamic-Burn-In) Electrical In accordance with applicable Actel device

Parameters

specification

11 Static Burn-In

1015, Condition C, 72 hours at 150°C or 144

hours at 125°C minimum

12 Interim (Post-Static-Burn-In) Electrical Parameters In accordance with applicable Actel device

specification

13

Percent Defective Allowable (PDA) Calculation

5% Overall, 3% Functional Parameters at 25°C

14 Final Electrical Test4

a. Static Tests

(1) 25°C

(2) –55°C and +125°C

In accordance with applicable Actel device

specification, which includes a, b, and c:

5005, Table 1, Subgroup 1

5005, Table 1, Subgroup 2, 3

Requirement

Extended Sample

100%

100%

100%

100%

100%

100%

100%

100%

100%

All Lots

100%

b. Functional Tests

(1) 25°C

(2) –55°C and +125°C

5005, Table 1, Subgroup 7

5005, Table 1, Subgroup 8a, 8b

c. Switching Tests at 25°C

15 Seal (Fine & Gross Leak Test)

5005, Table 1, Subgroup 9

1014

100%

16 External Visual

2009

100%

Notes:

1. Actel offers Extended Flow for users requiring additional screening beyond MIL-STD-833, Class B requirement. Actel is offering this

Extended Flow incorporating the majority of the screening procedures as outlined in Method 5004 of MIL-STD-883, Class S.

2. The Quality Conformance Inspection (QCI) for Extended Flow devices still comply to MIL-STD-833, Class B requirement.

3. For CCGA devices, all Assembly/Screening/TCI testing are performed at LGA level. Only QA electrical and mechanical visual are

performed after solder column attachment.

4. RTAX-S and RTAX-SL devices have the same silicon and are distinguished by screening the ICCA current limits at 125°C final electrical

test.

5. Requirement for 100% nondestructive bond pull per Method 2003 is substituted by an extensive destructive bond pull to Method

2011 Condition D on an extended sample basis.

v5.3

v

5 Page

FCI

A[0:1]

B[0:1]

D[0:3]

DB

CFN

C-cell

FCO

C-Cell

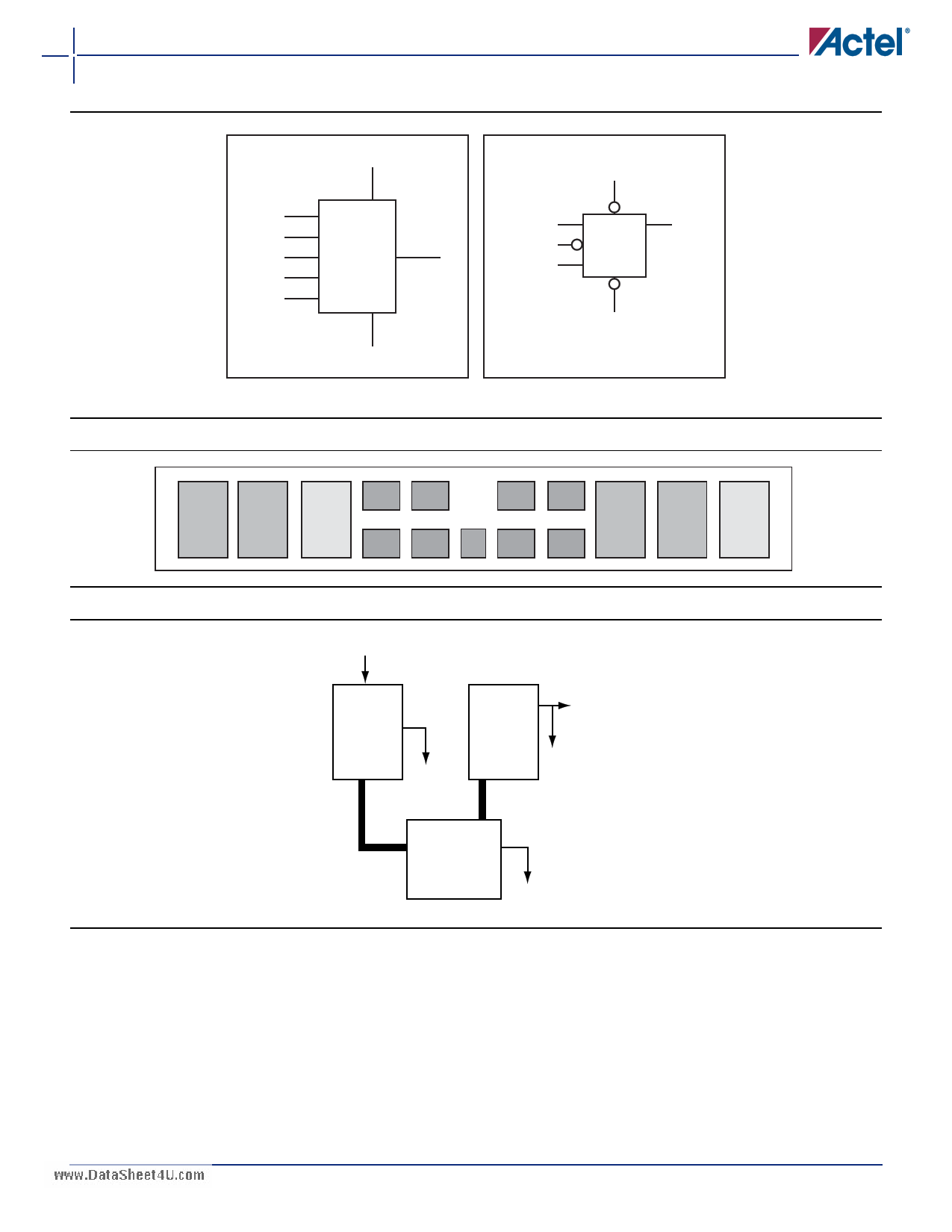

Figure 1-3 • RTAX-S/SL C-Cell and R-Cell

Y

RTAX-S/SL RadTolerant FPGAs

www.DataSheet4U.com

D PRE Q

E

CLK CLR

(Positive Edge Triggered)

R-Cell

TX TX

CC R

TX TX

CCR

RX RX B RX RX

Figure 1-4 • RTAX-S/SL SuperCluster

FCI

C-Cell

Y

C-Cell

DCOUT

Y

Figure 1-5 • RTAX-S/SL Two-Bit Carry Logic

Carry Logic

FCO

v5.3

1-3

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet RTAX2000SL.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| RTAX2000S | RadTolerant FPGAs | Actel Corporation |

| RTAX2000SL | RadTolerant FPGAs | Actel Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |