|

|

PDF ISL6217 Data sheet ( Hoja de datos )

| Número de pieza | ISL6217 | |

| Descripción | Precision Multi-Phase Buck PWM Controller | |

| Fabricantes | Intersil Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ISL6217 (archivo pdf) en la parte inferior de esta página. Total 19 Páginas | ||

|

No Preview Available !

NOT RECSOEMEMSEU®NBDSIETSDILT6UFD2OT1aER7taAPNSREhOWeDeDUtECSTIGNS

December 2006

ISL6217

FN9089.3

Precision Multi-Phase Buck PWM

Controller for Intel‚ Mobile Voltage

Positioning IMVP-IV™and IMVP-IV+™

The ISL6217 Multi-Phase Buck PWM control IC, with

integrated half bridge gate drivers, provides a precision

voltage regulation system for advanced Pentium“ IV

microprocessors in notebook computers. Two-phase

operation eases the thermal management issues and load

demand of Intel’s latest high performance processors. This

control IC also features both input voltage feed-forward and

average current mode control for excellent dynamic

response, “Loss-less” current sensing using MOSFET

RDS(ON) and user selectable switching frequencies from

250kHz to 1MHz per phase.

The ISL6217 includes a 6-bit digital-to-analog converter

(DAC) that dynamically adjusts the CORE PWM output

voltage from 0.700V to 1.708V in 16mV steps and conforms

to the Intel IMVP-IV™ and IMVP-IV+™ mobile VID

specification. The ISL6217 also has logic inputs to select

Active, Deep Sleep and Deeper Sleep modes of operation.

A precision reference, remote sensing and proprietary

architecture, with integrated processor-mode compensated

“Droop”, provide excellent static and dynamic CORE voltage

regulation.

To improve efficiency at light loading, the ISL6217 can be

configured to run in single phase PWM in ACTIVE, DEEP or

DEEPER SLEEP modes of operation.

Another feature of this IC controller is the PGOOD monitor

circuit that is held low until CORE voltage increases, during

its soft-start sequence, to within 12% of the “Boot” voltage.

This PGOOD signal is masked during VID changes. Output

Overcurrent, Overvoltage and Undervoltage are monitored

www.aDnadtarSehseueltt4iUn.tchoemconverter latching off and PGOOD signal

being held low.

The Overvoltage and Undervoltage thresholds are 112%

and 84% of the VID, Deep or Deeper Sleep setpoint,

respectively. Overcurrent protection features a 32 cycle

Overcurrent shutdown. PGOOD, Overvoltage, Undervoltage

and Overcurrent provide monitoring and protection for the

microprocessor and power system. The ISL6217 IC is

available in a 38 lead TSSOP.

Features

• IMVP-IV™ and IMVP-IV+™ Compliant CORE Regulator

• Single and/or Two-phase Power Conversion

• “Loss-less” Current sensing for improved efficiency and

reduced board area

− Optional Discrete Precision Current Sense Resistor

• Internal Gate-Drive and Boot-Strap Diodes

• Precision CORE Voltage Regulation

− 0.8% system accuracy over temperature

• 6-Bit Microprocessor Voltage Identification Input

• Programmable “Droop” and CORE Voltage Slew Rate to

comply with IMVP-IV™ and IMVP-IV+™ specification

• Direct Interface with System Logic (STP_CPU# and

DPRSLPVR) for Deep and Deeper Sleep modes of

operation

• Easily Programmable voltage setpoints for Initial “Boot”,

Deep Sleep and Deeper Sleep Modes

• Excellent Dynamic Response

− Combined Voltage Feed-Forward and Average

Current Mode Control

• Overvoltage, Undervoltage and Overcurrent Protection

• Power-Good Output with internal blanking during VID and

mode changes

• User programmable Switching Frequency of 250kHz -

1MHz per phase

• Pb-Free Plus Anneal Available (RoHS Compliant)

Ordering Information

PART NUMBER TEMP (°C)

PACKAGE

ISL6217CV

-10 to 85 38 Ld TSSOP

ISL6217CV-T 38 Ld TSSOP Tape and Reel

ISL6217CVZ

(Note 1)

-10 to 85

38 Ld TSSOP

(Pb-free)

ISL6217CVZ-T

(Note 1)

38 Ld TSSOP Tape and Reel

(Pb-free)

PKG.

DWG. #

M38.173

M38.173

M38.173

M38.173

ISL6217CVZA

(Note 1)

-10 to 85

38 Ld TSSOP

(Pb-free)

M38.173

ISL6217CVZA-T 38 Ld TSSOP Tape and Reel

(Note 1)

(Pb-free)

M38.173

NOTES:

1. Intersil Pb-free plus anneal products employ special Pb-free

material sets; molding compounds/die attach materials and 100%

matte tin plate termination finish, which are RoHS compliant and

compatible with both SnPb and Pb-free soldering operations. Intersil

Pb-free products are MSL classified at Pb-free peak reflow

temperatures that meet or exceed the Pb-free requirements of

IPC/JEDEC J STD-020.

1 CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143|Intersil (and design) is a registered trademark of Intersil Americas Inc.

Copyright © Intersil Americas Inc. 2006. All Rights Reserved

All other trademarks mentioned are the property of their respective owners

1 page

ISL6217

Absolute Voltage Ratings

Supply Voltage, VDD, VDDP .....................................-0.3-+7V

Battery Voltage, VBAT.................................................... +30V

Boot1,2 and UGATE1,2 .................................................. +35V

Phase1,2 and ISEN1,2 ................................................... +30V

Boot1,2 with respect to Phase1,2 .................................. +6.5V

UGATE1,2 ................... (Phase1,2 - 0.3V) to (Boot1,2 + 0.3V)

PHASE 1,2 Voltage..............GND- 0.3V (DC) to VBOOT + 0.3V

...........GND - 5V (<100ns Pulse Width, 10µJ) to VBOOT + 0.3V

ALL OTHER PINS ............................... -0.3V to (VDD + 0.3V)

Thermal Information

Thermal Resistance (Typical, Note 1)

θJA (oC/W)

TSSOP Package (Note 1) ................................................ 72°

Maximum Operating Junction Temperature ..................125oC

Maximum Storage Temperature Range ..........-65oC to 150oC

Maximum Lead Temperature (Soldering 10s) ...............300oC

Recommended Operating Conditions

Supply Voltage, VDD, VDDP ....................................+5V ±5%

Battery Voltage, VBAT........................................+5.6V to 25V

Ambient Temperature ....................................... -10°C to 85°C

Junction Temperature..................................... -10°C to 125°C

CAUTION: Stress above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and

operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied.

NOTE:

1) θJA is measured with the component mounted on a high effective thermal conductivity test board in free air.

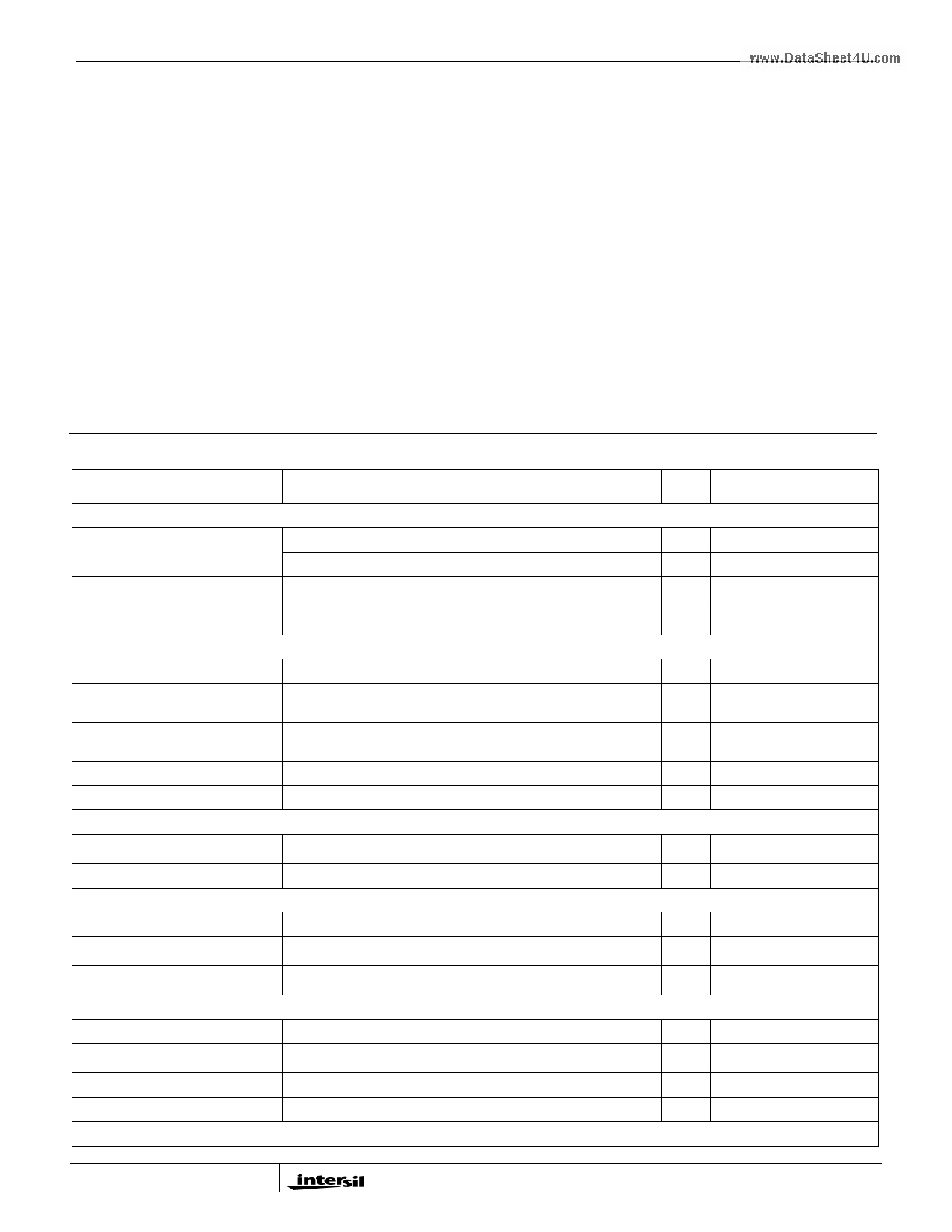

Electrical Specifications Operating Conditions: VDD = 5V, TA = -10°C to 85°C, Unless Otherwise Specified

PARAMETER

TEST CONDITIONS

MIN TYP

INPUT POWER SUPPLY

Input Supply Current, I(VDD)

POR (Power-On Reset) Threshold

REFERENCE AND DAC

System Accuracy

DAC (VID0 - VID5) Input Low

Voltage

DAC (VID0 - VID5) Input High

www.DVaotlataSgheeet4U.com

Maximum Output Voltage

Minimum Output Voltage

CHANNEL GENERATOR

Frequency, FSW

Adjustment Range

ERROR AMPLIFIER

DC Gain

Gain-Bandwidth Product

Slew Rate

ISEN

Full Scale Input Current

Overcurrent Threshold

Soft Start Current

Droop Current

GATE DRIVER

EN = 3.3V, DSEN# = 0, DRSEN = 0, PWRCH = 0

EN = 0V

VDD Rising

VDD Falling

Percent system deviation from programmed VID Codes @ 1.356

DAC Programming Input Low Threshold Voltage

DAC Programming Input High Threshold Voltage

RFset = 243K, ±1%

CL = 20pF

CL = 20pF

ROCSET =124K

SOFT = 0V

ISEN = 32µA

- 1.4

-1

4.35 4.45

4.05 4.20

-0.8 -

--

0.7 -

- 1.708

- 0.70

225 250

0.25 -

- 100

- 18

- 4.0

- 32

- 64

- 31

26.5 28

MAX

-

-

4.5

4.40

0.8

0.3

-

-

-

275

1.0

-

-

-

-

-

-

29.5

UNITS

mA

µA

V

V

%

V

V

V

V

kHz

MHz

dB

MHz

V/µs

µA

µA

µA

µA

5

5 Page

VID[0..5]

V CC_CORE

Current VID Code

< 600ns

Current Voltage Level

ISL6217

New VID Code

New Voltage Level

PGOOD

HIGH

FIGURE 5. PLOT SHOWING TIMING OF VID CODE CHANGES AND CORE VOLTAGE SLEWING AS WELL AS PGOOD MASKING

VID[0..5]

VID Code remains the same

STP_CPU#

(DSEN#)

V CC_CORE

VID Command Voltage

<30us

VDeep Sleep

FIGURE 6. CORE VOLTAGE SLEWING TO 98.8% OF PROGRAMMED VID VOLTAGE FOR A LOGIC LEVEL LOW ON DSEN

VID[0..5]

VID Code remains the same

STP_CPU#

(DSEN#)

DPRSLPVR

(DRSEN)

www.DataSVheCeCt4_UC.cOomRE

V Deep Sleep

V Deeper Sleep

Deeper Sleep Mode

Short DPRSLP causes

VCC-CORE to ramp up

FIGURE 7. VCORE RESPONSE FOR DEEPER SLEEP COMMAND

A logic low signal present on STPCPU# (pin DSEN#), with

a logic low signal on DPRSLPVR (pin DRSEN), signals the

ISL6217 to reduce the CORE output voltage to the Deep

Sleep level, the voltage on the DSV pin.

A logic high on DPRSLPVR, (pin DRSEN) with a logic low

signal on STPCPU# (pin DSEN#), signals the ISL6217

controller to further reduce the CORE output voltage to the

Deeper Sleep level, which is the voltage on the DRSV pin.

Deep Sleep and Deeper Sleep voltage levels are

programmable and are explained in the “STV, DSV and

DRSV” section of this document.

Deep Sleep Enable-DSEN# and Deeper Sleep

Enable - DRSEN

Table 2 shows logic states controlling modes of operation.

Figure 6 and Figure 7 shows the timing for transitions

11

entering and exiting Deep Sleep Mode and Deeper Sleep

Mode. This is controlled by the system signals STPCPU#

and DPRSLPVR. ISL6217 pins DSEN#, (Deep Sleep

Enable #) and DRSEN, (Deeper Sleep Enable), are

connected to these 2 signals, respectively.

When DSEN# is logic high, and DRSEN is logic low, the

controller will operate in Active Mode and regulate the

output voltage to the VID commanded DAC voltage, minus

the voltage “Droop” as determined by the load current.

Voltage “Droop” is the reduction of output voltage

proportional to output current.

When a logic low is detected at the DSEN# and DRSEN

pins, the controller will regulate the output voltage to the

voltage seen on the DSV pin minus “Droop”. If the PWRCH

pin is connected to the DSEN# pin then the controller will

also switch to single channel operation.

11 Page | ||

| Páginas | Total 19 Páginas | |

| PDF Descargar | [ Datasheet ISL6217.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ISL6210 | Dual Synchronous Rectified MOSFET Drivers | Intersil Corporation |

| ISL6211 | Crusoe Processor Core-Voltage Regulator | Intersil Corporation |

| ISL6217 | Precision Multi-Phase Buck PWM Controller | Intersil Corporation |

| ISL6217A | Precision Multi-Phase Buck PWM Controller | Intersil Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |