|

|

PDF UPD161831 Data sheet ( Hoja de datos )

| Número de pieza | UPD161831 | |

| Descripción | 240/244-OUTPUT TFT-LCD SOURCE DRIVER | |

| Fabricantes | NEC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de UPD161831 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

PRELIMINARY PRODUCT INFORMATION

MOS INTEGRATED CIRCUIT

µPD161831

240/244-OUTPUT TFT-LCD SOURCE DRIVER WITH TIMING GENERATOR

(COMPATIBLE WITH 64-GRAY SCALES)

DESCRIPTION

The µPD161831 is a source driver for LIPS TFTs with on-chip timing generator and featuring 240/244 outputs. Data

input as 6-bit x 3-dot digital data is output as 64 γ -corrected values using an internal D/A converter, achieving

260,000-color (full-color) display.

FEATURES

• CMOS level input

• 240/244 outputs (R, G, B output)

• Input of 6 bits (gray-scale data) by 3 dots

• Capable of outputting 64 values by means of 5 external power modules and a D/A converter

• Output dynamic range: VSS + 0.05 V to VS – 0.05 V

• High-speed data transfer: fCLK = 20 MHz MAX. (during 2-times data transfer when operating at VCC = 2.5 V. During

1-time data transfer 10 MHz MAX.)

• High-speed data transfer: fCLK = 16 MHz MAX. (during 2-times data transfer when operating at VCC = 2.2 V. During

1-time data transfer 8 MHz MAX.)

• On-chip power supplies (driver power supply, gate top power supply, gate bottom power supply)

• Logic power supply voltage (VCC): 2.2 to 3.6 V

• DC/DC reference power supply (VDC): 2.5 to 3.6 V

• On-chip timing generator (Outputs R, G, B switching signal to panel. Outputs gate control signal.)

• On-chip 8-bit serial interface (applied to SPI)

www.DataOSRheDetE4UR.IcNomG INFORMATION

Part Number

µPD161831P

Package

Chip

Remark Purchasing the above chip entail the exchange of documents such as a separate memorandum or product

quality, so please contact one of our sales representatives.

The information contained in this document is being issued in advance of the production cycle for the

device. The parameters for the device may change before final production or NEC Corporation, at its own

discretion, may withdraw the device prior to its production.

Not all devices/types available in every country. Please check with local NEC representative for

availability and additional information.

Document No. S16269EJ2V0PM00 (2nd edition)

Date Published October 2002 NS CP (K)

Printed in Japan

The mark 5 shows major revised points.

©

2002

1 page

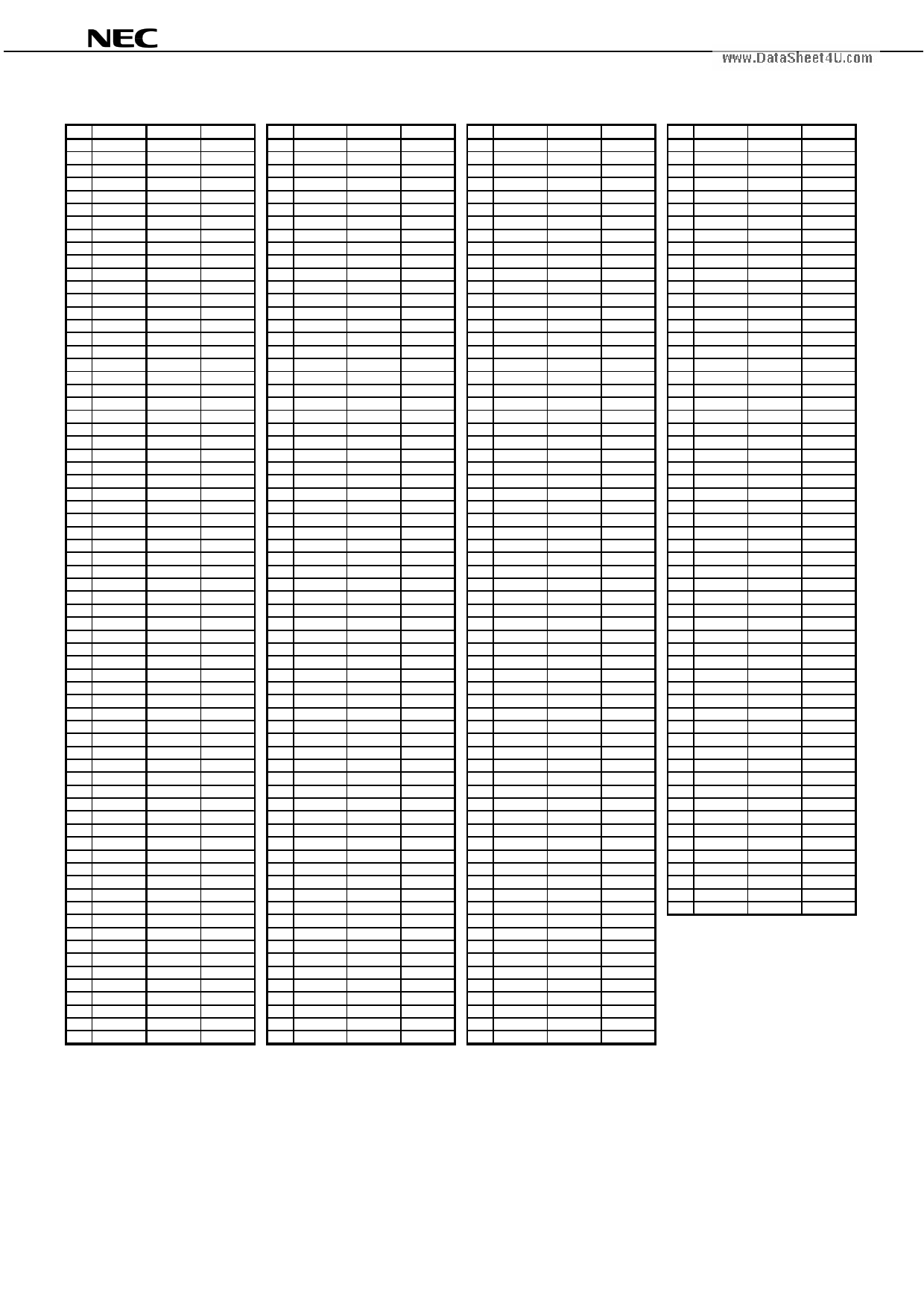

µPD161831

No. PADName µ X[µm]

281 Dummy

-6780.00

282 Dummy

-6840.00

283 BSW_O -6900.00

284 BSW_O -6960.00

285 GSW_O -7080.00

286 GSW_O -7140.00

287 RSW_O -7260.00

288 RSW_O -7320.00

289 EXT3_O -7440.00

290 EXT3_O -7500.00

291 EXT2_O -7620.00

292 EXT2_O -7680.00

293 EXT1_O -7800.00

294 EXT1_O -7860.00

295 VSS2

-7980.00

296 VSS2

-8040.00

297 VSS2

-8100.00

298 VSS2

-8160.00

299 VSS1

-8280.00

300 VSS1

-8340.00

301 VSS1

-8400.00

302 VSS1

-8460.00

303 VDD2

-8580.00

304 VDD2

-8640.00

305 VDD2

-8700.00

306 VDD2

-8760.00

307 GOE2_O -8880.00

308 GOE2_O -8940.00

309 GOE2_O -9000.00

310 GOE2_O -9060.00

311 GOE1_O -9180.00

312 GOE1_O -9240.00

313 GR/L_O -9360.00

314 GR/L_O -9420.00

315 GCLK_O -9540.00

316 GCLK_O -9600.00

317 GSTB_O -9720.00

318 GSTB_O -9780.00

319 Dummy

-9840.00

320 Dummy -10677.00

321 Dummy -10737.00

322 Dummy -10797.00

323 Dummy -10788.00

324 Dummy -10688.01

325 Dummy -10588.02

326 Dummy

-9879.99

327 VSS

-9780.00

328 VSS

-9705.00

329 VSS

-9630.00

www.D3333a01taShVVeSSeSSt4U.com--99545850..0000

332 VS

-9380.01

333 VS

-9305.01

334 VS

-9230.01

335 VS

-9155.01

336 VS

-9080.01

337 VGD

-8980.02

338 VGD

-8905.02

339 VGD

-8830.02

340 VGD

-8755.02

341 VR

-8655.03

342 VR

-8580.03

343 VR

-8505.03

344 VR

-8430.03

345 VDC

-8330.04

346 VDC

-8255.04

347 VDC

-8180.04

348 VDC

-8105.04

349 VDC

350 VDC

-8030.04

-7955.04

Y [µm]

594.99

594.99

594.99

594.99

594.99

594.99

594.99

594.99

594.99

594.99

594.99

594.99

594.99

594.99

594.99

594.99

594.99

594.99

594.99

594.99

594.99

594.99

594.99

594.99

594.99

594.99

594.99

594.99

594.99

594.99

594.99

594.99

594.99

594.99

594.99

594.99

594.99

594.99

594.99

594.99

594.99

594.99

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

Table 2–1. Pad Layout (2/2)

No. PADName

351 VDC

352 VDC2

353 VDC2

354 VDC2

355 VDC2

356 VDC2

357 VDC2

358 VDC2

359 C1+

360 C1+

361 C1+

362 C1+

363 C1+

364 C1+

365 C1+

366 C1-

367 C1-

368 C1-

369 C1-

370 C1-

371 C1-

372 C1-

373 C2+

374 C2+

375 C2+

376 C2+

377 C2+

378 C2+

379 C2+

380 C2-

381 C2-

382 C2-

383 C2-

384 C2-

385 C2-

386 C2-

387 C3+

388 C3+

389 C3+

390 C3-

391 C3-

392 C3-

393 C4+

394 C4+

395 C4+

396 C4-

397 C4-

398 C4-

399 C5+

400 C5+

401 C5+

402 C5-

403 C5-

404 C5-

405 DCCLK

406 VDD2

407 VDD2

408 VSS1

409 VSS1

410 VSS2

411 VSS2

412 TEST_VCLAMP

413 TEST_VCLAMP

414 TEST_COM2

415 TEST_COM2

416 BGR_O

417 MVS

418 MVS

419 Dummy

420 Dummy

X [µm]

-7880.04

-7780.05

-7705.05

-7630.05

-7555.05

-7480.05

-7405.05

-7330.05

-7230.06

-7155.06

-7080.06

-7005.06

-6930.06

-6855.06

-6780.06

-6680.07

-6605.07

-6530.07

-6455.07

-6380.07

-6305.07

-6230.07

-6130.08

-6055.08

-5980.08

-5905.08

-5830.08

-5755.08

-5680.08

-5580.09

-5505.09

-5430.09

-5355.09

-5280.09

-5205.09

-5130.09

-5030.10

-4955.10

-4880.10

-4780.11

-4705.11

-4630.11

-4530.12

-4455.12

-4380.12

-4280.13

-4205.13

-4130.13

-4030.14

-3955.14

-3880.14

-3780.15

-3705.15

-3630.15

-3530.16

-3430.17

-3355.17

-3255.18

-3180.18

-3080.19

-3005.19

-2905.20

-2830.20

-2730.21

-2655.21

-2555.22

-2455.23

-2380.23

-2280.24

-2180.25

Y [µm]

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

No. PADName

421 Dummy

422 Dummy

423 Dummy

424 Dummy

425 Dummy

426 Dummy

427 VCC

428 VCC

429 VCC

430 VCC

431 VSS

432 VSS

433 VSS

434 VSS

435 VSS

436 STHR

437 GOE2_I

438 GOE1_I

439 GSTB_I

440 GCLK_I

441 STB

442 AP

443 POL

444 TCON

445 PVCC

446 OSEL

447 VCSEL

448 GAM

449 MAS/SLV

450 SCLEG1

451 SCLEG0

452 CKS

453 HSEG

454 VSEG

455 PVSS

456 EXT3_I

457 EXT2_I

458 EXT1_I

459 BSW_I

460 GSW_I

461 RSW_I

462 Dummy

463 Dummy

464 Dummy

465 Dummy

466 Dummy

467 /RESET

468 A0

469 CS2

470 CS1

471 SCLK_SUB

472 SOSUB

473 LCDCS

474 LCDCS

475 SCLK

476 SCLK

477 SI

478 SI

479 SO

480 SO

481 VSYNC

482 HSYNC

483 HSYNC

484 DCK

485 DCK

486 Dummy

487 Dummy

488 Dummy

489 Dummy

490 Dummy

X[µm]

-2080.26

-1980.27

-1880.28

-1780.29

-1680.30

-1580.31

-1480.32

-1405.32

-1330.32

-1255.32

-1155.33

-1080.33

-1005.33

-930.33

-855.33

-755.34

-655.35

-555.36

-455.37

-355.38

-255.39

-155.40

-55.41

44.58

144.57

244.56

344.55

444.54

544.53

644.52

744.51

844.50

944.49

1044.48

1144.47

1244.46

1344.45

1444.44

1544.43

1644.42

1744.41

1844.40

1944.39

2044.38

2144.37

2244.36

2344.35

2444.34

2544.33

2644.32

2744.31

2844.30

2944.29

3019.29

3119.28

3194.28

3294.27

3369.27

3469.26

3544.26

3644.25

3744.24

3819.24

3919.23

3994.23

4094.22

4194.21

4294.20

4394.19

4494.18

Y [µm]

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

No. PADName

491 D25

492 D24

493 D23

494 D22

495 D21

496 D20

497 D15

498 D14

499 D13

500 D12

501 D11

502 D10

503 D05

504 D04

505 D03

506 D02

507 D01

508 D00

509 STHL

510 STHL

511 TESTOUT

512 TESTIN4

513 TESTIN3

514 TESTIN2

515 TESTIN1

516 V4

517 V4

518 V3

519 V3

520 V2

521 V2

522 V1

523 V1

524 V0

525 V0

526 Dummy

527 Dummy

528 Dummy

529 Dummy

530 Dummy

531 Dummy

532 Dummy

533 COMDCSL

534 COMDCIN

535 COMDCIN

536 VCOMH

537 VCOMH

538 VCOMH

539 VCOMH

540 COMDC

541 COMDC

542 COMC

543 COMC

544 COMC

545 COMC

546 COMC

547 Dummy

548 Dummy

549 Dummy

550 Dummy

X[µm]

4594.17

4694.16

4794.15

4894.14

4994.13

5094.12

5194.11

5294.10

5394.09

5494.08

5594.07

5694.06

5794.05

5894.04

5994.03

6094.02

6194.01

6294.00

6393.99

6468.99

6568.98

6668.97

6768.96

6868.95

6968.94

7068.93

7143.93

7243.92

7318.92

7418.91

7493.91

7593.90

7668.90

7768.89

7843.89

7943.88

8043.87

8143.86

8243.85

8343.84

8443.83

8543.82

8643.81

8743.80

8818.80

8918.79

8993.79

9068.79

9143.79

9243.78

9318.78

9418.77

9493.77

9568.77

9643.77

9718.77

9818.76

10588.02

10688.01

10788.00

Y [µm]

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

-607.50

Preliminary Product Information S16269EJ2V0PM

5

5 Page

µPD161831

3.5 Control Pins when Timing Generator Function Not Used, and Other Pins

Pin Symbol

Pin Name

Pin Name I/O

Description

STHR

Right shift start 436

I/O Start pulse I/O pin during cascade connection. When an H level is read at

pulse I/O

the rising edge of CLK, fetching of display data starts.

STHL

Left shift start

509, 510

I/O In the case of right shift, STHR = input and STHL = output.

pulse I/O

In the case of left shift, STHL = input and STHR = output.

STB

Latch input

441

Input This is the timing signal at which the contents of the data register are

latched. When an H level is read at the rising edge of CLK, the contents of

the data register are latched and transferred to the D/A converter, and an

analog voltage is output according to the display data. Even after STB

fetch, do not stop CLK because the internal operation is performed using

CLK. At the rising edge of STB, the content of the shift register are

cleared. After one pulse is input at startup, the operation becomes normal.

At the rising edge of STB, the output switch is switched OFF. For the STB

input timing, refer to 5. TIMING GENERATOR NON-USE FUNCTION.

AP

Output SW

442

Input Switches the BIAS circuit ON/OFF and the output switch and amplifier ON.

ON/OFF

The period during which AP is H is the amplifier circuit setting period and

the liquid crystal drive period. At the falling edge of AP, the amplifier output

and output switch go ON and liquid crystal driving starts.

At the rising edge of STB, the output switch is switched to OFF ad the

output becomes Hi-Z.

POL

Polarity

inversion signal

443

Input Inverts the output polarity. At the siring edge of RSEL, the polarity inversion

signal data is fetched internally. The γ -resistor is switched according to the

positive and negative polarity.

POL = L: Negative polarity (common high output)

POL = H: Positive polarity (common low output)

3.6 Back Panel LCD Controller Driver Control Pins

Pin Symbol

Pin Name

Pin Name I/O

Description

/CS1

Back panel LCD 470

chip select

Output Active-low chip select signal to the back panel LCD controller driver.

CS2

www.DataSheet4U.com

SCLK_SUB

Back panel LCD

chip select

Serial clock to

the back panel

LCD

469

471

Output Active-high chip select signal to the back panel LCD controller driver.

Output Back panel LCD serial data output.

SO_SUB

Outputs serial

data to the back

panel LCD

472

Output Outputs serial data to the back panel LCD controller driver.

A0

Back panel LCD 468

Output Controls data/command to the back panel LCD controller driver.

data/command

control

Preliminary Product Information S16269EJ2V0PM

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet UPD161831.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| UPD161830 | 240-OUTPUT TFT-LCD SOURCE DRIVER | NEC |

| UPD161831 | 240/244-OUTPUT TFT-LCD SOURCE DRIVER | NEC |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |