|

|

PDF ISL6261 Data sheet ( Hoja de datos )

| Número de pieza | ISL6261 | |

| Descripción | Single Phase Core Regulator | |

| Fabricantes | Intersil | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ISL6261 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

®

Data Sheet

September 27, 2006

ISL6261

FN9251.1

Single-Phase Core Regulator for IMVP-6®

Mobile CPUs

The ISL6261 is a single-phase buck regulator implementing

lntel® IMVP-6® protocol, with embedded gate drivers.

The heart of the ISL6261 is the patented R3 Technology™,

Intersil’s Robust Ripple Regulator modulator. Compared with

the traditional multi-phase buck regulator, the R3

Technology™ has faster transient response. This is due to

the R3 modulator commanding variable switching frequency

during a load transient.

lntel® Mobile Voltage Positioning (IMVP) is a smart voltage

regulation technology effectively reducing power dissipation

in lntel® Pentium processors. To boost battery life, the

ISL6261 supports DPRSLRVR (deeper sleep) function and

maximizes the efficiency via automatically changing

operation modes. At heavy load in the active mode, the

regulator commands the continuous conduction mode

(CCM) operation. When the CPU enters deeper sleep mode,

the ISL6261 enables diode emulation to maximize the

efficiency at light load. Asserting the FDE pin of the ISL6261

in deeper sleep mode will further decrease the switching

frequency at light load and increase the regulator efficiency.

A 7-bit digital-to-analog converter (DAC) allows dynamic

adjustment of the core output voltage from 0.300V to 1.500V.

The ISL6261 has 0.5% system voltage accuracy over

temperature.

A unity-gain differential amplifier provides remote voltage

sensing at the CPU die. This allows the voltage on the CPU

www.dDiaetatoShbeeeta4cUc.ucoramtely measured and regulated per lntel®

IMVP-6 specification. Current sensing can be implemented

through either lossless inductor DCR sensing or precise

resistor sensing. If DCR sensing is used, an NTC thermistor

network will thermally compensates the gain and the time

constant variations caused by the inductor DCR change.

Features

• Precision single-phase CORE voltage regulator

- 0.5% system accuracy over temperature

- Enhanced load line accuracy

• Internal gate driver with 2A driving capability

• Microprocessor voltage identification input

- 7-Bit VID input

- 0.300V to 1.500V in 12.5mV steps

- Support VID change on-the-fly

• Multiple current sensing schemes supported

- Lossless inductor DCR current sensing

- Precision resistive current sensing

• Thermal monitor

• User programmable switching frequency

• Differential remote voltage sensing at CPU die

• Overvoltage, undervoltage, and overcurrent protection

• Pb-free plus anneal available (RoHS compliant)

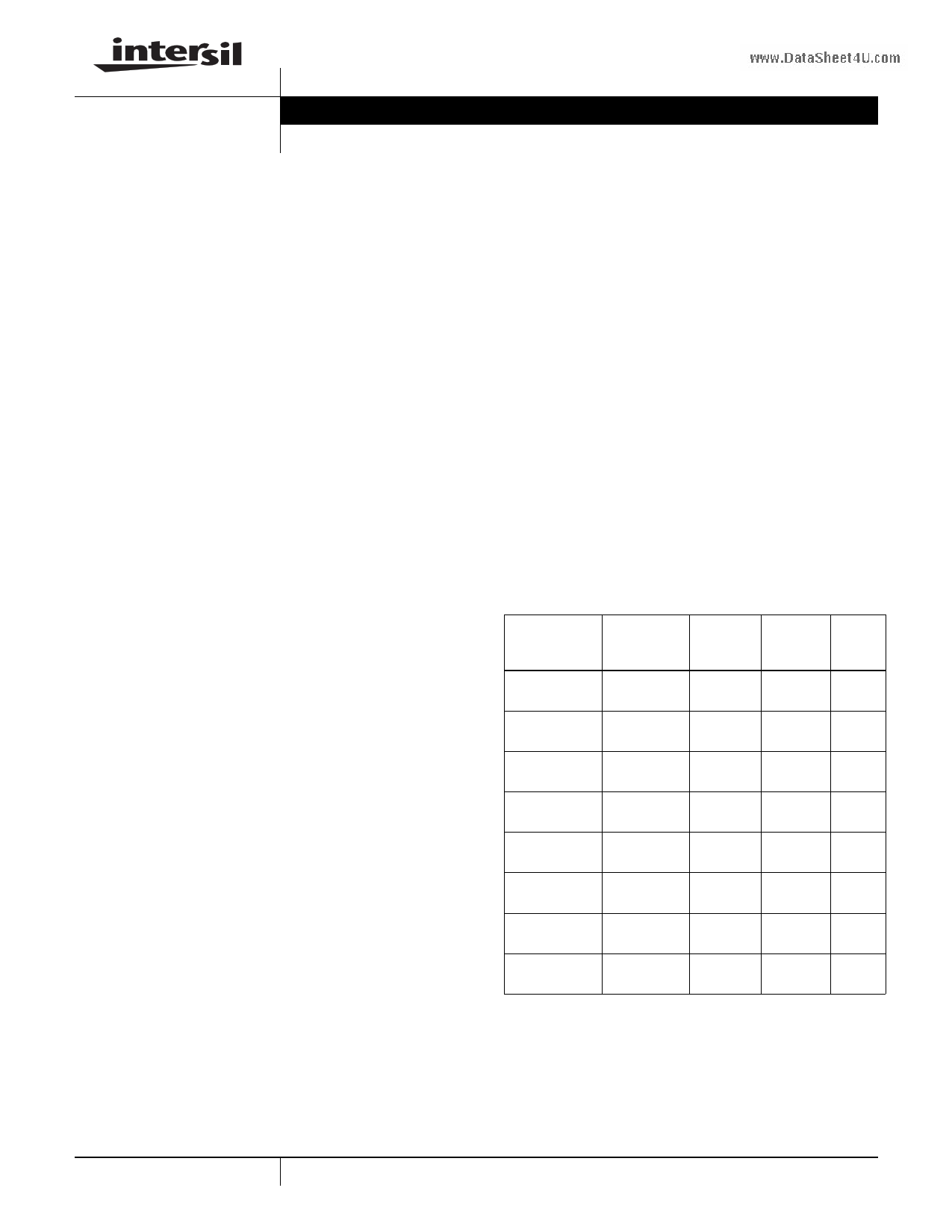

Ordering Information

PART NUMBER PART

(NOTE)

MARKING

TEMP

RANGE

(°C)

PACKAGE PKG.

(Pb-FREE) DWG. #

ISL6261CRZ

ISL6261CRZ -10 to +100 40 Ld 6x6 L40.6x6

QFN

ISL6261CRZ-T ISL6261CRZ -10 to +100 40 Ld 6x6 L40.6x6

QFN, T&R

ISL6261CR7Z ISL6261CR7Z -10 to +100 48 Ld 7x7 L48.7x7

QFN

ISL6261CR7Z-T ISL6261CR7Z -10 to +100 48 Ld 7x7 L48.7x7

QFN, T&R

ISL6261IRZ

ISL6261IRZ -40 to +100 40 Ld 6x6 L40.6x6

QFN

ISL6261IRZ-T ISL6261IRZ -40 to +100 40 Ld 6x6 L40.6x6

QFN, T&R

ISL6261IR7Z ISL6261IR7Z -40 to +100 48 Ld 7x7 L48.7x7

QFN

ISL6261IR7Z-T ISL6261IR7Z -40 to +100 48 Ld 7x7 L48.7x7

QFN, T&R

NOTE: Intersil Pb-free plus anneal products employ special Pb-free

material sets; molding compounds/die attach materials and 100%

matte tin plate termination finish, which are RoHS compliant and

compatible with both SnPb and Pb-free soldering operations. Intersil

Pb-free products are MSL classified at Pb-free peak reflow

temperatures that meet or exceed the Pb-free requirements of

IPC/JEDEC J STD-020.

1 CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774 | Intersil (and design) is a registered trademark of Intersil Americas Inc.

Copyright Intersil Americas Inc. 2006. All Rights Reserved. R3 Technology™ is a trademark of Intersil Americas Inc.

All other trademarks mentioned are the property of their respective owners.

1 page

ISL6261

Electrical Specifications VDD = 5V, TA = -10°C to +100°C, Unless Otherwise Specified. (Continued)

PARAMETER

SYMBOL

TEST CONDITIONS

MIN

Leakage Current on VR_ON and

PGD_IN

Leakage Current on DPRSLPVR

DAC(VID0-VID6), PSI# and

DPRSTP# Input Low

IIL

IIH

IIL_DPRSLP

IIH_DPRSLP

VIL(1.0V)

Logic input is low

Logic input is high

DPRSLPVR logic input is low

DPRSLPVR logic input is high

-1

-

-1

-

-

DAC(VID0-VID6), PSI# and

DPRSTP# Input High

VIH(1.0V)

0.7

Leakage Current of DAC(VID0-

VID6) and DPRSTP#

THERMAL MONITOR

IIL DPRSLPVR logic input is low

IIH DPRSLPVR logic input is high

-1

-

NTC Source Current

NTC = 1.3V

53

Over-temperature Threshold

V(NTC) falling

1.17

VR_TT# Low Output Resistance

CLK_EN# OUTPUT LEVELS

RTT I = 20mA

-

CLK_EN# High Output Voltage

VOH 3V3 = 3.3V, I = -4mA

CLK_EN# Low Output Voltage

VOL

ICLK_EN# = 4mA

NOTES:

3. Guaranteed by characterization.

4. Guaranteed by design.

2.9

-

TYP

0

0

0

0.45

-

-

0

0.45

60

1.2

5

3.1

0.18

MAX

-

1

-

1

0.3

-

-

1

67

1.25

9

-

0.4

UNITS

μA

μA

μA

μA

V

V

μA

μA

µA

V

V

V

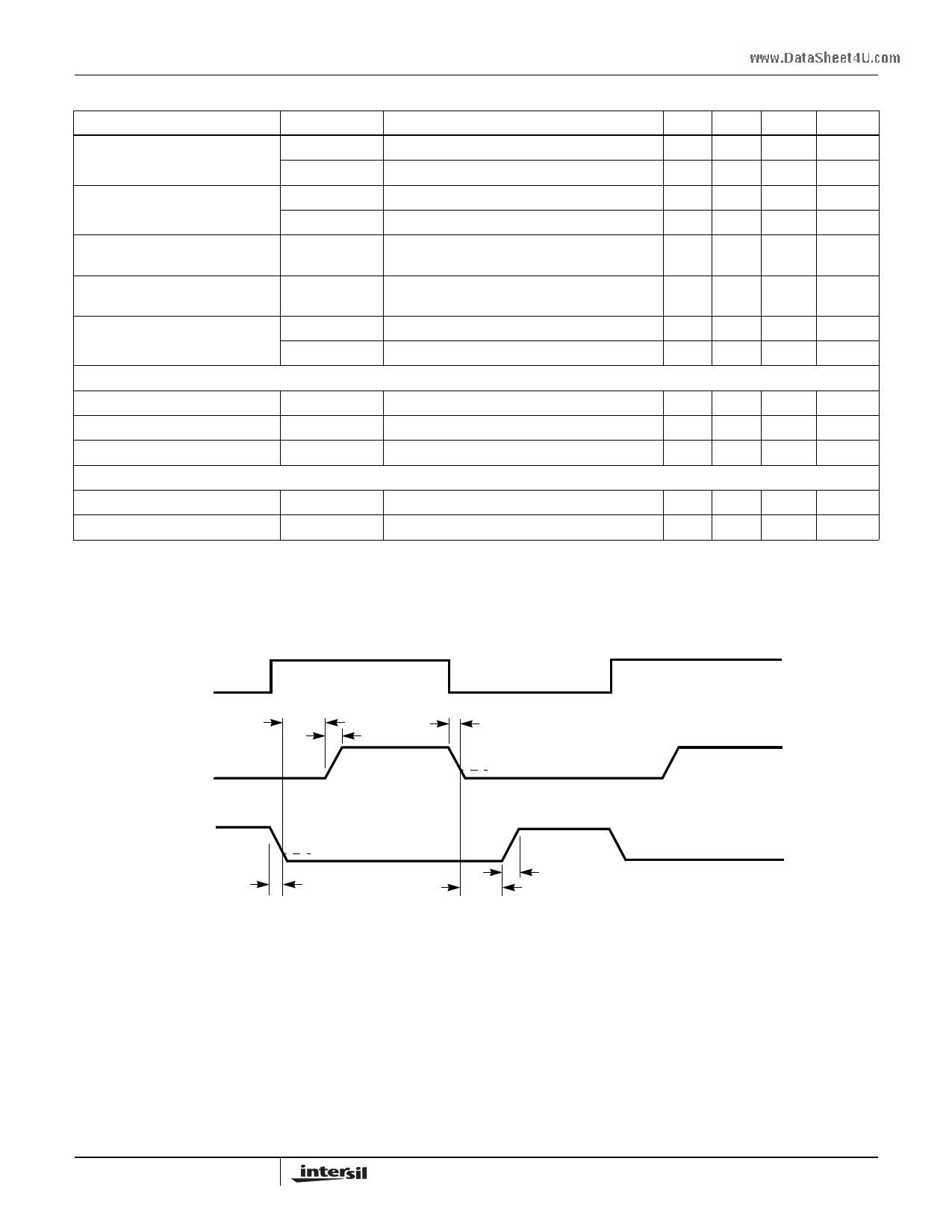

Gate Driver Timing Diagram

PWM

www.DataSheet4U.com

UGATE

tPDHU

tRU

tFU

1V

LGATE

tFL

1V

tPDHL

tRL

5 FN9251.1

September 27, 2006

5 Page

ISL6261

Theory of Operation

The ISL6261 is a single-phase regulator implementing Intel®

IMVP-6® protocol and includes an integrated gate driver for

reduced system cost and board area. The ISL6261 IMVP-6®

solution provides optimum steady state and transient

performance for microprocessor core voltage regulation

applications up to 25A. Implementation of diode emulation

mode (DEM) operation further enhances system efficiency.

The heart of the ISL6261 is the patented R3 Technology™,

Intersil’s Robust Ripple Regulator modulator. The R3™

modulator combines the best features of fixed frequency and

hysteretic PWM controllers while eliminating many of their

shortcomings. The ISL6261 modulator internally synthesizes

an analog of the inductor ripple current and uses hysteretic

comparators on those signals to establish PWM pulses.

Operating on the large-amplitude and noise-free synthesized

signals allows the ISL6261 to achieve lower output ripple

and lower phase jitter than either conventional hysteretic or

fixed frequency PWM controllers. Unlike conventional

hysteretic converters, the ISL6261 has an error amplifier that

allows the controller to maintain 0.5% voltage regulation

accuracy throughout the VID range from 0.75V to 1.5V.

The hysteretic window voltage is with respect to the error

amplifier output. Therefore the load current transient results

in increased switching frequency, which gives the R3™

regulator a faster response than conventional fixed

frequency PWM regulators.

Start-up Timing

With the controller’s VDD pin voltage above the POR

threshold, the start-up sequence begins when VR_ON

exceeds the 3.3V logic HIGH threshold. In approximately

100μs, SOFT and VO start ramping to the boot voltage of

1.2V. At startup, the regulator always operates in continuous

www.cDuartraeSnhtemeto4Ude.co(CmCM), regardless of the control signals.

During this interval, the SOFT cap is charged by a 41μA

current source. If the SOFT capacitor is 20nF, the SOFT

ramp will be 2mV/μs for a soft-start time of 600μs. Once VO

is within 10% of the boot voltage and PGD_IN is HIGH for six

PWM cycles (20µs for 300kHz switching frequency),

CLK_EN# is pulled LOW, and the SOFT cap is

charged/discharged by approximate 200µA and VO slews at

10mV/μs to the voltage set by the VID pins. In approximately

7ms, PGOOD is asserted HIGH. Figure 4 shows typical

startup timing.

PGD_IN Latch

It should be noted that PGD_IN going low will cause the

converter to latch off. Toggling PGD_IN won’t clear the latch.

Toggling VR_ON will clear it. This feature allows the

converter to respond to other system voltage outages

immediately.

VDD

VR_ON

100us

SOFT &VO

PGD_IN

10mV/us

2mV/us Vboot

~20us

CLK_EN#

IMVP-VI PGOOD

~7ms

FIGURE 4. SOFT-START WAVEFORMS USING A 20nF SOFT

CAPACITOR

Static Operation

After the startup sequence, the output voltage will be

regulated to the value set by the VID inputs per Table 1,

which is presented in the lntel® IMVP-6® specification. The

ISL6261 regulates the output voltage with ±0.5% accuracy

over the range of 0.7V to 1.5V.

A true differential amplifier remotely senses the core voltage

to precisely control the voltage at the microprocessor die.

VSEN and RTN pins are the inputs to the differential

amplifier.

As the load current increases from zero, the output voltage

droops from the VID value proportionally to achieve the

IMVP-6® load line. The ISL6261 can sense the inductor

current through the intrinsic series resistance of the

inductors, as shown in Figure 2, or through a precise resistor

in series with the inductor, as shown in Figure 3. The

inductor current information is fed to the VSUM pin, which is

the non-inverting input to the droop amplifier. The DROOP

pin is the output of the droop amplifier, and DROOP-VO

voltage is a high-bandwidth analog representation of the

inductor current. This voltage is used as an input to a

differential amplifier to achieve the IMVP-6® load line, and

also as the input to the overcurrent protection circuit.

When using inductor DCR current sensing, an NTC

thermistor is used to compensate the positive temperature

coefficient of the copper winding resistance to maintain the

load-line accuracy.

The switching frequency of the ISL6261 controller is set by

the resistor RFSET between pins VW and COMP, as shown in

Figures 2 and 3.

11 FN9251.1

September 27, 2006

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet ISL6261.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ISL6260 | Multi-Phase Core Regulator | Intersil Corporation |

| ISL6260B | Multi-Phase Core Regulator | Intersil Corporation |

| ISL6260C | Multiphase PWM Regulator | Intersil Corporation |

| ISL6261 | Single Phase Core Regulator | Intersil |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |