|

|

PDF HD64F2214 Data sheet ( Hoja de datos )

| Número de pieza | HD64F2214 | |

| Descripción | 16-Bit Single-Chip Microcomputer H8S Family/H8S/2200 Series | |

| Fabricantes | Renesas Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de HD64F2214 (archivo pdf) en la parte inferior de esta página. Total 70 Páginas | ||

|

No Preview Available !

REJ09B0189-0400

The revision list can be viewed directly by clicking the title page.

The revision list summarizes the locations of revisions and additions.

wwwD.DeattaaSilhseest4hUo.cuomld always be checked by referring to the relevant text.

16

H8S/2214 Group

Hardware Manual

Renesas 16-Bit Single-Chip Microcomputer

H8S Family/H8S/2200 Series

H8S/2214 HD64F2214

HD6432214

Rev. 4.00

Revision Date: Sep. 18, 2008

1 page

Preface

This LSI is a single-chip microcomputer made up of the H8S/2000 CPU with an internal 32-bit

architecture as its core, and the peripheral functions required to configure a system.

www.DataSheet4U.com

This LSI is equipped with ROM, RAM, a bus controller, data transfer controller (DTC), a DMA

controller (DMAC), two types of timers, a serial communication interface (SCI), a D/A converter,

an A/D converter, and I/O ports as on-chip supporting modules. This LSI is suitable for use as an

embedded processor for high-level control systems. Its on-chip ROM are flash memory (F-

ZTAT™*) and masked ROM that provides flexibility as it can be reprogrammed in no time to

cope with all situations from the early stages of mass production to full-scale mass production.

This is particularly applicable to application devices with specifications that will most probably

change.

Note: * F-ZTAT is a trademark of Renesas Technology, Corp.

Target Users: This manual was written for users who will be using the H8S/2214 Group in the

design of application systems. Members of this audience are expected to understand

the fundamentals of electrical circuits, logical circuits, and microcomputers.

Objective:

This manual was written to explain the hardware functions and electrical

characteristics of the H8S/2214 Group to the above audience. Refer to the

H8S/2600 Series, H8S/2000 Series Software Manual for a detailed description of

the instruction set.

Notes on reading this manual:

• In order to understand the overall functions of the chip

Read the manual according to the contents. This manual can be roughly categorized into parts

on the CPU, system control functions, peripheral functions and electrical characteristics.

• In order to understand the details of the CPU’s functions

Read the H8S/2600 Series, H8S/2000 Series Software Manual.

• In order to understand the details of a register when its name is known

The addresses, bits, and initial values of the registers are summarized in appendix B, Internal

I/O Registers.

Example: Bit order:

The MSB is on the left and the LSB is on the right.

Related Manuals: The latest versions of all related manuals are available from our web site.

Please ensure you have the latest versions of all documents you require.

http://www.renesas.com/

Rev.4.00 Sep. 18, 2008 Page v of lx

REJ09B0189-0400

5 Page

Item

Page

7.5.9 DMAC Bus

Cycles (Dual

Address Mode)

234

(2) FuwllwAwd.dDraetsasSheet4U.com

Mode (Cycle Steal

Mode)

8.2.5 DTC Transfer 258

Count Register A

(CRA)

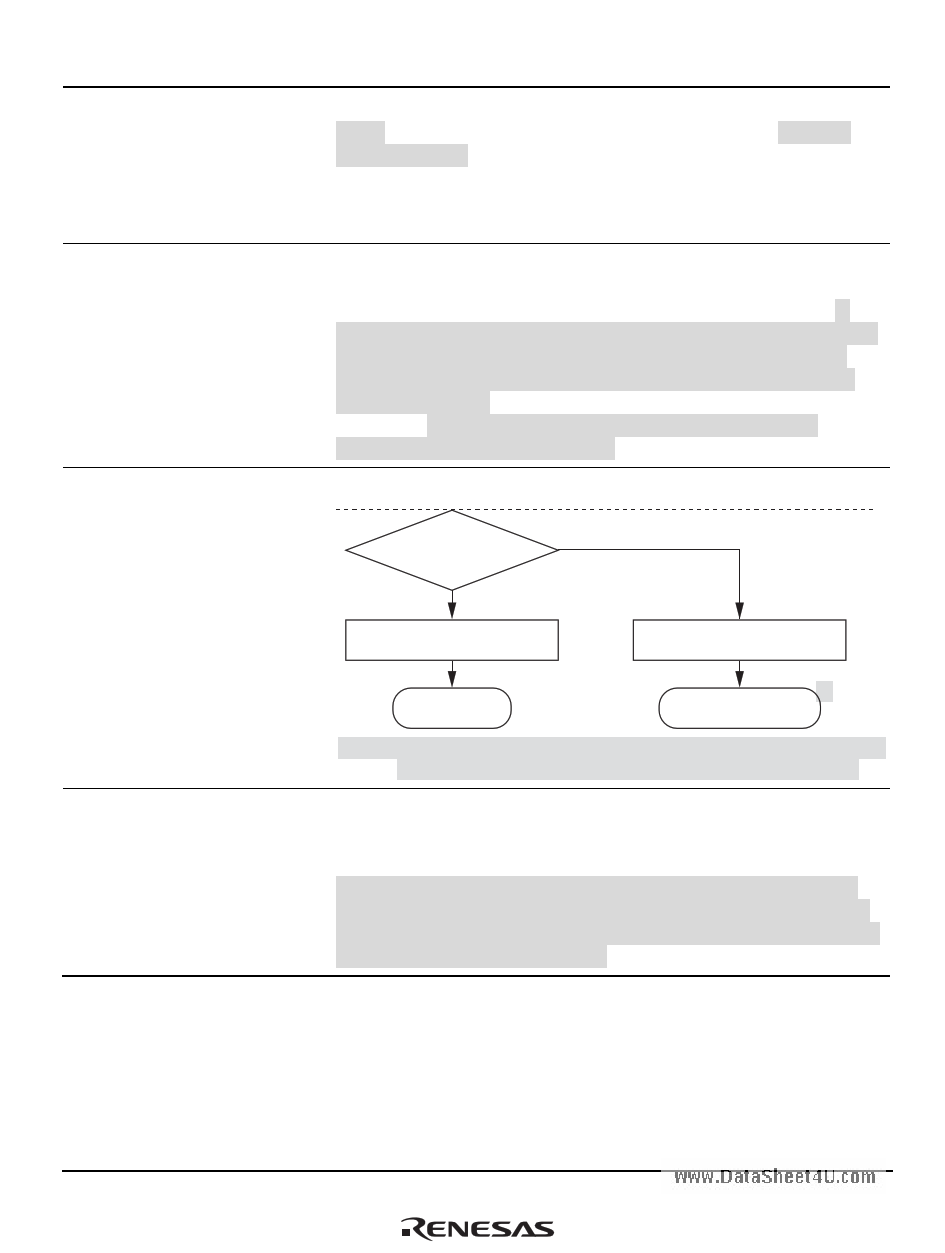

8.3.1 Overview

Figure 8.2

Flowchart of DTC

Operation

262

Revisions (See Manual for Details)

Description amended

Either a one-byte or a one-word transfer is performed for each

transfer request, and after the transfer the bus is released.

Description amended

In repeat mode or block transfer mode, CRA is divided into two

parts: the upper 8 bits (CRAH) and the lower 8 bits (CRAL). In

repeat mode, CRAH holds the transfer count and CRAL functions

as an 8-bit transfer counter (1 to 256). In block transfer mode,

CRAH holds the block size and functions as an 8-bit block size

counter (1 to 256). CRAL is decremented by 1 every time data is

transferred and when the counter value becomes H'00 the

contents of CRAH are transferred. This operation is repeated.

Note added

Transfer Counter = 0

or DISEL = 1

No

Yes

Clear an activation flag

Clear DTCER

8.3.2 Activation

Sources

264

End

Interrupt exception *

handling

Note: * See the section on the corresponding peripheral module for details

on the content of the processing required for interrupt handling.

Description added

... The activation source flag, in the case of RXI0, for example, is

the RDRF flag of SCI0.

Since there are multiple factors that can initiate DTC operation,

the flag that initiated the transfer is not cleared after the last byte

(or word) is transferred. The corresponding interrupt handler must

perform the required processing.

Rev.4.00 Sep. 18, 2008 Page xi of lx

REJ09B0189-0400

11 Page | ||

| Páginas | Total 70 Páginas | |

| PDF Descargar | [ Datasheet HD64F2214.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HD64F2211 | (HD643221x) 16-Bit Single-Chip Microcomputer H8S Family H8S-2200 Series | Renesas Technology |

| HD64F2212 | (HD643221x) 16-Bit Single-Chip Microcomputer H8S Family H8S-2200 Series | Renesas Technology |

| HD64F2214 | 16-Bit Single-Chip Microcomputer H8S Family/H8S/2200 Series | Renesas Technology |

| HD64F2215 | 16-Bit Single-Chip Microcomputer H8S Family/H8S/2200 Series | Renesas Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |