|

|

PDF HI-8599 Data sheet ( Hoja de datos )

| Número de pieza | HI-8599 | |

| Descripción | ARINC 429 LINE DRIVER AND DUAL RECEIVER | |

| Fabricantes | Holt Integrated Circuits | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de HI-8599 (archivo pdf) en la parte inferior de esta página. Total 12 Páginas | ||

|

No Preview Available !

June 2006

HI-8599

ARINC 429 LINE DRIVER AND DUAL RECEIVER

GENERAL DESCRIPTION

The HI-8599 from Holt Integrated Circuits is a silicon gate

CMOS device for interfacing a 16-bit parallel data bus

directly to the ARINC 429 serial bus. This device provides

two receivers, an independent transmitter and line driver

capability in a single package. The receiver input circuitry

and logic are designed to meet the ARINC 429

specifications for loading, level detection, timing, and

protocol. The transmitter section provides the ARINC 429

communication protocol and the line driver circuits

provide the ARINC 429 output levels.

The 16-bit parallel data bus exchanges the 32-bit ARINC

data word in two steps when either loading the transmitter

or interrogating the receivers. The data bus interfaces

with CMOS and TTL.

The HI-8599 provides the option to bypass most of the

internal output resistance so that external series

resistance may be added for lighting protection and still

matchwww.DataSheet4U.com the 75 ohm characteristic impedance of the ARINC

bus.

Each independent receiver monitors the data stream with

a sampling rate 10 times the data rate. The sampling rate

is software selectable at either 1MHz or 125KHz. The

results of a parity check are available as the 32nd ARINC

bit. The HI-8599 examines the null and data timings and

will reject erroneous patterns. For example, with a 125

KHz clock selection, the data frequency must be between

10.4 KHz and 15.6 KHz.

The transmitter has a First In, First Out (FIFO) memory to

store 8 ARINC words for transmission. The data rate of

the transmitter is software selectable by dividing the

master clock, CLK, by either 10 or 80. The master clock is

used to set the timing of the ARINC transmission within the

required resolution.

APPLICATIONS

! Avionics data communication

! Serial to parallel conversion

! Parallel to serial conversion

FEATURES

! ARINC specification 429 compliant

! Direct receiver and transmitter interface to

ARINC bus in a single device

! 16-Bit parallel data bus

! Timing control 10 times the data rate

! Selectable data clocks

! Receiver error rejection per ARINC

specification 429

! Automatic transmitter data timing

! Self test mode

! Parity functions

! Low power

! Industrial & full military temperature ranges

PIN CONFIGURATION (Top View)

429DI2(B) - 1

D/R1 - 2

D/R2 - 3

SEL - 4

EN1 - 5

EN2 - 6

BD15 - 7

BD14 - 8

BD13 - 9

BD12 - 10

BD11 - 11

HI-8599PQI

&

HI-8599PQT

33 - ENTX

32 - N/C

31 - V+

30 - TXB(OUT)

29 - TXA(OUT)

28 - V-

27 - GND

26 - TX/R

25 - PL2

24 - PL1

23 - BD00

44-Pin Plastic Quad Flat Pack (PQFP)

(See page 12 for additional pin configurations)

(DS8599 Rev. NEW)

HOLT INTEGRATED CIRCUITS

www.holtic.com

06/06

1 page

HI-8599

FUNCTIONAL DESCRIPTION (cont.) TRANSMITTER PARITY

TRANSMITTER

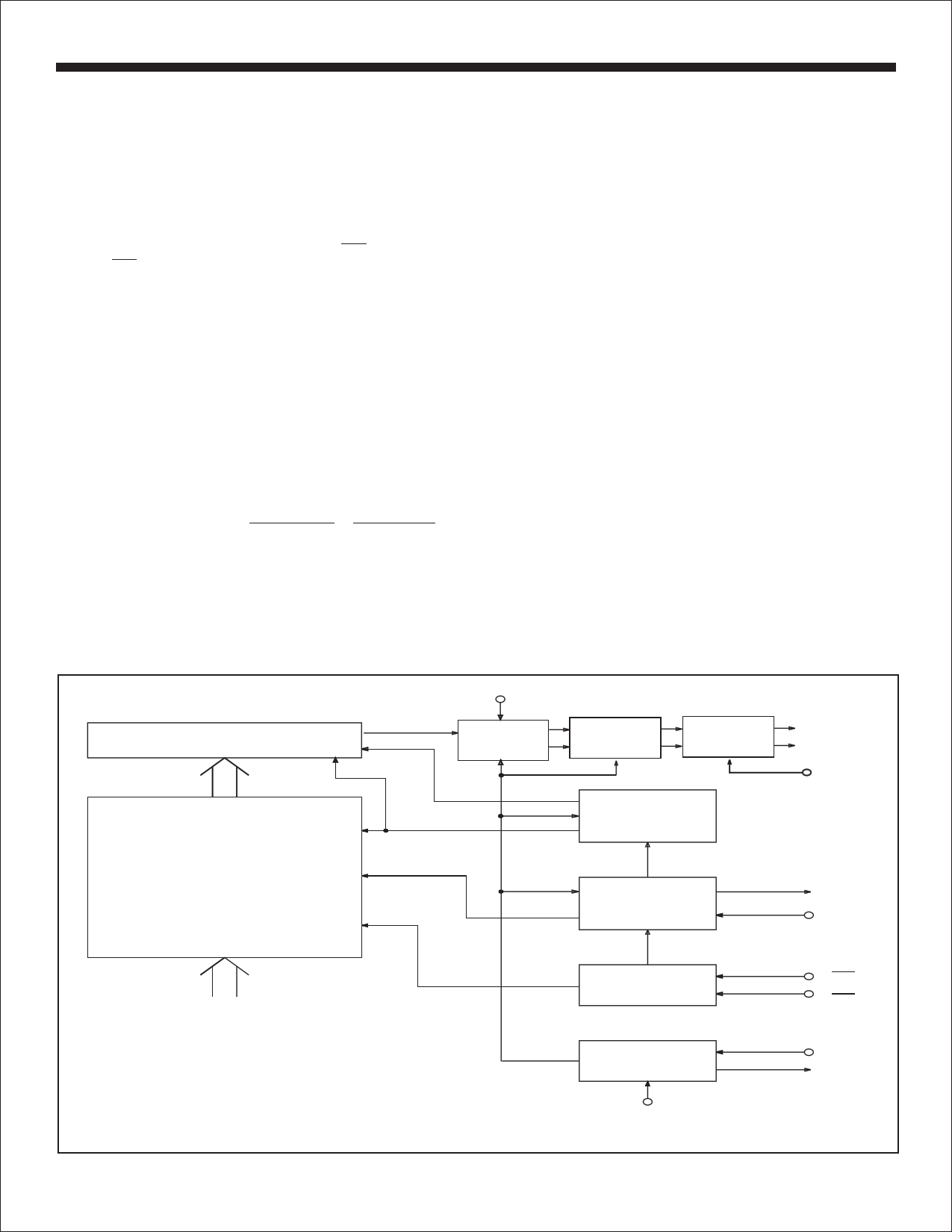

A block diagram of the transmitter section is shown in Figure 3.

FIFO OPERATION

The FIFO is loaded sequentially by first pulsing PL1 to load byte 1

and then PL2 to load byte 2. The control logic automatically loads

the 31 bit word in the next available position of the FIFO. If TX/R,

the transmitter ready flag is high (FIFO empty), then 8 words,

each 31 bits long, may be loaded. If TX/R is low, then only the

available positions may be loaded. If all 8 positions are full, the

FIFO ignores further attempts to load data.

DATA TRANSMISSION

When ENTX goes high, enabling transmission, the FIFO

positions are incremented with the top register loading into the

data transmission shift register. Within 2.5 data clocks the first

data bit appears at either TXA(OUT) or TXB(OUT). The 31 bits in

the data transmission shift register are presented sequentially to

the outputs in the ARINC 429 format with the following timing:

ARINC DATA BIT TIME

DATA BIT TIME

NULL BIT TIME

WORD GAP TIME

HIGH SPEED

10 Clocks

5 Clocks

5 Clocks

40 Clocks

LOW SPEED

80 Clocks

40 Clocks

40 Clocks

320 Clocks

The word counter detects when all loaded positions are

transmitted and sets the transmitter ready flag, TX/R, high.

The parity generator counts the ONES in the 31-bit word. If the

BD12 control word bit is set low, the 32nd bit transmitted will

make parity odd. If the control bit is high, the parity is even.

SELF TEST

If the BD05 control word bit is set low, the digital outputs of the

transmitter are internally connected to the logic inputs of the

receivers, bypassing the analog bus interface circuitry. Data to

Receiver 1 is as transmitted and data to Receiver 2 is the

complement. All data transmitted during self test is also present

on the TXA(OUT) and TXB(OUT) line driver outputs. Taking

TEST high forces TXA(OUT) and TXB(OUT) into the null state

regardless of the state of Bd05 control word bit.

SYSTEM OPERATION

The two receivers are independent of the transmitter. Therefore,

control of data exchanges is strictly at the option of the user. The

only restrictions are:

1. The received data may be overwritten if not retrieved

within one ARINC word cycle.

2. The FIFO can store 8 words maximum and ignores

attempts to load addition data if full.

3. Byte 1 of the transmitter data must be loaded first.

4. Either byte of the received data may be retrieved first.

Both bytes must be retrieved to clear the data ready flag.

5. After ENTX, transmission enable, goes high it cannot go

low until TX/R, transmitter ready flag, goes high. Otherwise,

one ARINC word is lost during transmission.

BIT BD12

31 BIT PARALLEL

LOAD SHIFT REGISTER

8 X 31 FIFO

DATA BUS

BIT CLOCK

PARITY

GENERATOR

WORD CLOCK

ADDRESS

LOAD

DATA AND

NULL TIMER

SEQUENCER

LINE DRIVER

BIT

AND

WORD GAP

COUNTER

START

SEQUENCE

WORD COUNTER

AND

FIFO CONTROL

INCREMENT

WORD COUNT

FIFO

LOADING

SEQUENCER

TXA(OUT)

TXB(OUT)

TEST

TX/R

ENTX

PL1

PL2

FIGURE 3. TRANSMITTER BLOCK DIAGRAM

DATA

CLOCK

DATA CLOCK

DIVIDER

CONTROL BIT

BD13

CLK

TX CLK

HOLT INTEGRATED CIRCUITS

5

5 Page

HI-8599

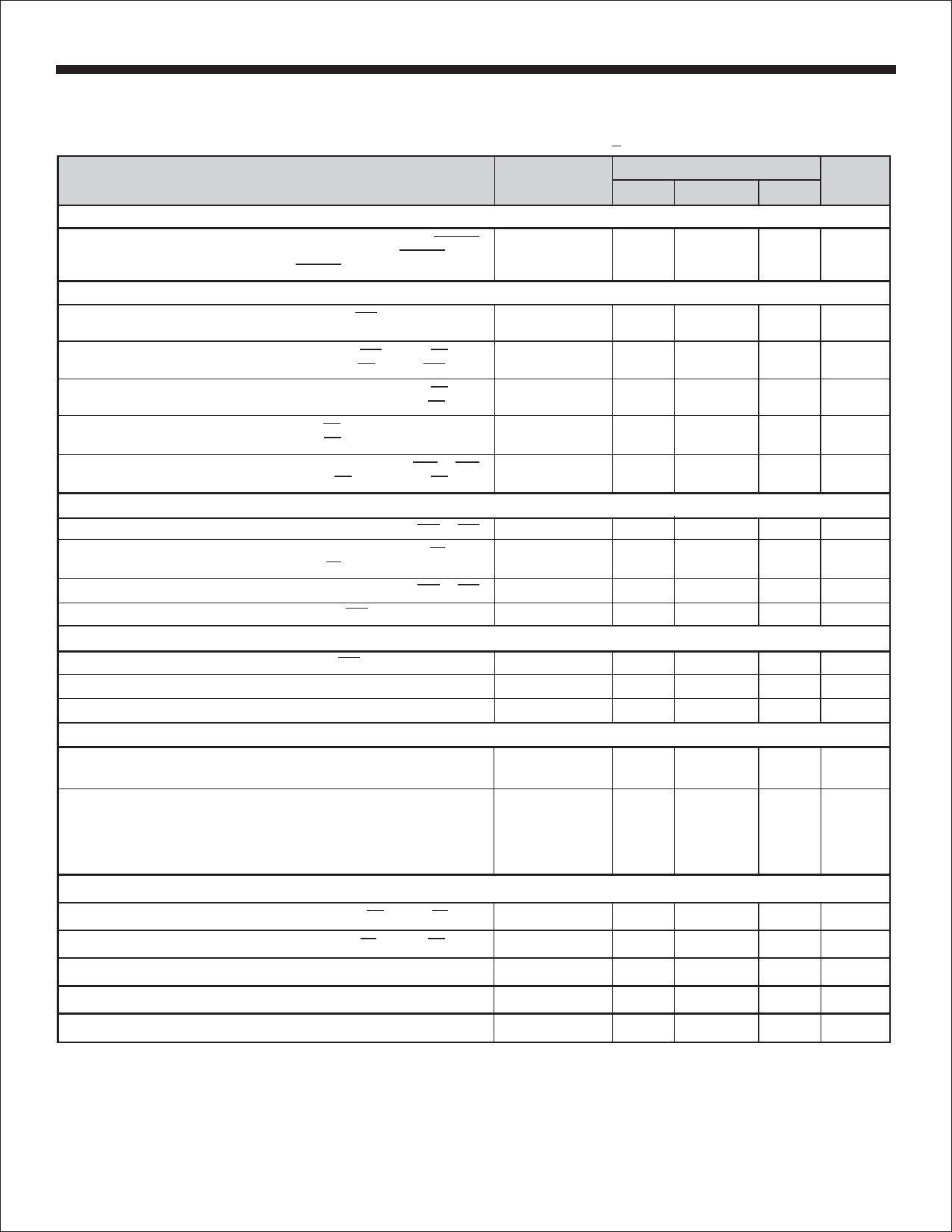

AC ELECTRICAL CHARACTERISTICS

Vcc = 5V, V+=10V, V- = -10V, GND = 0V, TA = Oper. Temp. Range and fclk = 1MHz +0.1% with 60/40 duty cycle

PARAMETER

CONTROL WORD TIMING

Pulse Width - CWSTR

Setup - DATA BUS Valid to CWSTR HIGH

Hold - CWSTR HIGH to DATA BUS Hi-Z

RECEIVER TIMING

Delay - Start ARINC 32nd Bit to D/R LOW: High Speed

Low Speed

Delay - D/R LOW to EN LOW

Delay - EN LOW to D/R HIGH

Setup - SEL to EN LOW

Hold - SEL to EN HIGH

Delay - EN LOW to DATA BUS Valid

Delay - EN HIGH to DATA BUS Hi-Z

Pulse Width - EN1 or EN2

Spacing - EN HIGH to next EN LOW

FIFO TIMING

Pulse Width - PL1 or PL2

Setup - DATA BUS Valid to PL HIGH

Hold - PL HIGH to DATA BUS Hi-Z

Spacing - PL1 or PL2

Delay - PL2 HIGH to TX/R LOW

TRANSMISSION TIMING

Spacing - PL2 HIGH to ENTX HIGH

Delay - 32nd ARINC Bit to TX/R HIGH

Spacing - TX/R HIGH to ENTX LOW

LINE DRIVER OUTPUT TIMING

SYMBOL

tCWSTR

tCWSET

tCWHLD

tD/R

tD/R

tD/REN

tEND/R

tSELEN

tENSEL

tENDATA

tDATAEN

tEN

tENEN

tPL

tDWSET

tDWHLD

tPL12

tTX/R

tPL2EN

tDTX/R

tENTX/R

LIMITS

MIN TYP MAX

80

50

10

0

10

10

50

80

50

16

128

200

100

30

80

50

10

0

840

0

50

0

Delay - ENTX HIGH to TXA(OUT) or TXB(OUT): High Speed

Delay - ENTX HIGH to TXA(OUT) or TXB(OUT): Low Speed

Line driver transition differential times:

(High Speed)

(Low Speed)

high to low

low to high

high to low

low to high

tENDAT

tENDAT

tfx

trx

tfx

trx

25

200

1.0 1.5 2.0

1.0 1.5 2.0

5.0 10 15

5.0 10 15

REPEATER OPERATION TIMING

Delay - EN LOW to PL LOW

tENPL

0

Hold - PL HIGH to EN HIGH

tPLEN

0

Delay - TX/R LOW to ENTX HIGH

tTX/REN

0

MASTER RESET PULSE WIDTH

tMR 400

ARINC DATA RATE AND BIT TIMING

± 1%

UNITS

ns

ns

ns

µs

µs

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

µs

ns

ns

µs

µs

µs

µs

µs

µs

ns

ns

ns

ns

HOLT INTEGRATED CIRCUITS

11

11 Page | ||

| Páginas | Total 12 Páginas | |

| PDF Descargar | [ Datasheet HI-8599.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HI-8590 | ARINC 429 LINE DRIVER AND DUAL RECEIVER | Holt Integrated Circuits |

| HI-8591 | ARINC 429 LINE RECEIVER | Holt Integrated Circuits |

| HI-8592 | (HI-8592 - HI-8594) Single-Rail ARINC 429 Differential Line Driver | Holt Integrated Circuit |

| HI-8593 | (HI-8592 - HI-8594) Single-Rail ARINC 429 Differential Line Driver | Holt Integrated Circuit |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |