|

|

PDF ISL6442 Data sheet ( Hoja de datos )

| Número de pieza | ISL6442 | |

| Descripción | PWM and Linear Controller | |

| Fabricantes | Intersil Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ISL6442 (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

®

Data Sheet

April 7, 2006

ISL6442

FN9204.1

Dual (180° Out-of-Phase) PWM and Linear

Controller

The ISL6442 is a high-performance, triple output controller

that provides a single high-frequency power solution

primarily for Broadband, DSL and Networking applications.

This device integrates complete control, monitoring and

protection functions for two synchronous buck PWM

controllers and one linear controller. Input voltage ripple and

total RMS input current is substantially reduced by

synchronized 180° out-of-phase operation of the two PWMs.

The two PWM buck converters provide simple voltage mode

control. The output voltage of the converters can be

precisely regulated to as low as 0.6V, with a maximum

tolerance of ±1.5% over temperature and line variations.

Programmable switching frequency up to 2.5MHz provides

fast transient response and small external components. The

linear controller provides a low-current output.

The ISL6442 has voltage-tracking capability. Each controller

has soft-start and independent enable functions combined

on a single pin. A capacitor from SS/EN to ground sets the

soft-start time; pulling SS/EN pin below 1V disables the

controller. Both outputs can soft-start into a pre-biased load.

The ISL6442 incorporates robust protection features. An

adjustable overcurrent protection circuit monitors the output

current by sensing the voltage drop across the upper

MOSFET rDS(ON). Hiccup mode overcurrent operation

protects the DC/DC converters from damage under over-

load and short circuit conditions. A PGOOD signal is issued

when soft-start is complete and PWM outputs are within 10%

of their regulated values and the linear regulator output is

higher than 75% of its nominal value. Thermal shut-down

circuitry turns the device off if the IC temperature exceeds

150°C.

Ordering Information

PART

PART

TEMP.

PKG.

NUMBER* MARKING RANGE (°C) PACKAGE DWG. #

ISL6442IA ISL6442IA -40 to 85 24 Ld QSOP M24.15

ISL6442IAZ ISL6442IAZ -40 to 85 24 Ld QSOP M24.15

(Note)

(Pb-free)

* Add “-TK” to suffix for tape and reel.

NOTE: Intersil Pb-free plus anneal products employ special Pb-free

material sets; molding compounds/die attach materials and 100% matte

tin plate termination finish, which are RoHS compliant and compatible

with both SnPb and Pb-free soldering operations. Intersil Pb-free

products are MSL classified at Pb-free peak reflow temperatures that

meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

Features

• 4.5V to 5.5V or 5.5V to 24V Input Voltage Range

• ±1.5% PWM Switcher Reference Accuracy Over Line and

Temperature

• Three Programmable Power Output Voltages

- Two PWM Controllers with Out-of-Phase Operation

- Voltage-Mode PWM Control

- One Linear Controller

• Programmable Switching Frequency from 300kHz to 2.5MHz

• Fast Transient Response

- High-Bandwidth Error Amplifier

• Extensive Circuit Protection Functions

- Overvoltage, Undervoltage, and Overtemperature

- Programmable Overcurrent Limit with Hiccup Mode

Operation

- Lossless Current Sensing (no Sense Resistor needed)

• Externally Adjustable Soft-Start Time

- Independent Enable Control

- Voltage Tracking Capability

- Able to Soft-Start into a Pre-Biased Load

• PGOOD Output with Delay

• 24 Ld QSOP

• Pb-Free Plus Anneal Available (RoHS Compliant)

Applications

• Complete 1 Chip Solution for DSL Modems/Routers

• DSP, ASIC, and FPGA Point of Load Regulation

• ADSL, Broadband and Networking Applications

Pinout

ISL6442 (QSOP)

TOP VIEW

OCSET1 1

SS1/EN1 2

COMP1 3

FB1 4

RT 5

SGND 6

LCDR 7

LCFB 8

FB2 9

COMP2 10

SS2/EN2 11

OCSET2 12

24 VIN

23 BOOT1

22 UGATE1

21 PHASE1

20 LGATE1

19 VCC

18 PGND

17 LGATE2

16 PHASE2

15 UGATE2

14 BOOT2

13 PGOOD

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774 | Intersil (and design) is a registered trademark of Intersil Americas Inc.

Copyright Intersil Americas Inc. 2006. All Rights Reserved

All other trademarks mentioned are the property of their respective owners.

1 page

ISL6442

Electrical Specifications

Operating Conditions Unless Otherwise

values are at 25°C. (Continued)

Noted:

VIN

=

12V,

or

VCC

=

5V

±10%,

TA

=

-40°C

to

+85°C.

Typical

PARAMETER

SYMBOL

TEST CONDITIONS

MIN TYP

MAX

UNITS

ENx/SSx Soft-Start Top of Ramp

Voltage

VSSx_top

(Note 3)

- 3.2

-

V

POWER-ON RESET ON VCC

Rising Threshold

Falling Threshold

PWM CONVERTERS

VPOR_r

VPOR_f

4.2 4.4

3.85 4.0

4.475

4.1

V

V

Minimum UGATE on Time

Maximum Duty Cycle

Maximum Duty Cycle

FBx Pin Bias Current

OSCILLATOR

tUGATE_min (Note 3)

DCmax

VIN = 4.5 or 12V; FSW = 300kHz

DCmax

VIN = 4.5V; FSW = 2.5MHz

IFBx (Note 3)

- 100

95 -

80 -

- 80

-

-

-

-

ns

%

%

nA

Low End Frequency

FSW

VIN = 5V or 12V; RT = 52.3k

VIN = 24V; RT = 52.3k

270 300

270 305

330

340

kHz

kHz

High End Frequency

FSW

VIN = 5V; RT = 5.23k

VIN = 12V; RT = 5.23k

2.25 2.5

2.25 2.55

2.75

2.85

MHz

MHz

Frequency Adjustment Range

FSW

RT = 52.3k; (Note 3)

RT = 5.23k; (Note 3)

- 0.3 - MHz

- 2.5 - MHz

PWM Sawtooth Ramp Amplitude VPP

(peak-peak)

(Note 4)

- 1.25

-

V

PWM CONTROLLER GATE DRIVERS

Gate Drive Peak Current

(Note 3)

- 0.7

-

A

Rise Time

Fall Time

Dead Time Between Drivers

(Note 3); CL = 1000pF

(Note 3); CL = 1000pF

(Note 3)

- 20

- 20

- 30

-

-

-

ns

ns

ns

ERROR AMPLIFIERS

DC Gain

Gain

(Note 4)

- 88

-

dB

Gain-Bandwidth Product

GBWP

(Note 4)

- 15 - MHz

Slew Rate

SR (Note 4); COMP = 10pF

-5

- V/µs

Maximum Output Voltage

VEA_max

PROTECTION and OUTPUT MONITOR

VCC = 5V; RL = 10k to ground

3.9 4.4

-

Overvoltage Threshold

OV

113 116

121

%

Undervoltage Threshold

UV

78 82

88

%

OCSET Current Source

LINEAR CONTROLLER

IOCSET

VOCSET = 4.5V

80 110

140

µA

Drive Sink Current

LCFB Feedback Threshold

LCFB Input Leakage Current

ILCDR

VLCFB

ILCFB

LCDR

TA = 25°C

TA = -40°C to +85°C

(Note 3)

50

-

0.570

-

-

0.595

-

80

-

-

0.620

-

mA

V

V

nA

5 FN9204.1

April 7, 2006

5 Page

ISL6442

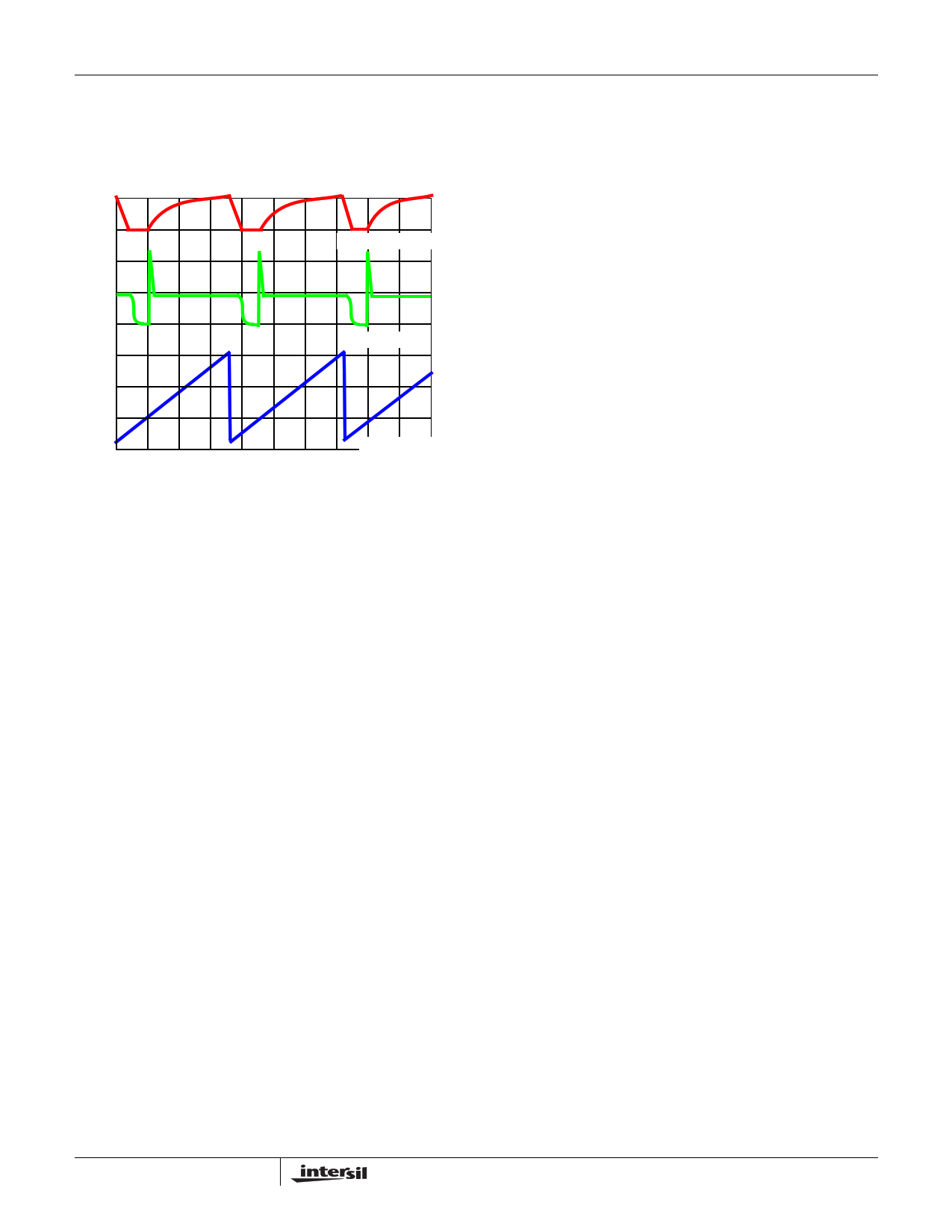

value. When the SS2/EN2 ramp reaches ~3V, the cycle

repeats, and can continue indefinitely. If the short-circuit is

removed, the output will ramp up with the next soft-start, and

normal operation will resume. VOUT1 and SS1/EN1 will

independently function the same way.

GND>

VOUT2 (2V/DIV)

0A>

IOUT2 (2A/DIV)

GND>

SS2/EN2 (1V/DIV)

FIGURE 12. OVERCURRENT PROTECTION

UVP - (Function independent for both PWM). If the voltage

on the FB pin falls to 82% (typical) of the reference voltage

for 8 consecutive PWM cycles, then the circuit enters into

soft-start hiccup mode. This mode is identical to the

overcurrent hiccup mode. The UVP comparator is separate

from the one sensing for PGOOD, which should have

already detected a problem, before the UVP trips.

OVP - (Function independent for both PWM). If voltage on

FB pin rises to 116% (typical) of the reference voltage, the

lower gate driver is turned on continuously (with diode

emulation enabled). If SS_DN (internal soft-start done

signal) is true (not in soft-start) and the overvoltage condition

continues for 32 consecutive PWM cycles, then that output

is latched off with the gate drivers three-stated. The

capacitor on the SS/EN pin will not be discharged. The

switcher will restart when the SS/EN pin is externally driven

below 1V, or if power is recycled to the chip, or when the

voltage on the FB pin falls to the 82% (typical) undervoltage

threshold - after 8 clock cycles the chip will enter soft-start

hiccup mode. The hiccup mode is identical to the

overcurrent hiccup mode. The OVP comparator is separate

from the one sensing for PGOOD, which should have

already detected a problem, before the OVP trips.

Application Guidelines

PWM Controller

Discussion

The PWM must be compensated such that it achieves the

desired transient performance goals, stability, and DC

regulation requirements.

The first parameter that needs to be chosen is the switching

frequency, FSW. This decision is based on the overall size

11

constraints and the frequency plan of the end equipment.

Smaller space requires higher frequency. This allows the

output inductor, input capacitor bank, and output capacitor

bank to be reduced in size and/or value. The power supply

must be designed such that the frequency and its distribution

over component tolerance, time and temperature causes

minimal interference in RF stages, IF stages, PLL loops,

mixers, etc.

Inductor Selection

The output inductor is selected to meet the output voltage

ripple requirements and minimize the converter’s response

time to the load transient. The inductor value determines the

converter’s ripple current, and the ripple voltage is a function

of the ripple current. The ripple current and voltage are

approximated by the following equations, where ESR is the

output capacitance ESR value.

∆I = -V----I-F-N---S-----W---V---•-O---L-U-----T- • V----V-O---I-U-N---T--

∆VOUT = ∆I x ESR

Increasing the value of inductance reduces the ripple current

and voltage. However, the large inductance value reduces

the converter’s response time to a load transient (and

usually increases the DCR of the inductor, which decreases

the efficiency). Increasing the switching frequency (FSW) for

a given inductor also reduces the ripple current and voltage.

One of the parameters limiting the converter’s response to a

load transient is the time required to change the inductor

current. Given a sufficiently fast control loop design, the

ISL6442 will provide either 0% or 100% duty cycle in

response to a load transient. The response time is the time

required to slew the inductor current from an initial current

value to the transient current level. During this interval the

difference between the inductor current and the transient

current level must be supplied by the output capacitor.

Minimizing the response time can minimize the output

capacitance required.

The response time to a transient is different for the

application of load and the removal of load. The following

equations give the approximate response time interval for

application and removal of a transient load:

tRISE = L----VO----I-U-N---T--–---×--V--I--TO----R-U---A-T---N--

tFALL = L----O-----U---V-T---O--×---U-I--T-T---R----A----N--

where: ITRAN is the transient load current step, tRISE is the

response time to the application of load, and tFALL is the

response time to the removal of load. With a +5V input

source, the worst case response time can be either at the

application or removal of load and dependent upon the

output voltage setting. Be sure to check both of these

equations at the minimum and maximum output levels for

the worst case response time.

Finally, check that the inductor Isat rating is sufficiently above

the maximum output current (DC load plus ripple current).

FN9204.1

April 7, 2006

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet ISL6442.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ISL644 | High Voltage ORing MOSFET Controller | Intersil |

| ISL6440 | Step-Down PWM Controller | Intersil Corporation |

| ISL6440A | Advanced PWM and Triple Linear Power Controller | Intersil Corporation |

| ISL6441 | Step-Down PWM and Single Linear Controller | Intersil Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |