|

|

PDF ISL83202 Data sheet ( Hoja de datos )

| Número de pieza | ISL83202 | |

| Descripción | 1A Peak Current H-Bridge FET Driver | |

| Fabricantes | Intersil Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ISL83202 (archivo pdf) en la parte inferior de esta página. Total 12 Páginas | ||

|

No Preview Available !

®

Data Sheet

December 20, 2006

ISL83202

FN6382.0

55V, 1A Peak Current H-Bridge FET Driver

The ISL83202 is a medium-frequency H-Bridge FET driver

capable of 1A (typ) of peak drive current that is designed to

drive high- and low-side N-Channel MOSFETs in medium-

voltage applications. Optimized for PWM motor control and

uninterruptible power supply systems, the ISL83202 enables

simple and flexible bridge-based design. With typical input-

to-output propagation delays as low as 25ns and with a user-

programmable dead-time range of 0.1µs to 4.5µs, the

ISL83202 is ideal for switching frequencies up to 200kHz.

The dead-time of the ISL83202 is programmable via a single

resistor. The ISL83202's four independent driver control

inputs (ALI, AHI, BLI, and BHI) allow driving of every

possible switch combination except those that would cause

a shoot-through condition. A global disable input, DIS,

overrides input control and causes the ISL83202 to refresh

the bootstrap capacitor when pulled low. Integrated

undervoltage protection and shoot-through protection ensure

reliable system operation.

The ISL83202 is available in compact 16 Ld SOIC and 16 Ld

PDIP packages and operates over the range of -55°C to

+125°C.

Ordering Information

PART

NUMBER

PART

TEMP.

PKG.

MARKING RANGE (°C) PACKAGE DWG. #

ISL83202IBZ 83202IBZ

(Note)

-55 to +125 16 Ld SOIC (N) M16.15

(Pb-free)

ISL83202IBZT 16 Ld SOIC (N) Tape and Reel

(Note)

(Pb-free)

M16.15

ISL83202IPZ ISL83202IPZ -55 to +125 16 Ld PDIP** E16.3

(Note)

(Pb-free)

NOTE: Intersil Pb-free plus anneal products employ special Pb-free

material sets; molding compounds/die attach materials and 100%

matte tin plate termination finish, which are RoHS compliant and

compatible with both SnPb and Pb-free soldering operations. Intersil

Pb-free products are MSL classified at Pb-free peak reflow

temperatures that meet or exceed the Pb-free requirements of IPC/

JEDEC J STD-020.

**Pb-free PDIPs can be used for through hole wave solder processing

only. They are not intended for use in Reflow solder processing

applications.

Features

• Independently Drives 4 N-Channel FETs in Half Bridge or

Full Bridge Configurations

• Bootstrap Supply Max Voltage: 70VDC

• Drives a 1000pF Load in Free Air at +50°C with Rise and

Fall Times of 15ns (typ)

• User-Programmable Dead Time from 0.1 to 4.5μs

• DIS (Disable) Overrides Input Control and Refreshes

Bootstrap Capacitor when Pulled Low

• Input Logic Thresholds Compatible with 5V to 15V Logic

Levels

• Shoot-Through Protection

• Undervoltage Protection

• Pb-Free Plus Anneal Available (RoHS Compliant)

Applications

• UPS Systems

• DC Motor Controls

• Full Bridge Power Supplies

• Switching Power Amplifiers

• Noise Cancellation Systems

• Battery Powered Vehicles

• Peripherals

• Medium/Large Voice Coil Motors

• Related Literature

- TB363, Guidelines for Handling and Processing

Moisture Sensitive Surface Mount Devices (SMDs)

Pinout

ISL83202

(PDIP, SOIC)

TOP VIEW

BHB 1

BHI 2

BLI 3

ALI 4

DEL 5

VSS 6

AHI 7

DIS 8

16 BHO

15 BHS

14 BLO

13 ALO

12 VDD

11 AHS

10 AHO

9 AHB

1 CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774 | Intersil (and design) is a registered trademark of Intersil Americas Inc.

Copyright Intersil Americas Inc. 2006. All Rights Reserved

All other trademarks mentioned are the property of their respective owners.

1 page

ISL83202

Electrical Specifications

PARAMETER

VDD = VAHB = VBHB = 12V, VSS = VAHS = VBHS = 0V, RDEL = 100k (Continued)

SYMBOL

TEST CONDITIONS

TJ = +25°C

MIN TYP MAX

TJ = -55°C

TO +150°C

MIN MAX

UNITS

GATE DRIVER OUTPUT PINS: ALO, BLO, AHO, and BHO

Low Level Output Voltage

High Level Output Voltage

Peak Pullup Current

Peak Pulldown Current

VOL

VDD-VOH

IO+

IO-

IOUT = 50mA

IOUT = -50mA

VOUT = 0V

VOUT = 12V

0.65 1.1 0.5 1.2

0.7 1.2 0.5 1.3

1.0 0.6 2.0

1.0 0.6 2.0

V

V

A

A

Switching Specifications VDD = VAHB = VBHB = 12V, VSS = VAHS = VBHS = 0V, RDEL= 100k, CL = 1000pF.

TJ = +25°C

TJ = -55°C TO

+150°C

PARAMETER

SYMBOL

TEST CONDITIONS MIN TYP MAX MIN MAX

Lower Turn-off Propagation Delay

(ALI-ALO, BLI-BLO)

TLPHL

- 25 50 - 70

Upper Turn-off Propagation Delay

(AHI-AHO, BHI-BHO)

THPHL

- 55 80 - 100

Lower Turn-on Propagation Delay

(ALI-ALO, BLI-BLO)

TLPLH

- 40 85 - 100

Upper Turn-on Propagation Delay

(AHI-AHO, BHI-BHO)

THPLH

- 75 110 - 150

Rise Time

Fall Time

Minimum Input Pulse Width

Output Pulse Response to 50ns Input Pulse

Disable Turn-off Propagation Delay

(DIS - Lower Outputs)

TR

TF

TPWIN-ON/OFF

TPWOUT

TDISLOW

- 9 20 - 25

- 9 20 - 25

50 -

- 50 -

63 80

- 50 80 - 90

Disable Turn-off Propagation Delay

(DIS - Upper Outputs)

TDISHIGH

- 75 100 - 125

Disable Turn-on Propagation Delay

(DIS - ALO and BLO)

TDLPLH

- 40 70 - 100

Disable Turn-on Propagation Delay

(DIS- AHO and BHO)

TDHPLH

RDEL = 10k

- 1.2 2 - 3

Refresh Pulse Width (ALO and BLO)

TREF-PW

375 580 900 350 950

UNITS

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

μs

ns

INPUT

ALI, BLI

AHI, BHI

VDDUV

XXX

XX1

0X0

1X0

010

000

NOTE: X signifies that input can be either a “1” or “0”.

TRUTH TABLE

VHBUV

X

X

1

X

0

0

DIS

1

X

0

0

0

0

OUTPUT

ALO, BLO

AHO, BHO

00

00

00

10

01

00

5 FN6382.0

December 20, 2006

5 Page

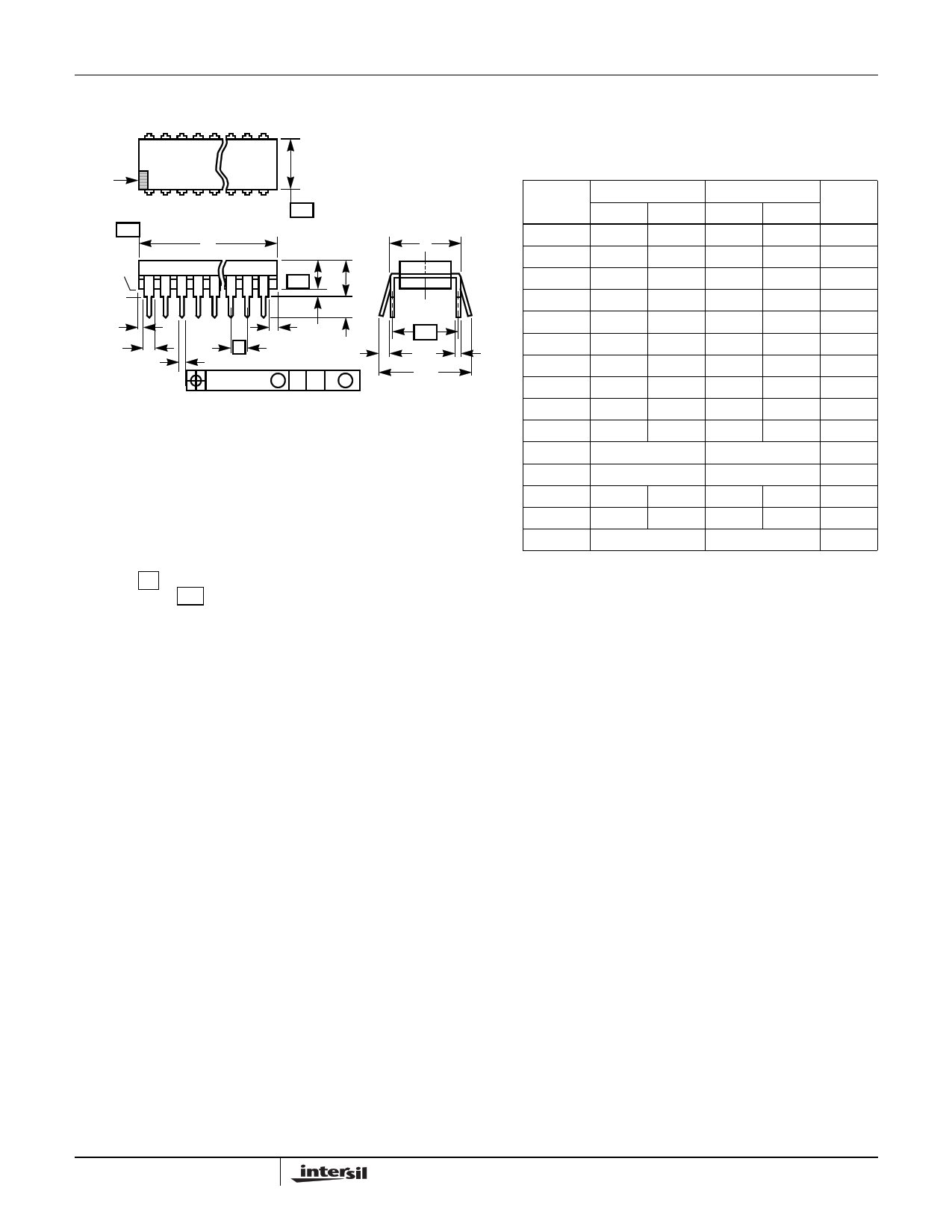

Dual-In-Line Plastic Packages (PDIP)

ISL83202

INDEX

AREA

N

12 3

E1

N/2

-A-

BASE

PLANE

SEATING

PLANE

D1

B1

B

-B-

D

-C- A2 A

L

D1

e

A1

eC

0.010 (0.25) M C A B S

E

CL

eA

C

eB

NOTES:

1. Controlling Dimensions: INCH. In case of conflict between English and

Metric dimensions, the inch dimensions control.

2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

3. Symbols are defined in the “MO Series Symbol List” in Section 2.2 of

Publication No. 95.

4. Dimensions A, A1 and L are measured with the package seated in JE-

DEC seating plane gauge GS-3.

5. D, D1, and E1 dimensions do not include mold flash or protrusions.

Mold flash or protrusions shall not exceed 0.010 inch (0.25mm).

6. E and eA are measured with the leads constrained to be perpendic-

ular to datum -C- .

7. eB and eC are measured at the lead tips with the leads unconstrained.

eC must be zero or greater.

8. B1 maximum dimensions do not include dambar protrusions. Dambar

protrusions shall not exceed 0.010 inch (0.25mm).

9. N is the maximum number of terminal positions.

10. Corner leads (1, N, N/2 and N/2 + 1) for E8.3, E16.3, E18.3, E28.3,

E42.6 will have a B1 dimension of 0.030 - 0.045 inch (0.76 - 1.14mm).

E16.3 (JEDEC MS-001-BB ISSUE D)

16 LEAD DUAL-IN-LINE PLASTIC PACKAGE

INCHES

MILLIMETERS

SYMBOL

A

A1

A2

B

B1

C

D

D1

E

E1

MIN

-

0.015

0.115

0.014

0.045

0.008

0.735

0.005

0.300

0.240

MAX

0.210

-

0.195

0.022

0.070

0.014

0.775

-

0.325

0.280

MIN

-

0.39

2.93

0.356

1.15

0.204

18.66

0.13

7.62

6.10

MAX

5.33

-

4.95

0.558

1.77

0.355

19.68

-

8.25

7.11

NOTES

4

4

-

-

8, 10

-

5

5

6

5

e 0.100 BSC 2.54 BSC -

eA 0.300 BSC

7.62 BSC

6

eB - 0.430 - 10.92 7

L

0.115 0.150 2.93

3.81

4

N 16

16 9

Rev. 0 12/93

11 FN6382.0

December 20, 2006

11 Page | ||

| Páginas | Total 12 Páginas | |

| PDF Descargar | [ Datasheet ISL83202.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ISL83202 | 1A Peak Current H-Bridge FET Driver | Intersil Corporation |

| ISL83204A | High Frequency Full Bridge FET Driver | Intersil Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |