|

|

PDF ISL8112 Data sheet ( Hoja de datos )

| Número de pieza | ISL8112 | |

| Descripción | Main Power Supply Controllers | |

| Fabricantes | Intersil Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ISL8112 (archivo pdf) en la parte inferior de esta página. Total 27 Páginas | ||

|

No Preview Available !

®

Data Sheet

August 10, 2010

ISL8112

FN6396.1

High Light-Load Efficiency, Dual-Output,

Main Power Supply Controllers

ISL8112 is a dual-output Synchronous Buck controller with 2A

integrated driver. It features high light load efficiency which is

especially preferred in systems concerned with high efficiency

in wide load range, like the battery powered system. ISL8112

includes two constant on-time PWM controllers. Either of the

two outputs can operate in output fixed mode or adjustable

mode. In fixed mode, one output can be 5V or 3.3V and the

other can output 1.5V or 1.05V. In output adjustable mode,

one output can be 0.7V to 5.5V, and the other output can

range from 0V to 2.5V (sensing output voltage directly) or up

to 5V (using resistor divider voltage for voltage sensing). This

device also features a linear regulator providing 3.3V/5V, or

adjustable from 0.7V to 4.5V via LDOREF. The linear

regulator provides up to 100mA output current with automatic

linear-regulator bootstrapping to the BYP input. When in

switch over, the LDO output can source up to 200mA.

ISL8112 includes on-board power-up sequencing, the power-

good (PGOOD_) outputs, digital soft-start, and internal soft-

stop output discharge that prevents negative voltages on

shutdown.

ISL8112 is implemented with constant on-time PWM control

scheme which need no sense resistors and provides 100ns

response to load transients while maintaining a relatively

constant switching frequency. The unique ultrasonic pulse-

skipping mode maintains the switching frequency above

25kHz, eliminating undesired audible noises in low frequency

operation at light load. Other features include pulse skipping

which maximizes efficiency in light-load applications, and

fixed-frequency PWM mode which reduces RF interference in

sensitive applications.

Ordering Information

PART

NUMBER

(Note)

PART

MARKING

TEMP.

RANGE

(°C)

PACKAGE

PKG.

DWG. #

ISL8112IRZ* ISL8112 IRZ -40 to +100 32 Ld QFN

(Pb-free)

L32.5x5B

*Add “-T” suffix for tape and reel. Please refer to TB347 for details on

reel specifications.

NOTE: These Intersil Pb-free plastic packaged products employ

special Pb-free material sets, molding compounds/die attach materials,

and 100% matte tin plate plus anneal (e3 termination finish, which is

RoHS compliant and compatible with both SnPb and Pb-free soldering

operations). Intersil Pb-free products are MSL classified at Pb-free

peak reflow temperatures that meet or exceed the Pb-free

requirements of IPC/JEDEC J STD-020.

Features

• Wide Input Voltage Range 5.5V to 25V

• Constant ON-TIME Control with 100ns Load-Step

Response

• Dual Fixed Outputs of 1.05V (3.3V) and 1.5V (5.0V), or

Adjustable Outputs of 0.7V to 5.5V (SMPS1) and 0V to

2.5V/5V (SMPS2), ±1.5% Accuracy

• Adjustable Switching Frequency: 400/500kHz,

300/400kHz, 200/300kHz

• Very High Light Load Efficiency (Skip Mode)

• 5mW Quiescent Power Dissipation

• ±1.5% (LDO): 100mA, 200mA (Switch Over)

• 3.3V Reference Voltage ±2.0%: 5mA

• 2.0V Reference Voltage ±1.0%: 50µA

• Temperature Compensated rDS(ON) Current Sensing

• Programmable Current Limit with Foldback Capability

• Selectable PWM, Skip or Ultrasonic Mode

• Independent PGOOD1 and PGOOD2 Comparators

• Soft-Start with Pre-Biased Output and Soft-Stop

• 1.7ms Digital Soft-Start and Independent Shutdown

• Independent ENABLE

• Thermal Shutdown

• Extremely Low Components Count

• Pb-Free Available (RoHS Compliant)

Applications

• Power Supply for Telecom/Datacom and POL

• System Requiring High Efficiency in Wide Load Range

• Compact Design with Minimum Components Count

• PDAs and Mobile Communication Devices

• 3- and 4-Cell Li+ Battery-Powered Devices

• DDR1, DDR2, and DDR3 Applications

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774 | Intersil (and design) is a registered trademark of Intersil Americas Inc.

Copyright Intersil Americas Inc. 2006, 2010. All Rights Reserved

All other trademarks mentioned are the property of their respective owners.

1 page

ISL8112

Electrical Specifications

PARAMETER

Circuit of Figure 17, and Figure 18, no load on LDO, VSEN1, VSEN2, VREF2, and VREF1, VIN = 12V,

EN2 = EN1 = VCC, VBYP = 5V, PVCC = 5V, VEN_LDO = 5V, TA = -40°C to +100°C, unless otherwise noted.

Typical values are at TA = +25°C. (Continued)

CONDITIONS

MIN

(Note 3)

MAX

TYP (Note 3) UNITS

LDO 5V Bootstrap Switch Threshold to BYP Rising edge at BYP regulation point

LDOREF = GND

4.53 4.68 4.83

V

LDO 3.3V Bootstrap Switch Threshold to BYP Rising edge at BYP regulation point

LDOREF = VCC

3.0 3.1 3.2 V

LDO 5V Bootstrap Switch Equivalent

Resistance

LDO to BYP, BYP = 5V, LDOREF > (VCC-1V) (Note 4)

0.7 1.5

Ω

LDO 3.3V Bootstrap Switch Equivalent

Resistance

LDO to BYP, BYP = 3.3V, LDOREF < 0.3V (Note 4)

1.5 3.0

Ω

VREF2 Output Voltage

No external load, VCC > 4.5V

3.235 3.300 3.365

V

No external load, VCC < 4.0V

3.220 3.300 3.380

V

VREF2 Load Regulation

0 < ILOAD < 5mA

10 mV

VREF2 Current Limit

VREF2 = GND

10 17 mA

VREF1 Output Voltage

No external load

1.980 2.000 2.020

V

VREF1 Load Regulation

0 < ILOAD < 50µA

10 mV

VREF1 Sink Current

VREF1 in regulation

10 µA

VIN Operating Supply Current

Both SMPSs on, FB1 = MODE = GND,

OUT2REF = VCC

VSEN1 = BYP = 5.3V, VSEN2 = 3.5V

25 50 µA

VIN Standby Supply Current

VIN Shutdown Supply Current

Quiescent Power Consumption

VIN = 5.5V to 25V, both SMPSs off, EN_LDO = VCC

VIN = 4.5V to 25V, EN1=EN2=EN_LDO=0V

Both SMPSs on, FB1 = MODE = GND,

OUT2REF = VCC,

VSEN1 = BYP = 5.3V, VSEN2 = 3.5V

180 250

µA

20 30 µA

5 7 mW

FAULT DETECTION

Overvoltage Trip Threshold

FB1 with respect to nominal regulation point

+8 +11 +14 %

OUT2REF with respect to nominal regulation point

+12 +16 +20

%

Overvoltage Fault Propagation Delay

FB1 or OUT2REF delay with 50mV overdrive

10 µs

PGOOD_ Threshold

FB1 or OUT2REF with respect to nominal output, falling -12 -9 -6 %

edge, typical hysteresis = 1%

PGOOD_ Propagation Delay

Falling edge, 50mV overdrive

10 µs

PGOOD_ Output Low Voltage

ISINK = 4mA

0.2 V

PGOOD_ Leakage Current

High state, forced to 5.5V

1 µA

Thermal-Shutdown Threshold

+150

°C

Output Undervoltage Shutdown Threshold FB1 or OUT2REF with respect to nominal output voltage

65

70 75 %

Output Undervoltage Shutdown Blanking

Time

From EN_ signal

10 20 30 ms

INPUTS AND OUTPUTS

FB1 Input Voltage

Low level

0.3 V

High level

VCC-1.0

V

OUT2REF Input Voltage

VSEN2 Dynamic Range, VSEN2= VOUT2REF

Fixed VSEN2 = 1.05V

0.5

3.0

2.50

VCC-

1.1

V

V

Fixed VSEN2 = 3.3V

VCC-1.0

V

5 FN6396.1

August 10, 2010

5 Page

ISL8112

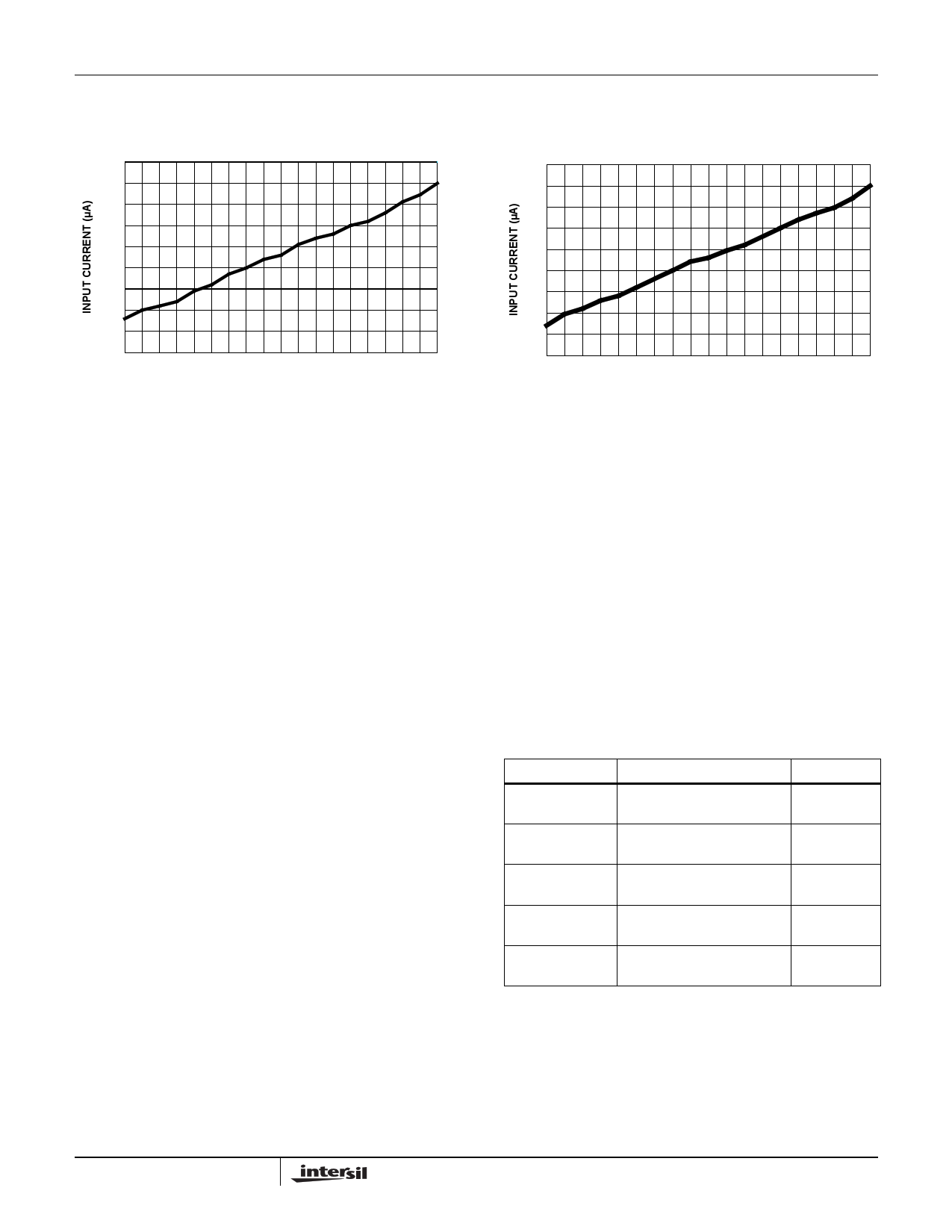

Typical Performance Curves Circuit of Figure 17 and Figure 18, no load on LDO, VSEN1, VSEN2, VREF2, and VREF1,

VIN = 12V, EN2 = EN1 = VCC, VBYP = 5V, PVCC = 5V, VEN_LDO = 5V, TA = -40°C to +100°C,

unless otherwise noted. Typical values are at TA = +25°C. (Continued)

177.5

177.0

176.5

176.0

175.5

175.0

174.5

174.0

173.5

173.0

7

9 11 13 15 17 19 21

INPUT VOLTAGE (V)

FIGURE 15. STANDBY INPUT CURRENT vs VIN

(EN = EN2 = 0, EN_LDO = VCC)

23 25

26.5

26.0

25.5

25.0

24.5

24.0

23.5

23.0

22.5

22.0

7

9 11 13 15 17 19 21

INPUT VOLTAGE (V)

FIGURE 16. SHUTDOWN INPUT CURRENT vs VIN

(EN = EN2 = EN_LDO = 0)

23 25

Typical Application Circuits

The typical application circuits are shown in Figures 17, 18

and 19. In Figure 17, the power supply system generates

1.25V/5A and dynamic voltage/10A. Figure 18 shows

system having1.5V/5A and 1.05V/5A output. The input

supply range is 5.5V to 25V. Figure 19 shows system

having1.2V/15A and 2.5V/5A output. The input supply range

is 5.5V to 25V and 4.5V to 5.5V respectively.

Detailed Description

The ISL8112 dual-buck, BiCMOS, switch-mode power-

supply controller generates logic supply voltages for

notebook computers. The ISL8112 is designed primarily for

battery-powered applications where high efficiency and low-

quiescent supply current are critical. The ISL8112 provides a

pin-selectable switching frequency, allowing operation for

200kHz/300kHz, 400kHz/300kHz, or 400kHz/500kHz on the

SMPSs.

Light-load efficiency is enhanced by automatic Idle-Mode

operation, a variable-frequency pulse-skipping mode that

reduces transition and gate-charge losses. Each step-down,

power-switching circuit consists of two n-channel MOSFETs,

a rectifier, and an LC output filter. The output voltage is the

average AC voltage at the switching node, which is

regulated by changing the duty cycle of the MOSFET

switches. The gate-drive signal to the n-channel high-side

MOSFET must exceed the battery voltage, and is provided

by a flying-capacitor boost circuit that uses a 100nF

capacitor connected to BOOT_.

Both SMPS1 and SMPS2 PWM controllers consist of a

triple-Mode feedback network and multiplexer, a multi-input

PWM comparator, high-side and low-side gate drivers and

logic. In addition, SMPS2 can also use OUT2REF to track its

output from 0.5V to 2.50V. The ISL8112 contains fault-

protection circuits that monitor the main PWM outputs for

undervoltage and overvoltage conditions. A power-on

sequence block controls the power-up timing of the main

PWMs and monitors the outputs for undervoltage faults. The

ISL8112 includes an adjustable low drop-out linear regulator.

The bias generator blocks include the linear regulator, 3.3V

precision reference, 2V precision reference and automatic

bootstrap switch over circuit.

The synchronous-switch gate drivers are directly powered

from PVCC, while the high-side switch gate drivers are

indirectly powered from PVCC through an external capacitor

and an internal Schottky diode boost circuit.

An automatic bootstrap circuit turns off the LDO linear

regulator and powers the device from BYP if LDOREF is set

to GND or VCC. See Table 1.

TABLE 1. LDO OUTPUT VOLTAGE TABLE

LDO VOLTAGE

CONDITIONS

COMMENT

VOLTAGE at BYP LDOREF < 0.3V,

BYP > 4.63V

Internal LDO is

disabled.

VOLTAGE at BYP LDOREF > VCC - 1V,

BYP > 3V

Internal LDO is

disabled.

5V

3.3V

2 x LDOREF

LDOREF < 0.3V,

BYP < 4.63V

LDOREF > VCC - 1V,

BYP < 3V

0.35V <LDOREF < 2.25V

Internal LDO is

active.

Internal LDO is

active.

Internal LDO is

active.

FREE-RUNNING, CONSTANT ON-TIME PWM

CONTROLLER WITH INPUT FEED-FORWARD

The constant on-time PWM control architecture is a

pseudo-fixed-frequency, constant on-time, current-mode

type with voltage feed forward. The constant on-time PWM

control architecture relies on the output ripple voltage to

11 FN6396.1

August 10, 2010

11 Page | ||

| Páginas | Total 27 Páginas | |

| PDF Descargar | [ Datasheet ISL8112.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ISL8112 | Main Power Supply Controllers | Intersil Corporation |

| ISL8115 | High Voltage Synchronous Buck PWM Controller | Intersil Corporation |

| ISL8117 | Synchronous Step-down PWM Controller | Intersil Corporation |

| ISL8117A | Synchronous Step-Down PWM Controller | Intersil |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |