|

|

PDF HIP1011E Data sheet ( Hoja de datos )

| Número de pieza | HIP1011E | |

| Descripción | Dual Slot PCI Hot Plug Controllers | |

| Fabricantes | Intersil Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de HIP1011E (archivo pdf) en la parte inferior de esta página. Total 15 Páginas | ||

|

No Preview Available !

®

Data Sheet

HIP1011D, HIP1011E

November 18, 2004

FN4725.5

Dual Slot PCI Hot Plug Controllers

The HIP1011D, HIP1011E are the first ICs available for

independent control of two PCI Hot-Plug slots. The

HIP1011D has all the features and functionality of two single

PCI Hot-Plug slot controllers such as the HIP1011A but in

the same foot print area. Like the single slot HIP1011B, the

HIP1011E does not monitor output voltage nor respond to

undervoltage conditions.

The HIP1011D, HIP1011E are designed to be physically

placed in close proximity to two adjacent PCI slots thus

reducing layout complexity and placement costs in

assembly. The HIP1011D, HIP1011E provides independent

power control to each slot and the addition of discrete power

MOSFETs and a few passive components creates two

complete power control solutions. The IC integrates the

+12V and -12V current sensing switches for each slot.

Overcurrent (OC) protection is provided by sensing the

voltage across external current-sense resistors. In addition,

on-chip references are used to monitor the +5V, +3.3V and

+12V outputs for undervoltage (UV) conditions *. The two

PWRON inputs control the state of the switches, one each

for slot A and slot B outputs. During an OC condition on any

www.DataSheet4U.coomutput, or a UV condition on the +5V, +3.3V or +12V outputs

*, a LOW (0V) is asserted on the associated FLTN output

and all associated switches are latched-off. The outputs

servicing the adjacent slot are unaffected.

The time to FLTN signal going LOW and MOSFET latch off

is user determined by a single capacitor from each FLTN pin

to ground. This added feature enables the HIP1011D,

HIP1011E to ignore system noise transients. The FLTN latch

is cleared when the PWRON input is toggled low again.

During initial power-up of the main VCC supply (+12V), the

PWRON input is inhibited from turning on the switches, and

the latch is held in the Reset state until the VCC input is

greater than 10V.

User programmability of the overcurrent threshold and turn-

on slew rate is provided. A resistor connected to the OCSET

pin programs the overcurrent threshold for both slots.

Capacitors connected to the gate pins set the turn-on rate.

* UV references do not apply to HIP1011E.

Features

• Independent Power Control of 2 PCI Slots

• Turn-Off Delay Time Adjustability

• Internal MOSFET Switches for +12V and -12V Outputs

• µP Interface for On/Off Control and Fault Reporting

• Adjustable Overcurrent Protection for All Eight Supplies

• Provides Fault Isolation

• Adjustable Turn-On Slew Rate

• Minimum Parts Count Solution

• No Charge Pump

• 100ns Response Time to Overcurrent

• Pb-Free Available (RoHS Compliant)

Applications

• PCI Hot-Plug

Ordering Information

PART NUMBER

HIP1011DCA*

HIP1011DCAZA*

(See Note)

HIP1011ECA*

HIP1011ECAZA*

(See Note)

TEMP.

RANGE (°C)

PACKAGE

0 to 70 28 Ld SSOP

0 to 70

28 Ld SSOP

(Pb-free)

0 to 70 28 Ld SSOP

0 to 70

28 Ld SSOP

(Pb-free)

PKG.

DWG. #

M28.15

M28.15

M28.15

M28.15

* Add “-T” suffix for tape and reel option.

NOTE: Intersil Pb-free products employ special Pb-free material sets; molding

compounds/die attach materials and 100% matte tin plate termination finish,

which are RoHS compliant and compatible with both SnPb and Pb-free

soldering operations. Intersil Pb-free products are MSL classified at Pb-free

peak reflow temperatures that meet or exceed the Pb-free requirements of

IPC/JEDEC J STD-020C.

Pinout

HIP1011D, HIP1011E (SSOP)

TOP VIEW

M12VO_2 1

M12VG_2 2

PWRON_2 3

FLTN_2 4

VSS 5

12VG_2 6

12VO_2 7

12VO_1 8

12VG_1 9

OCSET 10

FLTN_1 11

PWRON_1 12

M12VG_1 13

M12VO_1 14

28 M12VIN_2

27 3VISEN_2

26 3VS_2

25 5VISEN_2

24 5VS_2

23 3V5VG_2

22 12VIN_2

21 12VIN_1

20 3V5VG_1

19 5VS_1

18 5VISEN_1

17 3VS_1

16 3VISEN_1

15 M12VIN_1

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143 | Intersil (and design) is a registered trademark of Intersil Americas Inc.

Copyright © Intersil Americas Inc. 1999, 2000, 2004. All Rights Reserved

All other trademarks mentioned are the property of their respective owners.

1 page

HIP1011D, HIP1011E

Absolute Maximum Ratings

12VIN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.5V to +14.0V

12VO, 12VG, 3V5VG . . . . . . . . . . . . . . . . . . . . -0.5V to 12VIN+0.5V

M12VIN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -14.0V to +0.5V

M12VO, M12VG. . . . . . . . . . . . . . . . . . . . . . VM12VIN-0.5V to +0.5V

3VISEN, 5VISEN . . . . . . . . . . -0.5V to the Lesser of 12VIN or +7.0V

Voltage, Any Other Pin. . . . . . . . . . . . . . . . . . . . . . . . -0.5V to +7.0V

12VO Output Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3A

M12VO Output Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.8A

ESD Classification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2KeV (HBM)

Thermal Information

Thermal Resistance (Typical, Note 1)

θJA (°C/W)

SSOP Package . . . . . . . . . . . . . . . . . . . . . . . . . . . .

77

Maximum Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . 150°C

Maximum Storage Temperature Range . . . . . . . . . . . -65°C to 150°C

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . . 300°C

(SSOP - Lead Tips Only)

Operating Conditions

12VIN Supply Voltage Range . . . . . . . . . . . . . . . . +10.8V to +13.2V

5V and 3.3V Input Supply Tolerances. . . . . . . . . . . . . . . . . . . . . . ±10%

12VO Output Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . .0 to +0.5A

M12VO Output Current . . . . . . . . . . . . . . . . . . . . . . . . . . .0 to +0.1A

Temperature Range (TA) . . . . . . . . . . . . . . . . . . . . . . . . 0°C to 70°C

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTES:

1. θJA is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

2. All voltages are relative to GND, unless otherwise specified.

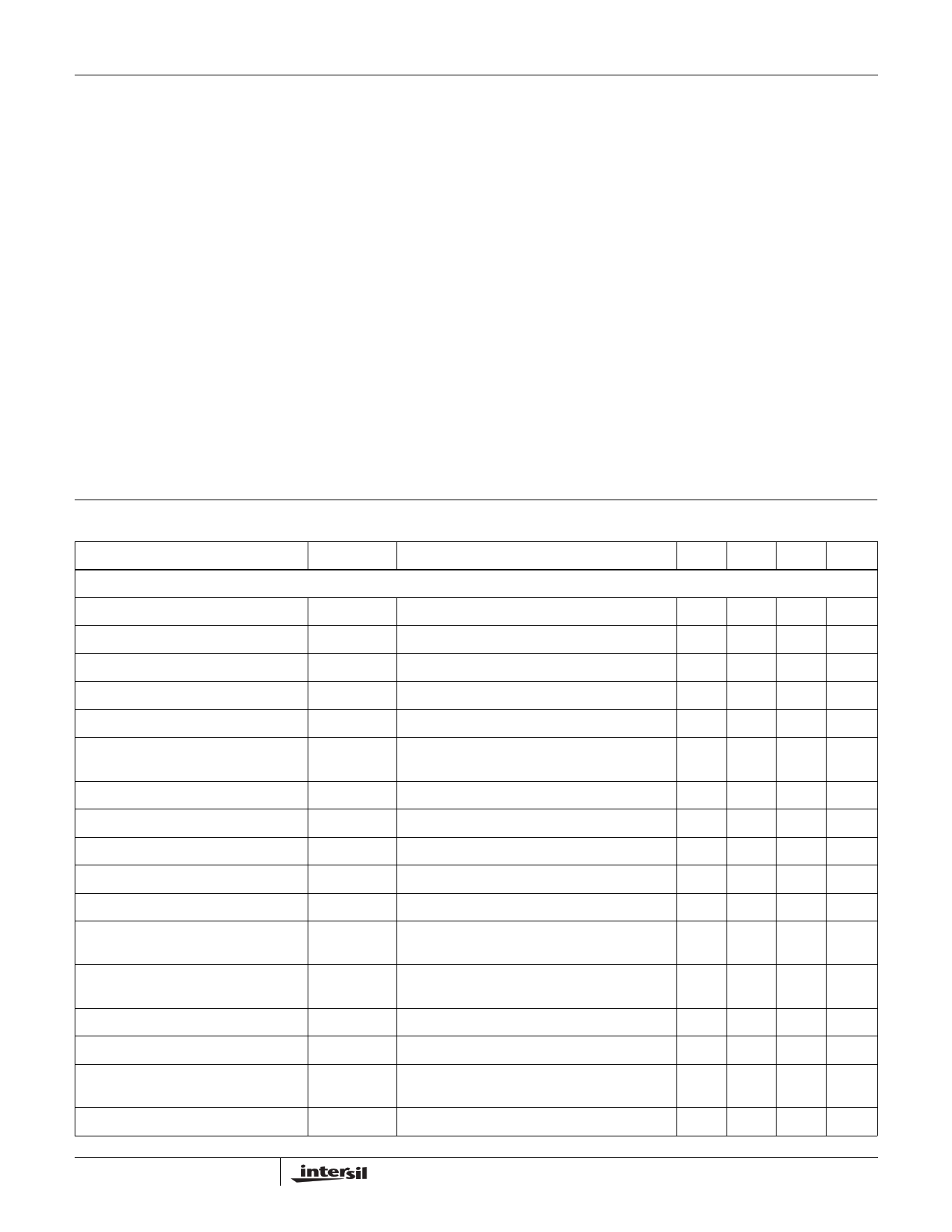

Electrical Specifications

PARAMETER

Nominal 5.0V and 3.3V Input Supply Voltages,

12VIN = 12V, M12VIN = -12V, TA = TJ = 0 to 70°C, Unless Otherwise Specified

SYMBOL

TEST CONDITIONS

MIN

5V/3.3V SUPPLY CONTROL

5V Overcurrent Threshold

5V Overcurrent Threshold Voltage

5V Overcurrent Threshold Voltage

5V Undervoltage Trip Threshold

5V Undervoltage Fault Response Time

5V Turn-On Time

(PWRON High to 5VOUT = 4.75V)

IOC5V

VOC5V_1

VOC5V_2

V5VUV

t5VUV

tON5V

See Figure 24, Typical Application

VOCSET = 0.6V

VOCSET = 1.2V

(HIP1011D only)

(HIP1011D only)

C3V5VG = 0.022µF, C5VOUT = 2000µF, RL = 1Ω

-

33

70

4.42

-

-

3V Overcurrent Threshold

3V Overcurrent Threshold Voltage

3V Overcurrent Threshold Voltage

3V Undervoltage Trip Threshold

3V Undervoltage Fault Response Time

3V5VG Undervoltage Enable Threshold

Voltage

IOC3V

See Figure 24, Typical Application

VOC3V_1 VOCSET = 0.6V

VOC3V_2 VOCSET = 1.2V

V3VUV

(HIP1011D Only)

t3VUV

(HIP1011D Only)

V3V5VGENVth (HIP1011D Only)

-

41

89

2.74

-

-

3V Turn-On Time

(PWRON High to 3VOUT = 3.00V)

3V5VG VOUT High

Gate Output Charge Current

Gate Turn-On Time

(PWRON High to 3V5VG = 11V)

tON3V

C3V5VG = 0.022µF, C3VOUT = 2000µF,

RL = 0.43Ω

Vout_hi_35VG PWRON = High, FLTN = High

IC3V5VG

tON3V5V

PWRON = High, V3V+5VG = 4V

C3V5VG = 0.033µF, 3V5VG Rising 10% to 90%

-

11.5

19

-

Gate Turn-Off Time

tOFF3V5V C3V5VG = 0.033µF, 3V5VG Falling 90% to 10%

-

TYP

8

42

80

4.65

110

6.5

10

52

98

2.86

110

9.6

6.5

11.8

25.0

280

2

MAX UNITS

-A

50 mV

90 mV

4.8 V

160 ns

- ms

-

62

108

2.98

160

-

A

mV

mV

V

ns

V

- ms

-V

29 µA

- µs

- µs

5 FN4725.5

November 18, 2004

5 Page

HIP1011D, HIP1011E

Using the HIP1011DEVAL1 Platform

General and Biasing Information

The HIP1011DEVAL1 platform (Figure 24) comes as a three

part set consisting of 1 motherboard emulator and 2 load

cards. This evaluation platform allows a designer to evaluate

and modify the performance and functionality of the

HIP1011D or HIP1011E in a simple environment.

Test point numbers (TP#) correspond to the HIP1011D/E

device (U5) pin numbers. Thus TP3 and TP12 are

PWRON_2 and PWRON_1 respectively. These 2 pins are

the HIP1011D/E control inputs for each of the 2 integrated

but independent PCI power controllers in the HIP1011D/E.

On the HIP1011DEVAL1 platform are 4 HUF76132SK8,

(11.5mΩ, 30V, 11.5A) N-Channel power MOSFETs, (Q1- Q4)

these are used as the external switches for the +5V and

+3.3V supplies to the load card connectors, P1 and P2.

Current sensing is facilitated by the four 5mΩ 1W metal strip

resistors (R1-R4), the voltages developed across the sense

resistors are compared to references on board the

HIP1011D/E.

The HIP1011DEVAL1 platform is powered through the J1 to

J5 connector jacks near the top of the board (see Table 2 for

bias voltage assignments.)

TABLE 2. HIP1011DEVAL1 BIAS ASSIGNMENTS

J1 J2 J3 J4 J5

GND

+5V

-12V

+12V

+3.3V

After properly biasing the HIP1011D/E and ensuring there is an

adequate ground return from the HIP1011DEVAL1 platform to

the power supplies, (otherwise anomalous and unpredictable

results will occur) signal the PWRON inputs low then insert the

load cards as shown in Figure 15. Signaling either or both

PWRON pins high (>2.4V) will turn on the appropriate FET

switches and apply voltage to the load cards.

LOAD CARDS

HIP1011D

FIGURE 15. CORRECT INSTALLATION OF LOAD CARDS

* The HIP1011DEVAL board is supplied with a HIP1011D

installed and in addition a loose packed HIP1011E.

Evaluating Time Delay to Latch-Off

Provided for delay to latch-off evaluation are 2 locations for

SMD capacitors, C7 and C8. Filling these locations places a

capacitor to ground from each of the HIP1011D/E FLTN pins

thus tailoring the FLTN signal going low ramp rate. This

provides a delay to the fault signal latch-off threshold

voltage, FLTN Vth. By increasing this time the HIP1011D

delays immediate latch-off of the bus supply switches, thus

ignoring transient OC and UV conditions. See Table 3

illustrating the time it takes for switch gate turn-off from the

FLTN start of response to an OC or UV condition. The FLTN

response to an OC or UV condition is 110ns. See Figures 20

through 23 for waveforms.

The intent of any protection device is to isolate the supply

quickly so a faulty card does not drag down a supply. A

longer latch-off delay results in less isolation from a faulty

card to supply.

C7 AND C8 VALUE

FLTN to Gate Response

TABLE 3.

OPEN 0.001µF 0.01µF

0.1µs 0.44µs 2.9µs

0.1µF

28µs

FLTN

3V5VG

FLTN, Vth

FIGURE 16. TIMING DIAGRAM

10ms

1ms

100µs

10µs

1µs

100ns

10ns

1ns

OPEN

0.001µF

0.01µF

0.1µF

1µF 10µF

FIGURE 17. TYPICAL OC/UV TO VG RESPONSE vs FLTN CAP

11 FN4725.5

November 18, 2004

11 Page | ||

| Páginas | Total 15 Páginas | |

| PDF Descargar | [ Datasheet HIP1011E.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HIP1011 | PCI Hot Plug Controller | Intersil Corporation |

| HIP1011A | PCI Hot Plug Controller | Intersil Corporation |

| HIP1011B | PCI Hot Plug Controller | Intersil Corporation |

| HIP1011D | Dual PCI Hot Plug Controller | Intersil Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |