|

|

PDF UJA1069 Data sheet ( Hoja de datos )

| Número de pieza | UJA1069 | |

| Descripción | LIN fail-safe system basis chip | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de UJA1069 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

UJA1069

LIN fail-safe system basis chip

Rev. 04 — 28 October 2009

Product data sheet

1. General description

The UJA1069 fail-safe System Basis Chip (SBC) replaces basic discrete components

which are common in every Electronic Control Unit (ECU) with a Local Interconnect

Network (LIN) interface. The fail-safe SBC supports all networking applications which

control various power and sensor peripherals by using LIN as a local sub-bus. The

fail-safe SBC contains the following integrated devices:

• LIN transceiver compliant with LIN 2.0 and SAE J2602, and compatible with LIN 1.3

• Advanced independent watchdog

• Dedicated voltage regulator for microcontroller

• Serial peripheral interface (full duplex)

• Local wake-up input port

• Inhibit/limp-home output port

In addition to the advantages of integrating these common ECU functions in a single

package, the fail-safe SBC offers an intelligent combination of system-specific functions

such as:

• Advanced low-power concept

• Safe and controlled system start-up behavior

• Advanced fail-safe system behavior that prevents any conceivable deadlock

• Detailed status reporting on system and sub-system levels

The UJA1069 is designed to be used in combination with a microcontroller and a LIN

controller. The fail-safe SBC ensures that the microcontroller is always started up in a

defined manner. In failure situations the fail-safe SBC will maintain the microcontroller

function for as long as possible, to provide full monitoring and software driven fall-back

operation.

The UJA1069 is designed for 14 V single power supply architectures and for 14 V and

42 V dual power supply architectures.

1 page

NXP Semiconductors

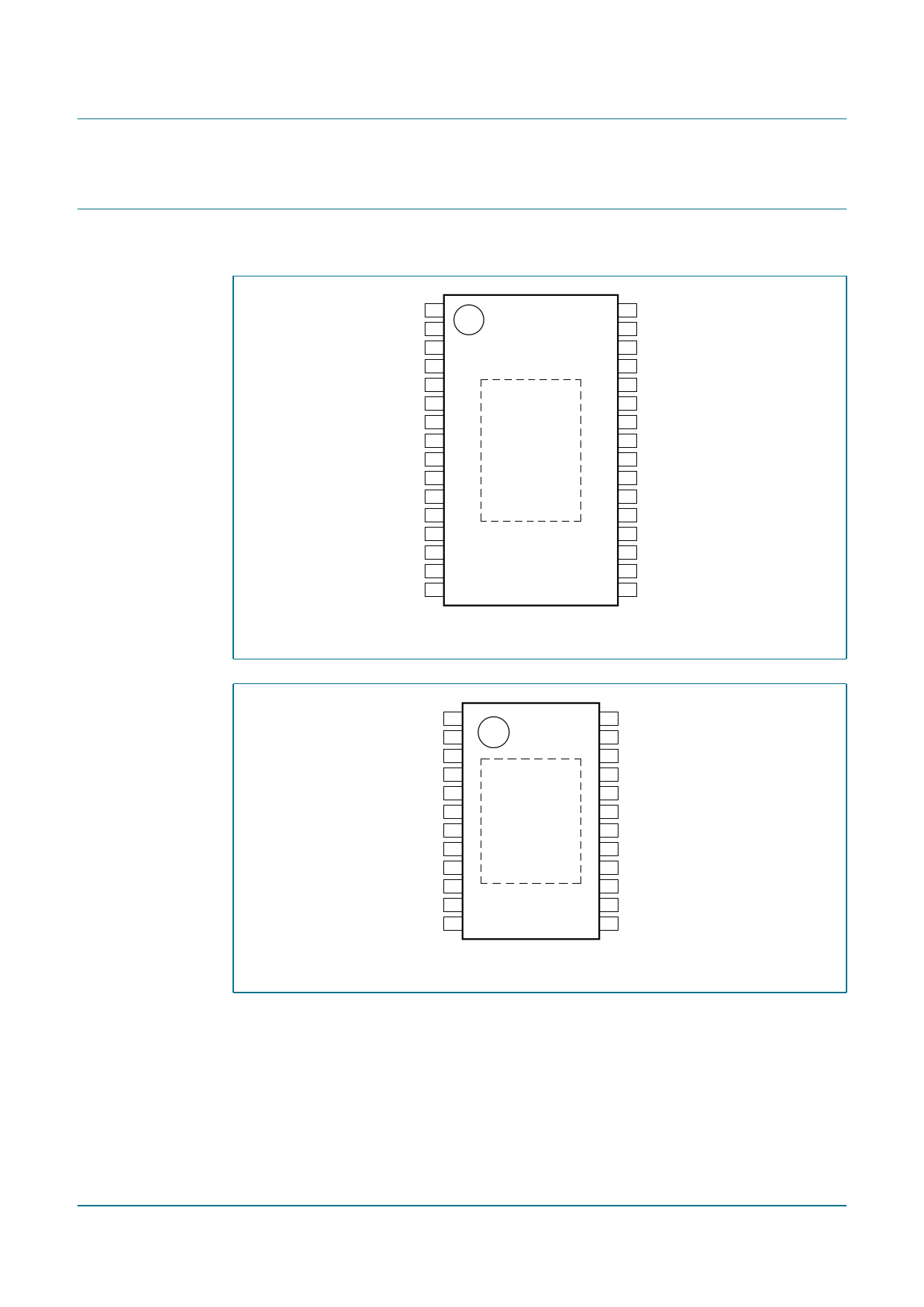

5. Pinning information

5.1 Pinning

UJA1069

LIN fail-safe system basis chip

n.c. 1

n.c. 2

TXDL 3

V1 4

RXDL 5

RSTN 6

INTN 7

EN 8

SDI 9

SDO 10

SCK 11

SCS 12

n.c. 13

n.c. 14

n.c. 15

TEST 16

UJA1069TW

32 BAT42

31 SENSE

30 V3

29 SYSINH

28 n.c.

27 BAT14

26 RTLIN

25 LIN

24 n.c.

23 GND

22 n.c.

21 n.c.

20 n.c.

19 n.c.

18 WAKE

17 INH/LIMP

001aad676

Fig 2. Pin configuration (HTSSOP32)

n.c. 1

TXDL 2

V1 3

RXDL 4

RSTN 5

INTN 6

EN 7

SDI 8

SDO 9

SCK 10

SCS 11

TEST 12

UJA1069TW24

24 BAT42

23 SENSE

22 V3

21 SYSINH

20 n.c.

19 BAT14

18 RTLIN

17 LIN

16 n.c.

15 GND

14 WAKE

13 INH/LIMP

001aad677

Fig 3. Pin configuration (HTSSOP24)

UJA1069_4

Product data sheet

Rev. 04 — 28 October 2009

© NXP B.V. 2009. All rights reserved.

5 of 64

5 Page

NXP Semiconductors

UJA1069

LIN fail-safe system basis chip

The following operations are possible from Standby mode:

• Cyclic wake-up by the watchdog via an interrupt signal to the microcontroller (the

microcontroller is triggered periodically and checked for the correct response)

• Cyclic wake-up by the watchdog via a reset signal (a reset is performed periodically;

the SBC provides information about the reset source to allow different start

sequences after reset)

• Wake-up by activity on the LIN-bus via an interrupt signal to the microcontroller

• Wake-up by bus activity on the LIN-bus via a reset signal

• Wake-up by increasing the microcontroller supply current without a reset signal

(where a stable supply is needed for the microcontroller RAM contents to remain valid

and wake-up from an external application not connected to the SBC)

• Wake-up by increasing the microcontroller supply current with a reset signal

• Wake-up due to a falling edge at pin WAKE forcing an interrupt to the microcontroller

• Wake-up due to a falling edge at pin WAKE forcing a reset signal

6.2.6 Sleep mode

In Sleep mode the microcontroller power supply (V1) and the INH/LIMP controlled

external supplies are switched off entirely, resulting in minimum system power

consumption. In this mode, the watchdog runs in Time-out mode or is completely off.

Entering Sleep mode results in an immediate LOW level on pin RSTN, thus stopping any

operation of the microcontroller. The INH/LIMP output is floating in parallel and pin V1 is

disabled. It is also possible for V3 to be ON, OFF or in Cyclic mode to supply external

wake-up switches.

If the watchdog is not disabled in software, it will continue to run and force a system reset

upon overflow of the programmed period time. The SBC enters Start-up mode and pin V1

becomes active again. This behavior can be used for a cyclic wake-up from Sleep mode.

Depending on the application, the following operations can be selected from Sleep mode:

• Cyclic wake-up by the watchdog (only in Time-out mode); a reset is performed

periodically, the SBC provides information about the reset source to allow different

start sequences after reset

• Wake-up by activity on the LIN-bus or falling edge at pin WAKE

• An overload on V3, only if V3 is in a cyclic or in continuously ON mode

6.2.7 Flash mode

Flash mode can only be entered from Normal mode by entering a specific Flash mode

entry sequence. This fail-safe control sequence comprises three consecutive write

accesses to the Mode register, within the legal windows of the watchdog, using the

operating mode codes 111, 001 and 111 respectively. As a result of this sequence, the

SBC will enter Start-up mode and perform a system reset with the related reset source

information (bits RSS[3:0] = 0110).

UJA1069_4

Product data sheet

Rev. 04 — 28 October 2009

© NXP B.V. 2009. All rights reserved.

11 of 64

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet UJA1069.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| UJA1061 | Fault-tolerant CAN/LIN fail-safe system basis chip | NXP Semiconductors |

| UJA1061 | Low speed CAN/LIN system basis chip | Philips |

| UJA1061TW | Fault-tolerant CAN/LIN fail-safe system basis chip | NXP Semiconductors |

| UJA1061TW | Low speed CAN/LIN system basis chip | Philips |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |