|

|

PDF ISL12027 Data sheet ( Hoja de datos )

| Número de pieza | ISL12027 | |

| Descripción | Real Time Clock/Calendar | |

| Fabricantes | Intersil Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ISL12027 (archivo pdf) en la parte inferior de esta página. Total 28 Páginas | ||

|

No Preview Available !

®

Data Sheet

ISL12027, ISL12027A

August 12, 2010

FN8232.8

Real Time Clock/Calendar with EEPROM

The ISL12027 device is a low power real time clock with

timing and crystal compensation, clock/calender, power-fail

indicator, two periodic or polled alarms, intelligent battery

backup switching, CPU Supervisor and integrated 512x8-bit

EEPROM, in 16 Byte per page format.

The oscillator uses an external, low-cost 32.768kHz crystal.

The real time clock tracks time with separate registers for

hours, minutes, and seconds. The device has calendar

registers for date, month, year and day of the week. The

calendar is accurate through 2099, with automatic leap year

correction.

The ISL12027 and ISL12027A Power Control Settings are

different. The ISL12027 uses the Legacy Mode Setting, and

the ISL12027A uses the Standard Mode Setting.

Applications that have VBAT > VDD will require only the

ISL12027A. Please refer to“Power Control Operation” on

page 15 for more details. Also, please refer to “I2C

Communications During Battery Backup and LVR Operation”

on page 24 for important details.

Pinouts

ISL12027, ISL12027A

(8 LD TSSOP)

TOP VIEW

VBAT

VDD

X1

X2

1

2

3

4

8 SCL

7 SDA

6 GND

5 RESET

ISL12027, ISL12027A

(8 LD SOIC)

TOP VIEW

X1

X2

RESET

GND

1

2

3

4

8 VDD

7 VBAT

6 SCL

5 SDA

Features

• Real Time Clock/Calendar

- Tracks Time in Hours, Minutes and Seconds

- Day of the Week, Day, Month and Year

• Two Non-Volatile Alarms

- Settable on the Second, Minute, Hour, Day of the Week,

Day, or Month

- Repeat Mode (Periodic Interrupts)

• Automatic Backup to Battery or SuperCap

• On-Chip Oscillator Compensation

- Internal Feedback Resistor and Compensation

Capacitors

- 64 Position Digitally Controlled Trim Capacitor

- 6 Digital Frequency Adjustment Settings to ±30ppm

• 512x8-Bits of EEPROM

- 16-Byte Page Write Mode (32 total pages)

- 8 Modes of BlockLock™ Protection

- Single Byte Write Capability

• High Reliability

- Data Retention: 50 years

- Endurance: >2,000,000 Cycles Per Byte

• I2C-bus™ Interface

- 400kHz Data Transfer Rate

• 800nA Battery Supply Current

• Package Options

- 8 Ld SOIC and 8 Ld TSSOP Packages

• Pb-Free (RoHS Compliant)

Applications

• Utility Meters

• HVAC Equipment

• Audio/Video Components

• Modems

• Network Routers, Hubs, Switches, Bridges

• Cellular Infrastructure Equipment

• Fixed Broadband Wireless Equipment

• Pagers/PDA

• POS Equipment

• Test Meters/Fixtures

• Office Automation (Copiers, Fax)

• Home Appliances

• Computer Products

• Other Industrial/Medical/Automotive

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774 | Intersil (and design) is a registered trademark of Intersil Americas Inc.

I2C-bus™ is a trademark of NXP B.V., BlockLock™ is a trademark of Intersil Corporation or one of its subsidiaries

Copyright Intersil Americas Inc. 2005, 2006, 2010. All Rights Reserved

All other trademarks mentioned are the property of their respective owners.

1 page

ISL12027, ISL12027A

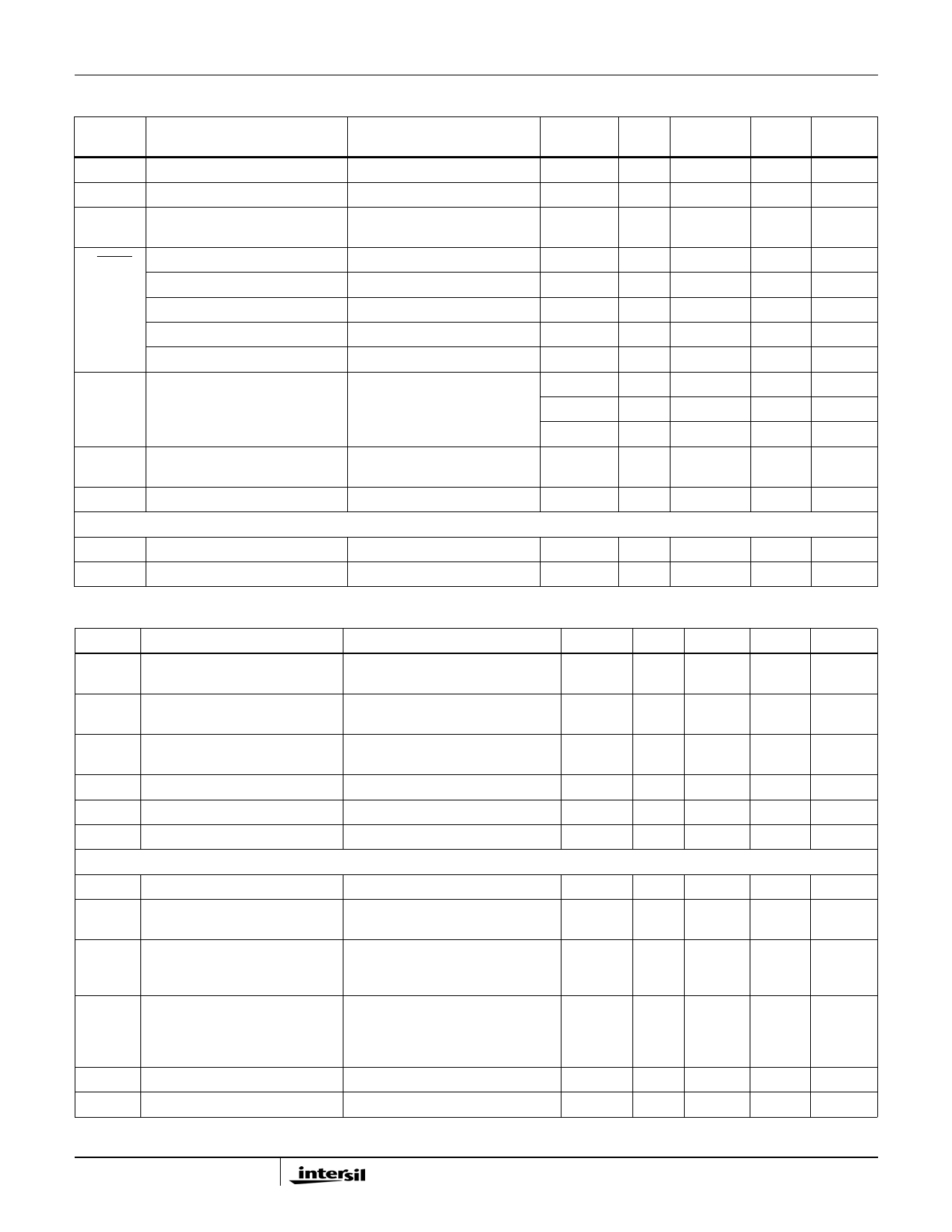

Watchdog Timer/Low Voltage Reset Parameters

SYMBOL

PARAMETER

CONDITIONS

tRPD

tPURST

VRVALID

VDD Detect to RESET LOW

Power-up Reset Time-Out Delay

Minimum VDD for Valid RESET

Output

VRESET ISL12027-4.5A Reset Voltage Level

ISL12027 Reset Voltage Level

ISL12027-3 Reset Voltage Level

ISL12027-2.7A Reset Voltage Level

ISL12027-2.7 Reset Voltage Level

tWDO Watchdog Timer Period

32.768kHz crystal between X1

and X2

tRST

Watchdog Timer Reset Time-Out 32.768kHz crystal between X1

Delay

and X2

tRSP I2C Interface Minimum Restart Time

EEPROM SPECIFICATIONS

EEPROM Endurance

EEPROM Retention

Temperature ≤ +75°C

MIN

(Note 16)

TYP

(Note 5)

500

MA

(Note 16)

100 250 400

1.0

UNITS

ns

ms

V

NOTES

13

4.59 4.64 4.69

4.33 4.38 4.43

3.04 3.09 3.14

2.87 2.92 2.97

2.58 2.63 2.68

1.70 1.75 1.801

725 750 775

225 250 275

225 250 275

V

V

V

V

V

s

ms

ms

ms

1.2 µs

>2,000,000

50

Cycles

Years

Serial Interface (I2C) Specifications

SYMBOL

PARAMETER

CONDITIONS

MIN

VIL SDA, and SCL Input Buffer LOW SBIB = 1 (Under VDD mode)

Voltage

-0.3

VIH SDA, and SCL Input Buffer HIGH SBIB = 1 (Under VDD mode)

Voltage

0.7xVDD

Hysteresis SDA and SCL Input Buffer

Hysteresis

SBIB = 1 (Under VDD mode)

0.05xVDD

VOL SDA Output Buffer LOW Voltage IOL = 4mA

ILI Input Leakage Current on SCL

VIN = 5.5V

ILO I/O Leakage Current on SDA

VIN = 5.5V

0

TIMING CHARACTERISTICS

fSCL SCL Frequency

tIN Pulse Width Suppression Time at Any pulse narrower than the max spec

SDA and SCL Inputs

is suppressed.

tAA SCL Falling Edge to SDA Output SCL falling edge crossing 30% of VDD,

Data Valid

until SDA exits the 30% to 70% of VDD

window.

tBUF

Time the Bus Must be Free Before

the Start of a New Transmission

SDA crossing 70% of VDD during a

STOP condition, to SDA crossing 70%

of VDD during the following START

condition.

1300

tLOW

tHIGH

Clock LOW Time

Clock HIGH Time

Measured at the 30% of VDD crossing.

Measured at the 70% of VDD crossing.

1300

600

TYP MAX UNITS

0.3xVDD

V

VDD + 0.3

V

V

0.4

0.1 10

0.1 10

V

µA

µA

400 kHz

50 ns

900 ns

ns

ns

ns

NOTES

5 FN8232.8

August 12, 2010

5 Page

ISL12027, ISL12027A

0 to 23 (with MIL = 1), DT (Date) is 1 to 31, MO (Month) is 1

to 12, YR (Year) is 0 to 99.

DW: Day of the Week Register

This register provides a Day of the Week status and uses

three bits DY2 to DY0 to represent the seven days of the

week. The counter advances in the cycle 0-1-2-3-4-5-6-0-1-

2-… The assignment of a numerical value to a specific day

of the week is arbitrary and may be decided by the system

software designer. The default value is defined as ‘0’.

Y2K: Year 2000 Register

Can have value 19 or 20. As of the date of the introduction of

this device, there would be no real use for the value 19 in a

true real time clock, however.

24 Hour Time

If the MIL bit of the HR register is 1, the RTC uses a 24-hour

format. If the MIL bit is 0, the RTC uses a 12-hour format and

H21 bit functions as an AM/PM indicator with a ‘1’,

representing PM. The clock defaults to standard time with

H21 = 0.

Leap Years

Leap years add the day February 29 and are defined as

those years that are divisible by 4.

Status Register (SR) (Volatile)

The Status Register is located in the CCR memory map at

address 003Fh. This is a volatile register only and is used to

control the WEL and RWEL write enable latches, read power

status and two alarm bits. This register is separate from both

the array and the Clock/Control Registers (CCR).

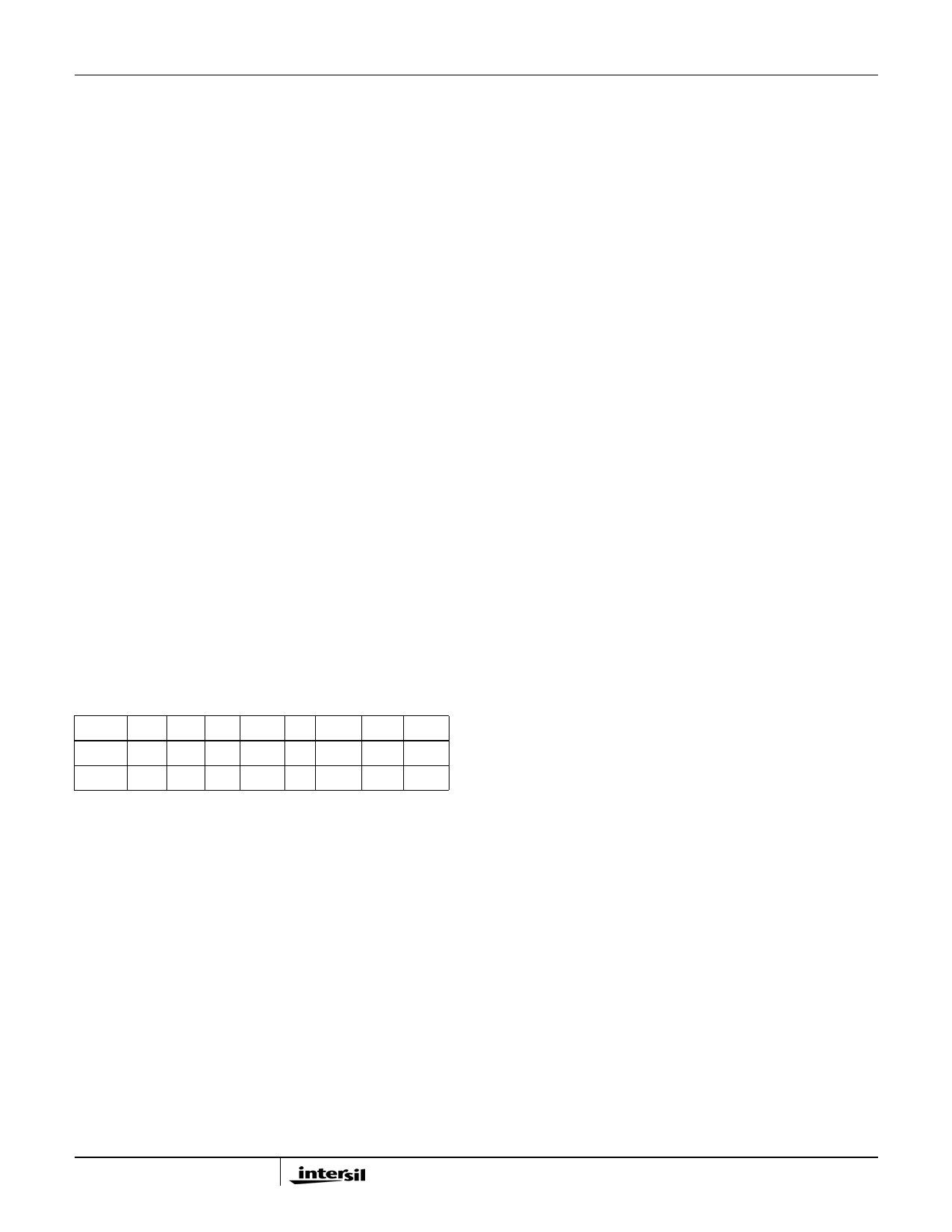

TABLE 1. STATUS REGISTER (SR)

ADDR 7

65

43

2

1

0

003Fh BAT AL1 AL0 OSCF 0 RWEL WEL RTCF

Default 0

00

00

0

0

1

BAT: Battery Supply

This bit set to “1” indicates that the device is operating from

VBAT, not VDD. It is a read-only bit and is set/reset by

hardware (ISL12027 internally). Once the device begins

operating from VDD, the device sets this bit to “0”.

AL1, AL0: Alarm Bits

These bits announce if either alarm 0 or alarm 1 match the

real time clock. If there is a match, the respective bit is set to

‘1’. The falling edge of the last data bit in a SR Read

operation resets the flags. Note: Only the AL bits that are set

when an SR read starts will be reset. An alarm bit that is set

by an alarm occurring during an SR read operation will

remain set after the read operation is complete.

OSCF: Oscillator Fail Indicator

This bit is set to “1” if the oscillator is not operating, or is

operating but has clock jitter which does not affect the

accuracy of RTC counting. The bit is set to “0” if the oscillator

is functioning and does not have clock jitter. This bit is read

only, and is set/reset by hardware.

RWEL: Register Write Enable Latch

This bit is a volatile latch that powers up in the LOW

(disabled) state. The RWEL bit must be set to “1” prior to any

writes to the Clock/Control Registers. Writes to RWEL bit do

not cause a non-volatile write cycle, so the device is ready

for the next operation immediately after the stop condition. A

write to the CCR requires both the RWEL and WEL bits to be

set in a specific sequence.

WEL: Write Enable Latch

The WEL bit controls the access to the CCR during a write

operation. This bit is a volatile latch that powers up in the

LOW (disabled) state. While the WEL bit is LOW, writes to

the CCR address will be ignored, although acknowledgment

is still issued. The WEL bit is set by writing a “1” to the WEL

bit and zeroes to the other bits of the Status Register. Once

set, WEL remains set until either reset to 0 (by writing a “0”

to the WEL bit and zeroes to the other bits of the Status

Register) or until the part powers up again. Writes to WEL bit

do not cause a non-volatile write cycle, so the device is

ready for the next operation immediately after the stop

condition.

RTCF: Real Time Clock Fail Bit

This bit is set to a “1” after a total power failure. This is a read

only bit that is set by hardware (ISL12027 internally) when

the device powers up after having lost all power to the device

(both VDD and VBAT go to 0V). The bit is set regardless of

whether VDD or VBAT is applied first. The loss of only one of

the supplies does not set the RTCF bit to “1”. On power up

after a total power failure, all registers are set to their default

states and the clock will not increment until at least one byte

is written to the clock register. The first valid write to the RTC

section after a complete power failure resets the RTCF bit to

“0” (writing one byte is sufficient).

Unused Bits:

Bit 3 in the SR is not used, but must be zero. The Data Byte

output during a SR read will contain a zero in this bit

location.

11 FN8232.8

August 12, 2010

11 Page | ||

| Páginas | Total 28 Páginas | |

| PDF Descargar | [ Datasheet ISL12027.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ISL12020 | Low Power RTC | Intersil Corporation |

| ISL12020M | Low Power RTC | Intersil Corporation |

| ISL12021 | Real Time Clock | Intersil Corporation |

| ISL12022 | Low Power RTC | Intersil |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |