|

|

PDF FS8107E Data sheet ( Hoja de datos )

| Número de pieza | FS8107E | |

| Descripción | Low Power Phase-Locked Loop IC | |

| Fabricantes | Himark | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de FS8107E (archivo pdf) en la parte inferior de esta página. Total 10 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

FS8107E Low Power Phase-Locked Loop IC

the wireless IC company

HiMARK Technology, Inc. reserves the right to change the product described in this datasheet. All information con-

tained in this datasheet is subject to change without prior notice. HiMARK Technology, Inc. assumes no responsibility

for the use of any circuits shown in this datasheet.

Description

The FS8107E is a serial data input, phase-locked loop IC with programmable input and

reference frequency dividers. When combined with a VCO, the FS8107E becomes the

core of a very low power frequency synthesizer well-suited for mobile communication

applications such as paging systems. Compared to the FS8100, the FS8107E is housed

in a smaller package and also implements a separate pin for stand-by control.

Features

High maximum input operating frequency — 100 MHz at VDD1 = 1.0 V

Up to 22 MHz internal crystal oscillator reference frequency at VDD1 = 1.0 V

Extremely low current consumption (IDD,total typically 0.4 mA at fFIN = 90 MHz)

16-bit programmable input frequency divider (including a ÷ 32/33 prescaler) with

divide ratio range from 992 to 65535

13-bit programmable reference frequency divider (including a ÷ 8 prescaler) with

divide ratio range from 40 to 65528

Optional lock detector output

Charge pump output for passive low-pass filter

Quick-lock signal output for faster locking

Separate pin for stand-by control

TSSOP 16L package (0.65mm pitch)

Applications

Pager

Wireless communication system

Page 1

June 2001

1 page

the wireless IC company

FS8107E

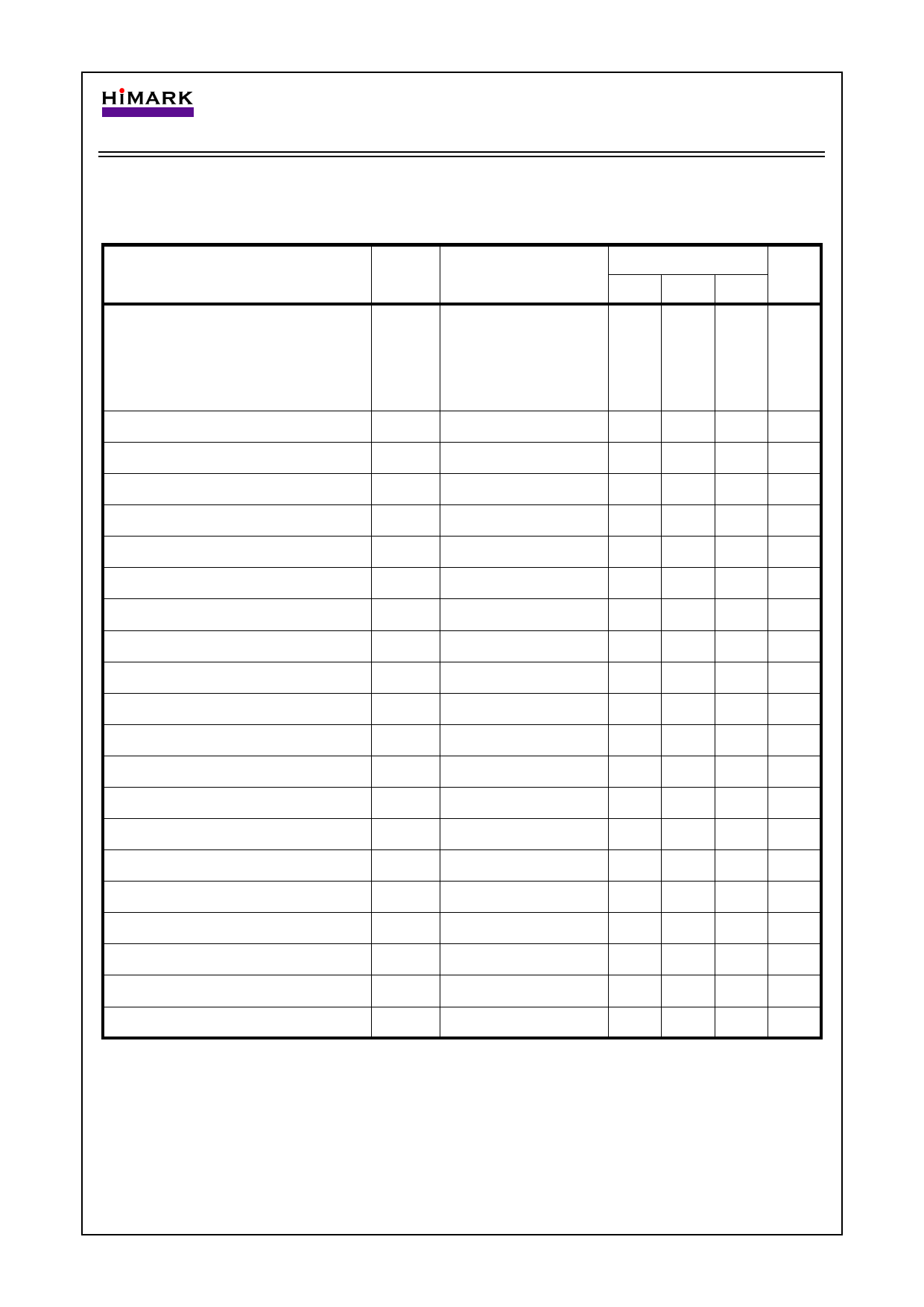

Electrical Characteristics

(VDD1 = 0.95 to 2.0 V, VDD2 = 2.7 to 3.3 V, VSS = 0 V, TA = 0 to 60°C unless otherwise noted)

Parameter

Current consumption

Standby current consumption (IDD2)

FIN max. operating frequency

FIN min. operating frequency

XIN max. operating frequency

XIN min. operating frequency

FIN input voltage swing

XIN input voltage swing

CLK, DATA, LE logic LOW input voltage

CLK, DATA, LE logic HIGH input voltage

XIN logic LOW input current

XIN logic HIGH input current

FIN logic LOW input current

FIN logic HIGH input current

DO logic LOW output current

DO logic HIGH output current

LD, FV, FR logic LOW output current

LD, FV, FR logic HIGH output current

DATA to CLK setup time

CLK to LE setup time

Hold time

Symbol

Condition

IDD,total

IDD,standby

fFIN,max

fFIN,min

fXIN,max

fXIN,min

VFIN

VXIN

VIL

VIH

IIL,XIN

IIH,XIN

IIL,FIN

IIH,FIN

IOL,DOP

IOH,DOP

IOL

IOH

tSU1

tSU2

tHOLD

VDD1 = 1.0 V, OPR=”H”,

VFIN = 0.3 Vpk-pk sinusoid,

fFIN = 100 MHz,

VXIN = 0.3 Vpk-pk sinusoid,

fXIN = 12.8 MHz

VDD1 = 0 V, OPR=”L”

VFIN = 0.3 Vpk-pk sinusoid

VFIN = 0.3 Vpk-pk sinusoid

VXIN = 0.3 Vpk-pk sinusoid

VXIN = 0.3 Vpk-pk sinusoid

VIL = 0 V

VIH = VDD1

VIL = 0 V

VIH = VDD1

VOL = 0.4 V

VOH = VDD2 – 0.4 V

VOL = 0.4 V

VOH = VDD2 – 0.4 V

Value

min. typ. max.

Unit

0.40 1.10 mA

10 µA

100 MHz

40 MHz

22 MHz

7 MHz

0.3 Vpk-pk

0.3 Vpk-pk

0.3 V

1.5 V

10 µA

10 µA

60 µA

60 µA

1.0 mA

1.0 mA

0.1 mA

0.1 mA

2 µs

2 µs

2 µs

Page 5

June 2001

5 Page | ||

| Páginas | Total 10 Páginas | |

| PDF Descargar | [ Datasheet FS8107E.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| FS8107E | Low Power Phase-Locked Loop IC | Himark |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |