|

|

PDF IS41LV32256 Data sheet ( Hoja de datos )

| Número de pieza | IS41LV32256 | |

| Descripción | EDO DYNAMIC RAM | |

| Fabricantes | ISSI | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de IS41LV32256 (archivo pdf) en la parte inferior de esta página. Total 19 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

IS41LV32256

256K x 32 (8-Mbit) EDO DYNAMIC RAM

3.3V, 100/83/66 MHz

ISSI®

SEPTEMBER 2000

FEATURES

• 262,144-word by 32-bit organization

• Single +3.3V ± 0.3V power supply

• Four CAS inputs for Byte Write and Byte Read

control

• Refresh modes: RAS-Only, CAS-Before-RAS (CBR),

and Hidden

• 512-cycle refresh in 8 ms

• Fast Page Mode with Extended Data Out

• 100-pin PQFP, TQFP package

DESCRIPTION

The ISSI IS41LV32256 is organized in a 262,122 x 32-bit

CMOS Dynamic Random Access Memory. Four CAS signals

facilitate execution of Byte Read and Byte Write operations.

A very fast EDO cycle time of 10 ns allows an operating

frequency of 100 MHz and makes the IS41LV32256 an ideal

frame buffer memory for graphics applications.

The IS41LV32256 is compatible with JEDEC standard

SGRAMs. This 8-Mbit EDO memory offers a significantly

lower latency and a faster memory cycle than the SGRAM.

ISSI's IS41LV32256 3.3V 256K x 32 device is pin/voltage

compatible with all standard SGRAM parts.

The IS41LV32256 is available in a 100-pin PQFP and TQFP

package.

KEY TIMING PARAMETERS

Parameter

-28 -30 -35 Unit

Max. RAS Access Time (tRAC)

Max. CAS Access Time (tCAC)

28 30 35 ns

9 9 10 ns

Max. Column Address Access Time (tAA) 15 16 18 ns

Max. OE Access Time (tOE)

9 9 10 ns

Min. Read/Write Cycle Time (tRC)

48 53 60 ns

Min. EDO Cycle Time (tPC)

12 12 15 ns

ISSI reserves the right to make changes to its products at any time without notice in order to improve design and supply the best possible product. We assume no responsibility for any errors

which may appear in this publication. © Copyright 2000, Integrated Silicon Solution, Inc.

Integrated Silicon Solution, Inc.

Rev. A

09/29/00

1

1 page

IS41LV32256

POWER-ON

The initial application of the VCC supply requires a 200-µs

wait followed by a minimum of any eight initialization

cycles containing a RAS clock. During Power-On, the VCC

current is dependent on the input levels of RAS and CAS.

It is recommended that RAS and CAS track with VCC or be

held at a valid VIH during Power-On to avoid current

surges.

ABSOLUTE MAXIMUM RATINGS(1)

Symbol Parameters

Rating

Unit

tA Ambient Temperature Under Bias

tSTG Storage Temperature

VT Voltage Relative to GND

IOUT Data Output Current

PD Power Dissipation

–1.0 to +80

–50 to +125

–1.0 to +5.5

50

1.0

°C

°C

V

mA

W

Note:

1. Stress greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent

damage to the device. This is a stress rating only and functional operation of the device at these

or any other conditions above those indicated in the operational sections of this specification is

not implied. Exposure to absolute maximum rating conditions for extended periods may affect

reliability.

RECOMMENDED OPERATING CONDITIONS(1) (TA = 0°C to 70°C)

Symbol

Parameter

VCC Power Supply

VIH Input High Voltage

VIL Input Low Voltage

Note:

1. Voltages are referenced to GND.

Min.

3.0

2.4

–0.5

Typ.

3.3

—

—

Max.

3.6

VCC + 0.5

0.4

Unit

V

V

V

CAPACITANCE(1,2)

Symbol

CIN

CIO

Parameter

Input Capacitance

Data Input/Output Capacitance

Notes:

1. Capacitance is sampled and 100% tested.

2. Test conditions: TA = 25°C, f = 1 MHz, VCC = 3.3V.

Integrated Silicon Solution, Inc.

Rev. A

09/29/00

Max.

5

7

Unit

pF

pF

ISSI®

5

5 Page

IS41LV32256

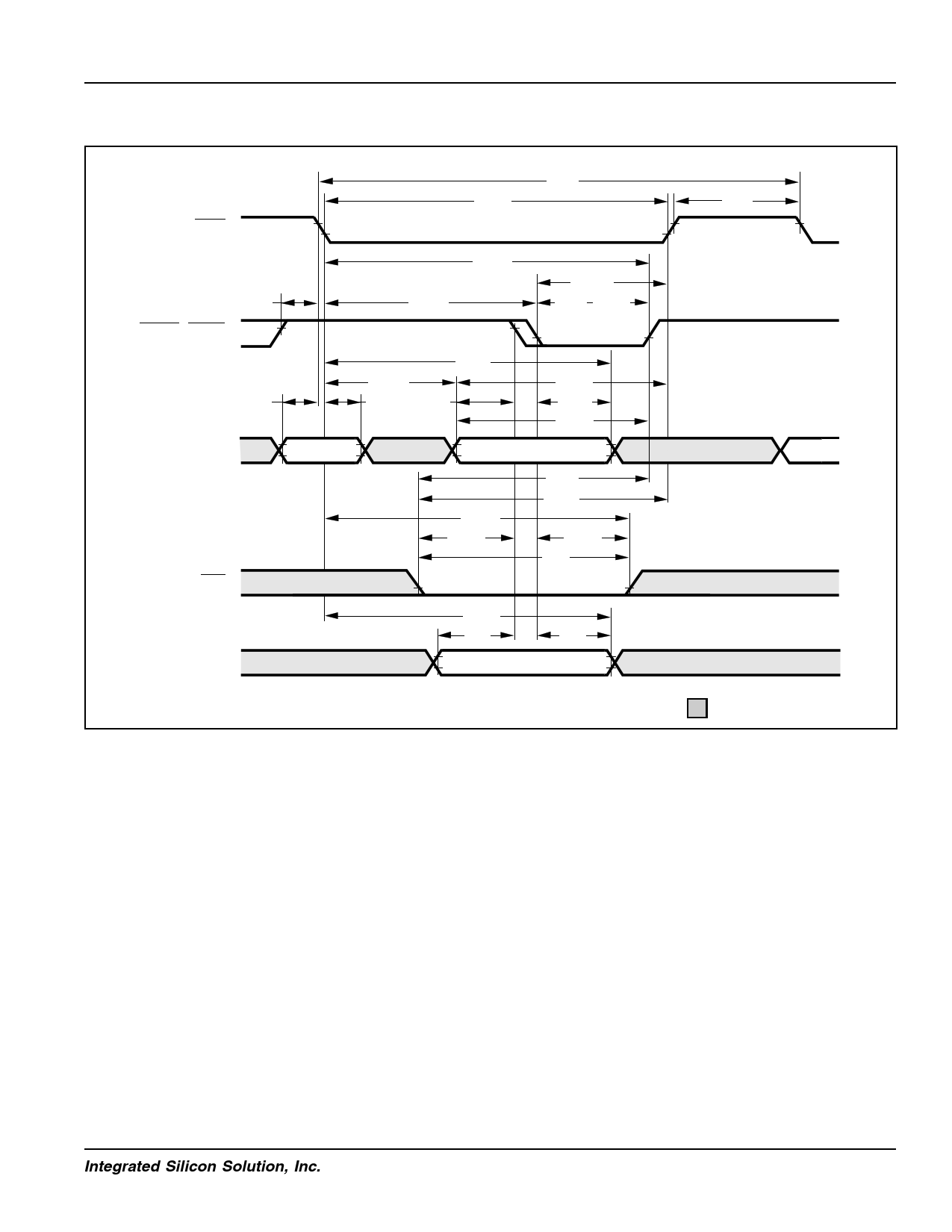

EARLY WRITE CYCLE (OE = DON'T CARE)

RAS

tCRP

CAS0-CAS3

tASR

ADDRESS

Row

WE

I/O

tRAS

tRC

tRCD

tCSH

tRSH

tCAS tCLCH

tRAD

tRAH

tASC

tAR

tRAL

tCAH

tACH

Column

tWCR

tWCS

tCWL

tRWL

tWCH

tWP

tDHR

tDS

tDH

Valid Data

ISSI®

tRP

Row

Don't Care

Integrated Silicon Solution, Inc.

Rev. A

09/29/00

11

11 Page | ||

| Páginas | Total 19 Páginas | |

| PDF Descargar | [ Datasheet IS41LV32256.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| IS41LV32256 | EDO DYNAMIC RAM | ISSI |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |