|

|

PDF IS25C16 Data sheet ( Hoja de datos )

| Número de pieza | IS25C16 | |

| Descripción | (IS25C08 / IS25C16) 8K-BIT/16K-BIT SPI SERIAL ELECTRICALLY ERASABLE PROM | |

| Fabricantes | ISSI | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de IS25C16 (archivo pdf) en la parte inferior de esta página. Total 14 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

IS25C08

IS25C16

8K-BIT/16K-BIT SPI SERIAL

ELECTRICALLY ERASABLE PROM

ISSI®

Preliminary Information

APRIL 2006

FEATURES

• Serial Peripheral Interface (SPI) Compatible

— Supports SPI Modes 0 (0,0) and 3 (1,1)

• Wide-voltage Operation

— Vcc = 1.8V to 5.5V

• Low power CMOS

— Active current less than 3.0 mA (2.5V)

— Standby current less than 2.0 µA (2.5V)

• Block Write Protection

— Protect 1/4, 1/2, or Entire Array

• 16 byte page write mode

— Partial page writes allowed

• 10 MHz Clock Rate (5V)

• Self timed write cycles (5 ms Typical)

• High-reliability

— Endurance: 1 million cycles per byte

— Data retention: 100 years

• Industrial and Automotive temperature ranges

• 8-pin PDIP, 8-pin SOIC, 8-pin TSSOP, and chip scale

packages are available

• Lead-free available

DESCRIPTION

The IS25C08 and IS25C16 are electrically erasable

PROM devices that use the Serial Peripheral Interface

(SPI) for communications. The IS25C08 is 8Kbit

(1024x 8) and the IS25C16 is 16Kbit (2048 x 8). The

IS25C08/16 EEPROMs are offered in a wide operating

voltage range of 1.8V to 5.5V compatible with most

application voltages. ISSI designed the IS25C08/16 to

be an efficient SPI EEPROM solution. The devices are

packaged in 8-pin PDIP, 8-pin SOIC, 8-pin TSSOP, and

8-ball CSP.

The functional features of the IS25C08/16 allow them to

be among the most advanced serial non-volatile memo-

ries available. Each device has a Chip-Select (CS) pin,

and a 3-wire interface of Serial Data In (SI), Serial Data

Out (SO), and Serial Clock (SCK). While the 3-wire

interface of the IS25C08/16 provides for high-speed

access, a HOLD pin allows the memories to ignore the

interface in a suspended state; later the HOLD pin re-

activates communication without re-initializing the serial

sequence. A Status Register facilitates a flexible write

protection mechanism, and a device-ready bit (RDY).

Copyright © 2006 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time

without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to

obtain the latest version of this device specification before relying on any published information and before placing orders for products.

Integrated Silicon Solution, Inc. — 1-800-379-4774

Preliminary Information Rev. 00H

02/23/06

1

1 page

IS25C08

IS25C16

ISSI ®

DEVICE OPERATION

The operations of the IS25C08/16 are controlled by a set of instructions that are clocked-in serially SI pin. (See Table

3). To begin an instruction, the chip select (CS) should be dropped Low. Subsequently, each Low-to-High transition of

the clock (SK) will latch a stable value on the SI pin. After the 8-bit op-code, it may be appropriate to continue to input

an address or data to SI, or to output data from SO. During data output, values appear on the falling edge of SK. All

bits are transferred with MSB first. Upon the last bit of communication, but prior to any following Low-to-High transition

of SK, CS should be raised High to end the transaction. The device then would enter Standby Mode if no internal

programming were underway.

Table 3. Instruction Set

Name Op-code

Operation

WREN 0000 X110

WRDI 0000 X100

RDSR 0000 X101

WRSR 0000 X001

READ 0000 X011

WRITE 0000 X010

Set Write Enable Latch

Reset Write Enable Latch

Read Status Register

Write Status Register

Read Data from Array

Write Data to Array

Address

-

-

-

-

A15-A0

A15-A0

Data(SI)

-

-

-

D7-D0

-

D7-D0,...

Data (SO)

-

-

D7-D0,...

-

D7-D0,...

-

1. X = Don’t care bit. For consistency, it is best to use “0”.

2. Some address bits are don’t care. See Table 5.

3. If the bits clocked-in for an op-code are invalid, SO remains high impedance, and upon CS going High there is no

affect. A valid op-code with an invalid number of bits clocked-in for address or data will cause an attempt to modify the

array or Status Register to be ignored.

WRITE ENABLE (WREN)

When Vcc is initially applied, the device powers up with

both status register and entire array in a write-disabled

state. Upon completion of Write Disable (WRDI), Write

Status Register (WRSR), or Write Data to Array

(WRITE), the device resets the WEN bit in the Status

Register to 0. Prior to any data modification, a WREN

instruction is necessary to set WEN to 1. (See Figure 2

for timing).

WRITE DISABLE (WRDI)

The device can be completely protected from modifica-

tion by resetting WEN to 0 through the WRDI instruc-

tion. (See Figure 3 for timing).

READ STATUS REGISTER (RDSR)

The Read Status instruction tells the user the status of

Write Protect Enable, the Block Protection setting (see

Table 2), the Write Enable state, and the RDY status.

RDSR is the only instruction accepted when a write

cycle is underway. It is recommended that the status of

Write Enable and RDY be checked, especially prior to

an attempted modification of data. The 8 bits of the

Status Register can be repeatedly output on SO after

the initial Op-code. (See Figure 4 for timing).

Integrated Silicon Solution, Inc. — 1-800-379-4774

Preliminary Information Rev. 00H

02/23/06

5

5 Page

IS25C08

IS25C16

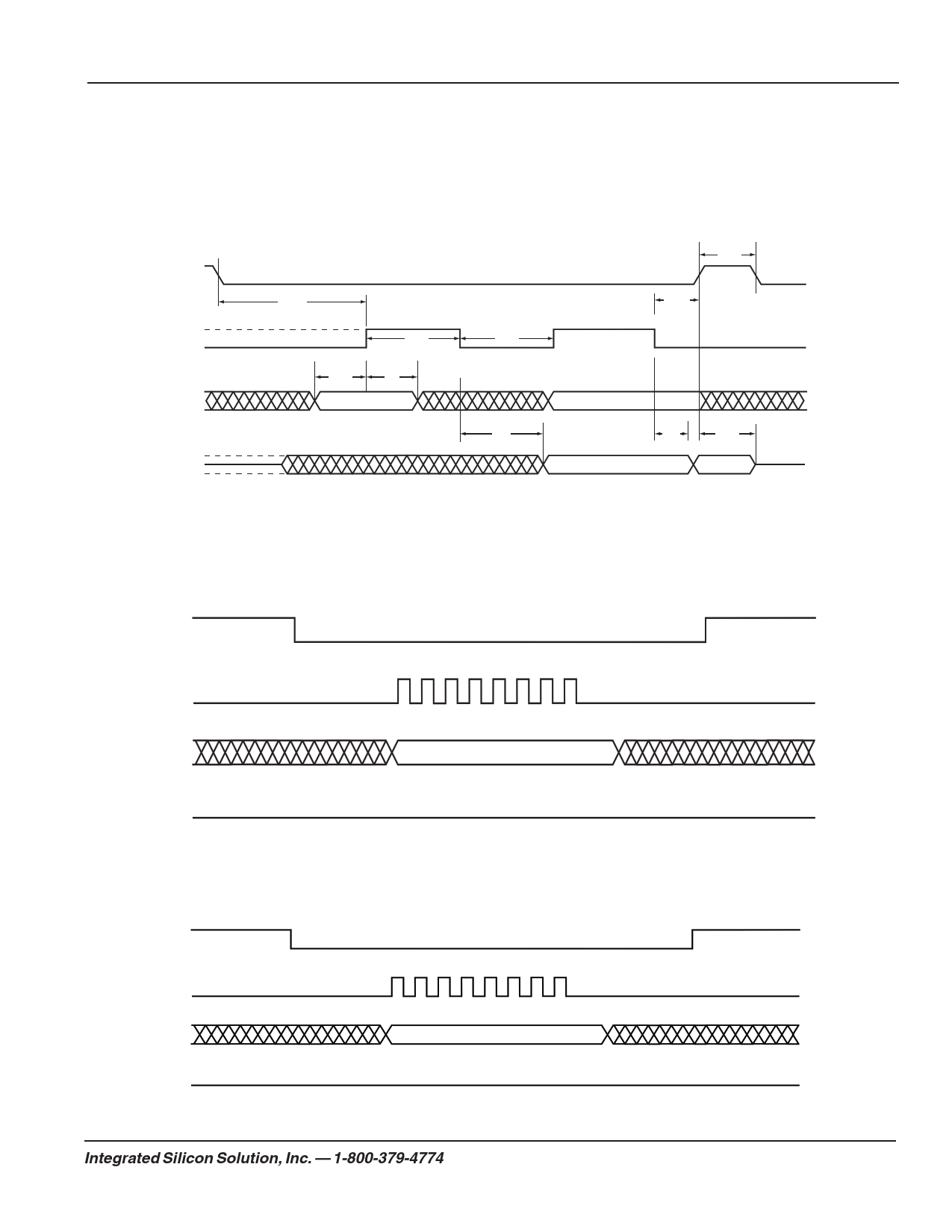

TIMING DIAGRAMS

Figure 1. Synchronous Data Timing

VIH

CS VIL

VIH

SK VIL

VIH

DIN VIL

tCSS

tWH

tSU tH

VALID IN

DOUT VOH

VOL

HIGH-Z

tWL

tV

Figure 2. WREN Timing

CS

SK

DIN

DOUT

Figure 3. WRDI Timing

CS

SK

DIN

DOUT

WREN OP-CODE

HIGH-Z

WRDI OP-CODE

HIGH-Z

Integrated Silicon Solution, Inc. — 1-800-379-4774

Preliminary Information Rev. 00H

02/23/06

ISSI ®

tCS

tCSH

tHO tDIS

HIGH-Z

11

11 Page | ||

| Páginas | Total 14 Páginas | |

| PDF Descargar | [ Datasheet IS25C16.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| IS25C128 | (IS25C128 / IS25C256) 128K-bit/ 256K-bit SPI SERIAL ELECTRICALLY ERASABLE PROM | ISSI |

| IS25C16 | (IS25C08 / IS25C16) 8K-BIT/16K-BIT SPI SERIAL ELECTRICALLY ERASABLE PROM | ISSI |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |