|

|

PDF ISPPAC-CLK56xxA Data sheet ( Hoja de datos )

| Número de pieza | ISPPAC-CLK56xxA | |

| Descripción | In-System Programmable | |

| Fabricantes | Lattice Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de ISPPAC-CLK56xxA (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

ispClock™5600A Family

In-System Programmable, Enhanced Zero-Delay

Clock Generator with Universal Fan-Out Buffer

December 2005

Preliminary Data Sheet

Features

■ Up to Five Clock Frequency Domains

■ 8MHz to 400MHz Input/Output Operation

■ Low Output to Output Skew (<50ps)

■ Flexible Clock Reference and External

Feedback Inputs

• Programmable input standards

■ Low Jitter Peak-to-Peak

■ Up to 20 Programmable Fan-out Buffers

• Programmable output standards and individual

enable controls

- LVTTL, LVCMOS, HSTL, eHSTL, SSTL,

- LVTTL, LVCMOS, SSTL, HSTL, LVDS,

LVPECL, Differential HSTL, SSTL

• Clock A/B selection multiplexer

• Feedback A/B selection multiplexer

• Programmable termination

LVDS, LVPECL, Differential HSTL, SSTL

• Programmable output impedance

■ All Inputs and Outputs are Hot Socket

Compliant

- 40 to 70Ω in 5Ω increments

• Programmable slew rate

• Up to 10 banks with individual VCCO and GND

- 1.5V, 1.8V, 2.5V, 3.3V

■ Four User-programmable Profiles Stored in

E2CMOS® Memory

• Supports both test and multiple operating

configurations

■ Fully Integrated High-Performance PLL

■ Full JTAG Boundary Scan Test In-System

• Programmable lock detect

Programming Support

• Multiply and divide ratio controlled by

- Input divider (1 to 40)

- Feedback divider (1 to 40)

- Five output dividers (2 to 80)

• Programmable on-chip loop filter

■ Exceptional Power Supply Noise Immunity

■ Commercial (0 to 70°C) and Industrial

(-40 to 85°C) Temperature Ranges

DataSheet■4U.c1o0m0-pin and 48-pin TQFP Packages

• Compatible with spread spectrum clocks

■ Precision Programmable Phase Adjustment

(Skew) Per Output

• 16 settings; minimum step size 156ps

- Locked to VCO frequency

• Up to +/- 12ns skew range

■ Applications

• Circuit board common clock generation and

distribution

• PLL-based frequency generation

• High fan-out clock buffer

• Zero-delay clock buffer

• Coarse and fine adjustment modes

Product Family Block Diagram

DataShee

LOCK DETECT

M

* PHASE/

FREQUENCY

FILTER

DETECTOR

N

PLL CORE

Internal/External

Feedback

Select

JTAG

INTERFACE

&

E2CMOS

* MEMORY

* Input Available only on ispClock5620A

BYPASS

MUX

VCO

OUTPUT

DIVIDERS

V0

V1

V2

V3

V4

Multiple Profile

Management Logic

0123

INTERNAL FEEDBACK PATH

SKEW

OUTPUT

CONTROL DRIVERS

OUTPUT

ROUTING

MATRIX

DataSheet4U© .2c0o05mLattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand

or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

www.latticesemi.com

1

clk5600a_01.0

DataSheet4 U .com

DataSheet4U.com

1 page

www.DataSheet4U.com

Lattice Semiconductor

ispClock5600A Family Data Sheet

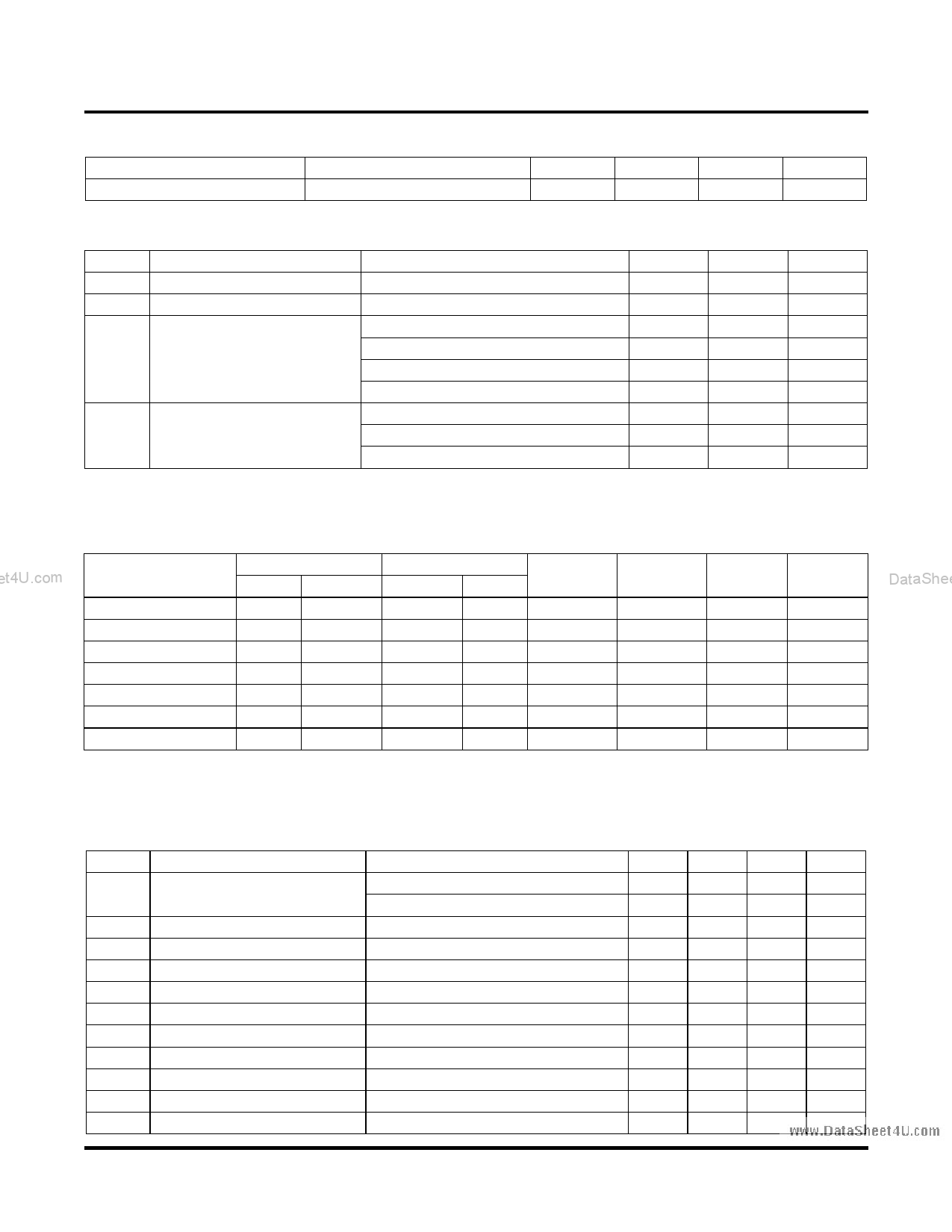

E2CMOS Memory Write/Erase Characteristics

Parameter

Erase/Reprogram Cycles

Conditions

Min.

1000

Typ.

—

Max.

—

Units

Performance Characteristics – Power Supply

Symbol

Parameter

Conditions

ICCD

Core Supply Current

ispClock5620A fVCO = 800MHz

ICCA

Analog Supply Current

fVCO = 800MHz

VCCO = 1.8V1, LVCMOS, fOUT = 266MHz

ICCO

Output Driver Supply Current

(per Bank)

VCCO = 2.5V1, LVCMOS, fOUT = 266MHz

VCCO = 3.3V1, LVCMOS, fOUT = 266MHz

VCCO = 3.3V2, LVDS, fOUT = 400MHz

VCCJ = 1.8V

ICCJ JTAG I/O Supply Current (static) VCCJ = 2.5V

VCCJ = 3.3V

1. Supply current consumed by each bank, both outputs active, 5pF load.

2. Supply current consumed by each bank, 100Ω, 5pf differential load.

Typ.

105

5.5

16

21

27

8

Max.

110

7

18

27

38

10

300

400

400

Units

mA

mA

mA

mA

mA

mA

µA

µA

µA

DC Electrical Characteristics – Single-ended Logic

et4U.com

VIL (V)

VIH (V)

Logic Standard

Min.

Max.

Min.

Max. VOL Max. (V) VOH Min. (V)

LVTTL/LVCMOS 3.3V

LVCMOS 1.8V

-0.3

-0.3

0.8

0.68

D2ataSheet34.U6 .com 0.4

1.07 3.6

0.4

VCCO - 0.4

VCCO - 0.4

LVCMOS 2.5V

-0.3 0.7

1.7 3.6

0.4 VCCO - 0.4

SSTL2 Class 1

-0.3 VREF - 0.18 VREF + 0.18 3.6

0.542

VCCO - 0.811

SSTL3 Class 1

-0.3 VREF - 0.2 VREF + 0.2 3.6

0.92 VCCO - 1.31

HSTL Class 1

-0.3 VREF - 0.1 VREF + 0.1 3.6

0.43 VCCO - 0.42

eHSTL Class 1

-0.3 VREF - 0.1 VREF + 0.1 3.6

0.43 VCCO - 0.42

1. Specified for 40Ω internal series output termination.

2. Specified for ≈20Ω internal series output termination, fast slew rate setting.

3. For slower slew rate setting IOH, IOL = 8mA.

IOL (mA)

122, 3

122, 3

122, 3

7.6

8

8

8

IOH (mA)

-122, 3

-122, 3

-122, 3

-7.6

-8

-8

-8

DC Electrical Characteristics – LVDS

Symbol

Parameter

Conditions

Min.

VICM

VTHD

VIN

VOH

VOL

VOD

ΔVOD

VOS

ΔVOS

ISA

DataSheet4UIS.cAoBm

Common Mode Input Voltage

Differential Input Threshold

VTHD ≤ 100mV

VTHD ≤ 150mV

VTHD/2

VTHD/2

±100

Input Voltage

0

Output High Voltage

Output Low Voltage

Output Voltage Differential

Change in VOD Between H and L

Output Voltage Offset

RT = 100Ω

RT = 100Ω

RT = 100Ω

Common Mode Output Voltage

—

0.9

250

—

1.10

Change in VOS Between H and L

Output Short Circuit Current

VOD = 0V, Outputs Shorted to GND

Output Short Circuit Current

VOD = 0V, Outputs Shorted to Each Other

—

—

—

Typ.

—

—

—

1.375

1.03

400

—

1.20

—

—

—

Max.

2.0

2.325

—

2.4

1.60

—

480

50

1.375

50

24

12

Units

V

V

mV

V

V

V

mV

mV

V

mV

mA

mA

DataSheet4 U .com

5

DataSheet4U.com

DataShee

5 Page

www.DataSheet4U.com

Lattice Semiconductor

ispClock5600A Family Data Sheet

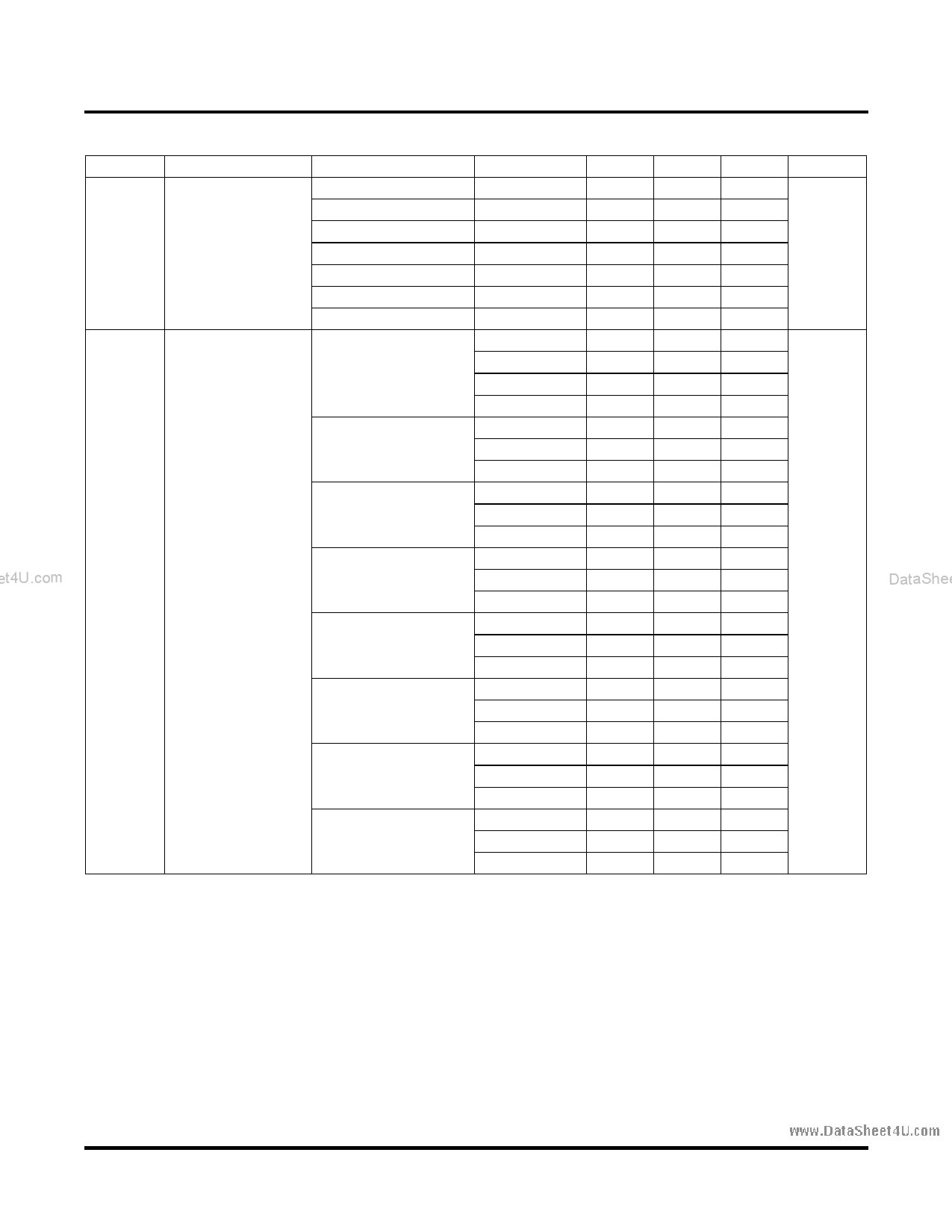

Programmable Input and Output Termination Characteristics

et4U.com

Symbol

Parameter

RIN Input Resistance

ROUT

Output Resistance1

1. Guaranteed by characterization.

Conditions

Rin=40Ω setting

VCCO Voltage

Rin=45Ω setting

Rin=50Ω setting

Rin=55Ω setting

Rin=60Ω setting

Rin=65Ω setting

Rin=70Ω setting

VCCO=3.3V

Rout≈20Ω setting

VCCO=2.5V

VCCO=1.8V

VCCO=1.5V

VCCO=3.3V

Rout≈40Ω setting

VCCO=2.5V

VCCO=1.8V

VCCO=3.3V

Rout≈45Ω setting

VCCO=2.5V

VCCO=1.8V

VCCO=3.3V

Rout≈50Ω setting

VCCO=2.5V

VCCO=1.8V

DataSheeVt4CUC.Oc=o3m.3V

Rout≈55Ω setting

VCCO=2.5V

VCCO=1.8V

VCCO=3.3V

Rout≈60Ω setting

VCCO=2.5V

VCCO=1.8V

VCCO=3.3V

Rout≈65Ω setting

VCCO=2.5V

VCCO=1.8V

VCCO=3.3V

Rout≈70Ω setting

VCCO=2.5V

VCCO=1.8V

Min.

36

40.5

45

49.5

54

59

61

—

—

—

—

-9%

-11%

-13%

-10%

-12%

-14%

-8%

-9%

-13%

-9%

-11%

-13%

-8%

-9%

-14%

-8%

-9%

-13%

-9%

-10%

-12%

Typ.

—

—

—

—

—

—

—

14

14

14

14

38

40

40

45

45

44

50

49

49

55

55

55

59

59

59

65

64

64

72

70

69

Max.

44

49.5

55

60.5

66

71.5

77

—

—

—

—

9%

11%

13%

10%

12%

14%

8%

9%

13%

9%

11%

13%

8%

9%

14%

8%

9%

13%

9%

10%

12%

Units

Ω

Ω

DataShee

DataSheet4U.com

DataSheet4 U .com

11

DataSheet4U.com

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet ISPPAC-CLK56xxA.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ISPPAC-CLK56xx | In-System Programmable | Lattice Semiconductor |

| ISPPAC-CLK56xxA | In-System Programmable | Lattice Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |