|

|

PDF HM51W16405 Data sheet ( Hoja de datos )

| Número de pieza | HM51W16405 | |

| Descripción | (HM51W16405 / HM51W17405) 16M EDO DRAM | |

| Fabricantes | Elpida Memory | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de HM51W16405 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

HM51W16405 Series

HM51W17405 Series

16 M EDO DRAM (4-Mword × 4-bit)

4 k Refresh/2 k Refresh

E0152H10 (Ver. 1.0)

(Previous ADE-203-647D (Z))

Jul. 6, 2001 (K)

Description

The HM51W16405 Series, HM51W17405 Series are CMOS dynamic RAMs organized 4,194,304-word ×

4-bit. They employ the most advanced CMOS technology for high performance and low power. The

HM51W16405 Series, HM51W17405 Series offer Extended Data Out (EDO) Page Mode as a high speed

access mode.They have package variations of standard 300-mil 26-pin plastic SOJ and 300-mil 26-pin

plastic TSOP.

Features

• Single 3.3 V (±0.3 V)

• Access time: 50 ns/60 ns/70 ns (max)

• Power dissipation

Active mode : 324 mW /288 mW /252 mW (max) (HM51W16405 Series)

: 360mW/324 mW/288 mW (max) (HM51W17405 Series)

Standby mode : 7.2 mW (max)

: 0.36 mW (max) (L-version)

• EDO page mode capability

• Long refresh period

4096 refresh cycles : 64 ms (HM51W16405 Series)

: 128 ms (L-version)

2048 refresh cycles : 32 ms (HM51W17405 Series)

: 128 ms (L-version)

• 4 variations of refresh

RAS-only refresh

CAS-before-RAS refresh

Hidden refresh

Self refresh (L-version)

Elpida Memory, Inc. is a joint venture DRAM company of NEC Corporation and Hitachi, Ltd.

1 page

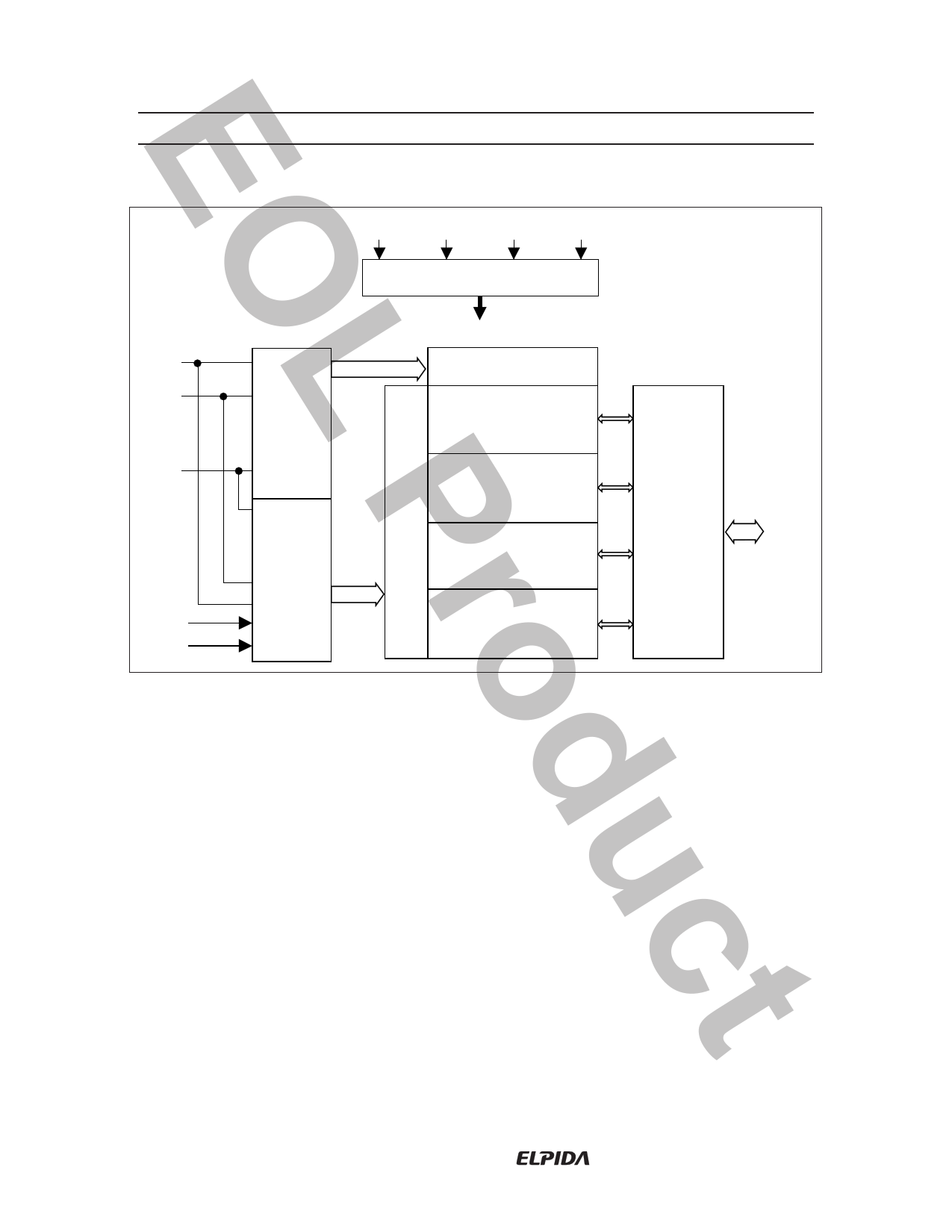

HM51W16405 Series, HM51W17405 Series

Block Diagram(HM51W16405 Series)

RAS

CAS

WE

OE

Timing and control

A0

A1 Column

to

• address

•

• buffers

A9

•

•

• Row

address

buffers

A10

A11

Column decoder

4M array

4M array

4M array

4M array

I/O buffers

I/O1

to

I/O4

Data Sheet E0152H10

5

5 Page

HM51W16405 Series, HM51W17405 Series

AC Characteristics (Ta = 0 to +70˚C, VCC = 3.3 V ± 0.3 V, VSS = 0 V) *1, *2, *18

Test Conditions

• Input rise and fall time: 2 ns

• Input levels: VIL = 0 V, VIH = 3 V

• Input timing reference levels: 0.8 V, 2.0 V

• Output timing reference levels: 0.8 V, 2.0 V

• Output load: 1 TTL gate + CL (100 pF) (Including scope and jig)

Read, Write, Read-Modify-Write and Refresh Cycles (Common parameters)

HM51W16405/HM51W17405

-5 -6 -7

Parameter

Symbol Min Max Min Max Min

Random read or write cycle time

RAS precharge time

CAS precharge time

RAS pulse width

CAS pulse width

Row address setup time

Row address hold time

Column address setup time

Column address hold time

RAS to CAS delay time

RAS to column address delay time

RAS hold time

CAS hold time

CAS to RAS precharge time

OE to Din delay time

OE delay time from Din

CAS delay time from Din

Transition time (rise and fall)

tRC

t RP

t CP

t RAS

t CAS

t ASR

t RAH

t ASC

t CAH

t RCD

t RAD

t RSH

t CSH

t CRP

t OED

t DZO

t DZC

tT

84 — 104 — 124

30 — 40 — 50

8 — 10 — 13

50 10000 60 10000 70

8 10000 10 10000 13

0—0—0

8 — 10 — 10

0—0—0

8 — 10 — 13

12 37 14 45 14

10 25 12 30 12

10 — 13 — 13

35 — 40 — 45

5—5—5

13 — 15 — 18

0—0—0

0—0—0

2 50 2 50 2

Max Unit

— ns

— ns

— ns

10000 ns

10000 ns

— ns

— ns

— ns

— ns

52 ns

35 ns

— ns

— ns

— ns

— ns

— ns

— ns

50 ns

Notes

3

4

5

6

6

7

Data Sheet E0152H10

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet HM51W16405.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HM51W16400 | (HM51W16400 / HM51W17400) Dynamic RAM | Hitachi Semiconductor |

| HM51W16400BS6 | CMOS 16M DRAM | ETC |

| HM51W16405 | (HM51W16405 / HM51W17405) 16M EDO DRAM | Elpida Memory |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |