|

|

PDF NT256D64S88A0G Data sheet ( Hoja de datos )

| Número de pieza | NT256D64S88A0G | |

| Descripción | 256MB DIMM | |

| Fabricantes | Nanya Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de NT256D64S88A0G (archivo pdf) en la parte inferior de esta página. Total 14 Páginas | ||

|

No Preview Available !

NT256D64S88A0G

256MB : 32M x 64

omPC2100 / PC1600 Unbuffered DIMM

U.c184pin One Bank Unbuffered DDR SDRAM MODULE Based on DDR266/200 32Mx8 SDRAM

eet4Features

h• 184-Pin Unbuffered 8-Byte Dual In-Line Memory Module

S• 32Mx64 Double Data Rate (DDR) SDRAM DIMM

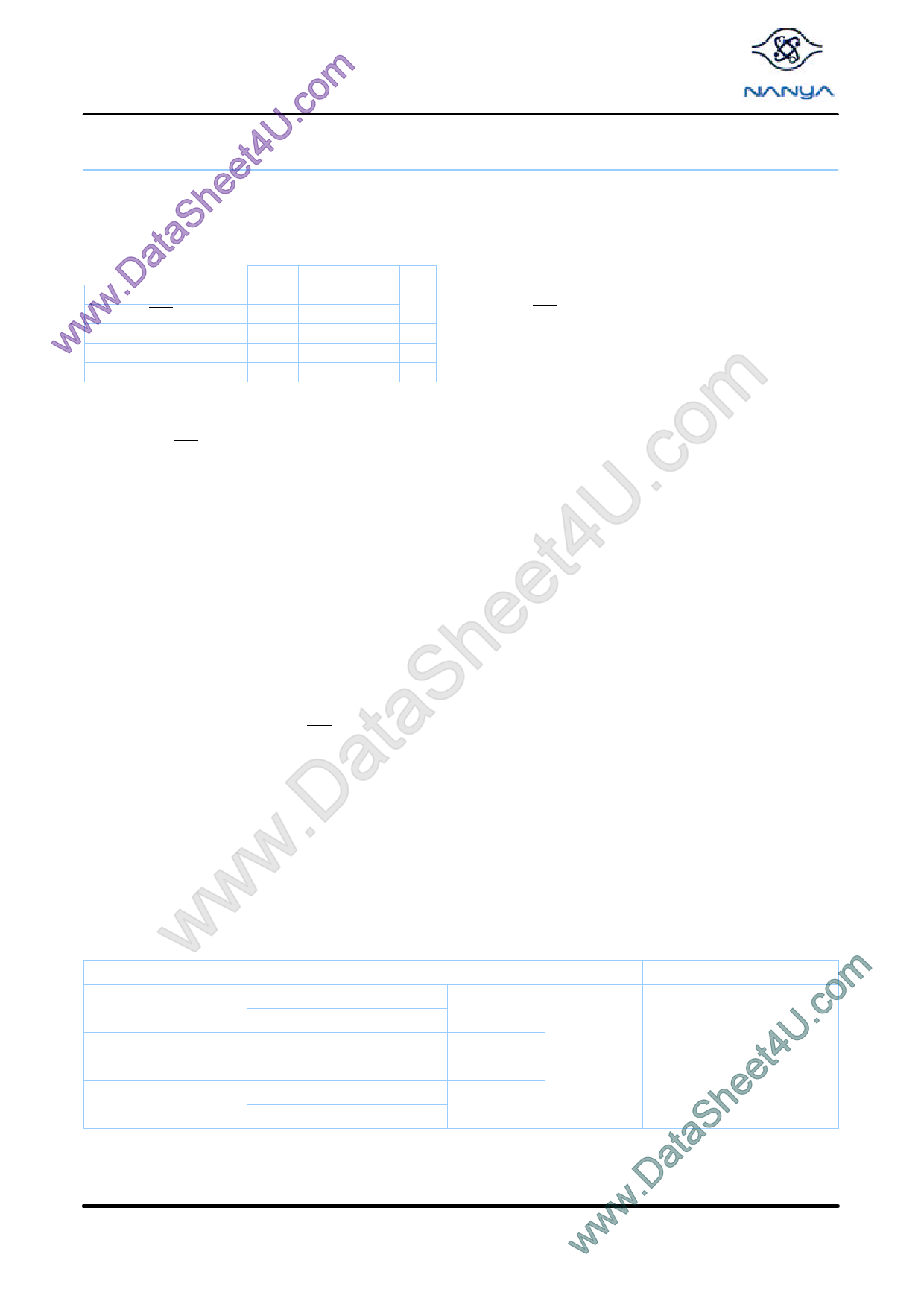

ta• Performance :

a PC1600

PC2100

.DSpeed Sort

- 8B - 75B - 7K

wDIMM CAS Latency

2 2.5 2

wf CK Clock Frequency

100 133 133

w t CK Clock Cycle

10 7.5 7.5

Unit

MHz

ns

• DRAM DLL aligns DQ and DQS transitions with clock transitions.

Also aligns QFC transitions with clock during Read cycles

• Address and control signals are fully synchronous to positive

clock edge

• Programmable Operation:

- DIMM CAS Latency: 2, 2.5

- Burst Type: Sequential or Interleave

- Burst Length: 2, 4, 8

f DQ DQ Burst Frequency 200 266 266

• Intended for 100 MHz and 133 MHz applications

• Inputs and outputs are SSTL-2 compatible

m• VDD = 2.5Volt ± 0.2, VDDQ = 2.5Volt ± 0.2

o• Single Pulsed RAS interface

• SDRAMs have 4 internal banks for concurrent operation

.c• Module has one physical bank

• Differential clock inputs

• Data is read or written on both clock edges

MHz

- Operation: Burst Read and Write

• Auto Refresh (CBR) and Self Refresh Modes

• Automatic and controlled precharge commands

• 13/10/2 Addressing (row/column/bank)

• 7.8 µs Max. Average Periodic Refresh Interval

• Serial Presence Detect

• Gold contacts

• SDRAMs in 66-pin TSOP Type II Package

t4UDescription

NT256D64S88A0G is an unbuffered 184-Pin Double Data Rate (DDR) Synchronous DRAM Dual In-Line Memory Module (DIMM),

eorganized as a one-bank high-speed memory array. The 32Mx64 module is a single-bank DIMM that uses eight 32Mx8 DDR

eSDRAMs in 400 mil TSOP packages. The DIMM achieves high-speed data transfer rates of up to 266MHz. The DIMM is intended for use

hin applications operating from 100 MHz to 133 MHz clock speeds with data rates of 200 to 266 MHz. Clock enable CKE0 controls all

Sdevices on the DIMM.

taPrior to any access operation, the device CAS latency and burst type/ length/operation type must be programmed into the DIMM by

address inputs A0-A12 and I/O inputs BA0 and BA1 using the mode register set cycle.

aThese DIMMs are manufactured using raw cards developed for broad industry use as reference designs. The use of these common

design files minimizes electrical variation between suppliers.

.DThe DIMM uses serial presence detects implemented via a serial EEPROM using the two-pin IIC protocol. The first 128 bytes of serial PD

data are programmed and locked during module assembly. The last 128 bytes are available to the customer.

wAll NANYA 184 DDR SDRAM DIMMs provide a high-performance, flexible 8-byte interface in a 5.25” long space-saving footprint.

wwOrdering Information

Part Number

NT256D64S88A0G-7K

NT256D64S88A0G –75B

NT256D64S88A0G –8B

Preliminary 08 / 2001

Speed

143MHz (7ns @ CL = 2.5 )

133MHz (7.5ns @ CL= 2 )

133MHz (7.5ns @ CL= 2.5 )

100MHz (10ns @ CL = 2 )

125MHz (8ns @ CL = 2.5 )

100MHz (10ns @ CL = 2 )

.comPC2100

t4UPC2100

heePC1600

Organization

32Mx64

Leads

Gold

Power

2.5V

w.DataS1

w © NANYA TECHNOLOGY CORP.

wNANYA TECHNOLOGY CORP. reserves the right to change Products and Specifications without notice.

1 page

NT256D64S88A0G

256MB : 32M x 64

PC2100 / PC1600 Unbuffered DIMM

Serial Presence Detect -- Part 1 of 2

32Mx64 SDRAM DIMM based on 32Mx8, 4Banks, 8K Refresh, 2.5V DDR SDRAMs with SPD

Byte

Description

SPD Entry Value

Serial PD Data Entry (Hexadecimal)

DDR266A DDR266B DDR200 DDR266A DDR266B DDR200

-7K -75B -8B -7K -75 -8B

Number of Serial PD Bytes Written during

0

Production

128

80

1 Total Number of Bytes in Serial PD device

256

08

2 Fundamental Memory Type

SDRAM DDR

07

3 Number of Row Addresses on Assembly

13

0D

4 Number of Column Addresses on Assembly

10

0A

5 Number of DIMM Bank

1 01

6. Data Width of Assembly

X64 40

7 Data Width of Assembly (cont’)

X64

00

8 Voltage Interface Level of this Assembly

SSTL 2.5V

04

9 DDR SDRAM Device Cycle Time at CL=2.5

7ns

7.5ns

8ns

70

75

80

DDR SDRAM Device Access Time from

10

0.75ns 0.75ns

0.8ns

75

75

80

Clock at CL=2.5

11 DIMM Configuration Type

Non-Parity

00

12 Refresh Rate/Type

SR/1x(7.8us)

82

13 Primary DDR SDRAM Width X8 08

14 Error Checking DDR SDRAM Device Width

N/A

00

DDR SDRAM Device Attr: Min CLk Delay,

15

Random Col Access

1 Clock

01

DDR SDRAM Device Attributes:

16

Burst Length Supported

2,4,8

0E

DDR SDRAM Device Attributes: Number of

17

Device Banks

4

04

DDR SDRAM Device Attributes: CAS

18

Latencies Supported

2/2.5

2/2.5

2/2.5

0C

0C

0C

19 DDR SDRAM Device Attributes: CS Latency

0

01

20 DDR SDRAM Device Attributes: WE Latency

1

02

21 DDR SDRAM Device Attributes:

Differential Clock

20

22 DDR SDRAM Device Attributes: General

+/-0.2V Voltage Tolerance

00

23 Minimum Clock Cycle at CL=2

7.5ns

10ns

10ns

75

A0

A0

Maximum Data Access Time from Clock at

24

0.75ns 0.75ns

0.8ns

75

75

80

CL=2

25 Minimum Clock Cycle Time at CL=1

N/A

00

Maximum Data Access Time from Clock at

26

CL=1

N/A

00

27 Minimum Row Precharge Time(tRP)

20ns

20ns

20ns

50

50

50

Minimum Row Active to Row Active delay

28

15ns

15ns

15ns

3C

3C

3C

(tRRD)

29 Minimum RAS to CAS delay (tRCD)

20ns

20ns

20ns

50

50

50

30 Minimum RAS Pulse Width (tRAS)

45ns

45ns

50ns

2D

2D

32

31 Module Bank Density

256MB

40

Address and Command Setup Time Before

32

0.9ns

0.9ns

1.1ns

90

90

B0

Clock

Address and Command Hold Time After

33

Clock

0.9ns

0.9ns

1.1ns

90

90

B0

34 Data Input Setup Time Before Clock

0.5ns

0.5ns

0.6ns

50

50

60

35 Data Input Hold Time After Clock

0.5ns

0.5ns

0.6ns

50

50

60

36-61 Reserved

Undefined

00

62 SPD Revision

Initial

Initial

Initial

00

00

00

63 Checksum Data

8F BF 45

Note

Preliminary 08 / 2001

5

© NANYA TECHNOLOGY CORP.

NANYA TECHNOLOGY CORP. reserves the right to change Products and Specifications without notice.

5 Page

NT256D64S88A0G

256MB : 32M x 64

PC2100 / PC1600 Unbuffered DIMM

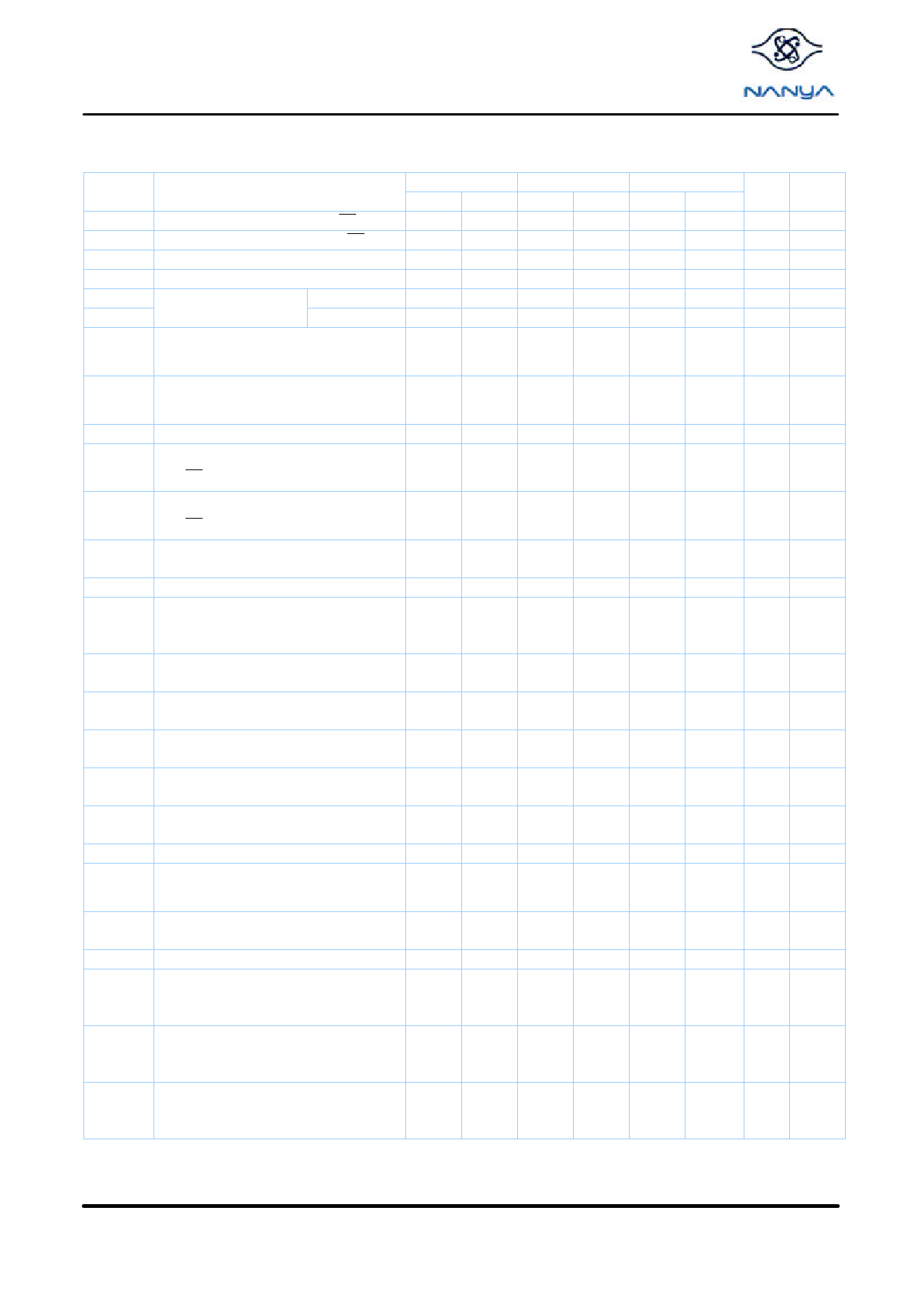

AC Timing Specifications for DDR SDRAM Devices Used on Module

( TA = 0 °C ~ 70 °C ; VDDQ = 2.5V ± 0.2V; VDD = 2.5V ± 0.2V, See AC Characteristics) (Part 1 of 2)

Symbol

Parameter

-7K

Min. Max.

-75B

Min. Max.

-8B

Min. Max.

tAC DQ output access time from CK/ CK

-0.75 +0.75 -0.75 +0.75 -0.8

+0.8

tDQSCK DQS output access time from CK/ CK

-0.75 +0.75 -0.75 +0.75 -0.8

+0.8

tCH CK high-level width

0.45 0.55 0.45 0.55 0.45 0.55

tCL CK low-level width

0.45 0.55 0.45 0.55 0.45 0.55

tCK

Clock cycle time

tCK

CL=2.5

CL=2

7 12 7.5 12 8

7.5 12 10 12 10

12

12

tDH DQ and DM input hold time

0.5 0.5 0.6

tDS DQ and DM input setup time

tDIPW

tHZ

tLZ

tDQSQ

tDQSQA

tHP

tQH

tDQSS

tDQSL,H

tDSS

tDSH

tMRD

DQ and DM input pulse width (each input)

Data-out high-impedance time from

CK/ CK

Data-out low-impedance time from

CK/ CK

DQS-DQ skew (DQS & associated DQ

signals)

DQS-DQ skew (DQS & all DQ signals)

Minimum half clk period for any given

cycle; defined by clk high(tCH )

or clk low (tCL ) time

Data output hold time from DQS

Write command to 1st DQS latching

transition

DQS input low (high) pulse width

(write cycle)

DQS falling edge to CK setup time

(write cycle)

DQS falling edge hold time from CK

(write cycle)

Mode register set command cycle time

tWPRES Write preamble setup time

0.5

1.75

-0.75

+0.75

0.5

1.75

-0.75

+0.75

0.6

2

-0.8

-0.75 +0.75 -0.75 +0.75 -0.8

tCH

or

tCL

tHP -

0.75ns

0.75

0.5

0.5

1.25

tCH

or

tCL

tHP -

0.75ns

0.75

0.5

0.5

1.25

tCH

or

tCL

tHP -

1.0ns

0.75

0.35 0.35 0.35

0.2 0.2 0.2

0.2 0.2 0.2

14 15 16

000

+0.8

+0.8

0.6

0.6

1.25

tWPST

tWPRE

tIH

Write postamble

Write preamble

Address and control input hold time

(fast slew rate)

Address and control input setup time

tIS

(fast slew rate)

Address and control input hold time

tIH

(slow slew rate)

0.40 0.60 0.40 0.60 0.40 0.60

0.25 0.25 0.25

0.9 1.1 1.1

0.9 1.1 1.1

1.0 1.1 1.1

Unit Notes

ns 1,2,3,4

ns 1,2,3,4

tCK 1,2,3,4

tCK 1,2,3,4

ns 1,2,3,4

ns 1,2,3,4

1,2,3,4

ns

,15,16

1,2,3,4

ns

,15,16

ns 1,2,3,4

1, 2, 3,

ns

4, 5

1, 2, 3,

ns

4, 5

ns 1,2,3,4

ns 1,2,3,4

tCK 1,2,3,4

tCK 1,2,3,4

tCK 1,2,3,4

tCK 1,2,3,4

tCK 1,2,3,4

tCK 1,2,3,4

ns 1,2,3,4

1, 2, 3,

ns

4, 7

1, 2, 3,

tCK

4, 6

tCK 1,2,3,4

2, 3, 4,

ns 9, 11,

12

2, 3, 4,

ns 9, 11,

12

2, 3, 4,

ns 10, 11,

12, 14

Preliminary 08 / 2001

11

© NANYA TECHNOLOGY CORP.

NANYA TECHNOLOGY CORP. reserves the right to change Products and Specifications without notice.

11 Page | ||

| Páginas | Total 14 Páginas | |

| PDF Descargar | [ Datasheet NT256D64S88A0G.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| NT256D64S88A0G | 256MB DIMM | Nanya Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |