|

|

PDF AT572D740 Data sheet ( Hoja de datos )

| Número de pieza | AT572D740 | |

| Descripción | DIOPSIS 740 Dual Core DSP | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AT572D740 (archivo pdf) en la parte inferior de esta página. Total 22 Páginas | ||

|

No Preview Available !

Features

• Dual Core System Integrating an ARM7TDMI ARM Thumb Processor Core and a

mAgic DSP for Audio, Communication and Beam-forming Applications

• High Performance DSP Operating at 100 MHz

– 1 GFLOPS - 1.5 Gops

– 10 Arithmetic Operations per Cycle (4 Multiply, 2 Add/subtract, 1 Add, 1 Subtract

Floating and Fixed Point) Allowing Single Cycle FFT Butterfly

– Native Support for Complex Arithmetic and Vectorial SIMD Operations: One

Complex Multiply with Dual Add/sub per Clock Cycle or Two Real Multiply and Two

Add/sub or Simple Scalar Operations

– 32-bit Integer and IEEE 40-bit Extended Precision Floating Point Numeric Format

– Large Multi-port Data Register File: 512 Registers Organized in Two 4-input 4-

output 256-register Banks

– Orthogonal VLIW Architecture, Code Compression for Code Size Reduction

– Flexible Addressing Capability: 2 Independent Address Generation Units

Operating on a 16 Registers Address Register File Supporting Programmable

Stride, Circular Pointers and Bit Reversal

– 1.7 Mbits of On-chip SRAM:

17 K x 40-bit Data Memory Locations

8 K x 128-bit Program Memory Location, Equivalent to 24K Instructions

– DMA Access to the External Program and Data Memory

– Two Main Operating Modes: Run and System Mode

– Efficient Optimizing Assembler: Allows Easy Exploitation of the Available

Hardware Resources Parallelism

• Utilizes the ARM7TDMI Processor Core with 32 K Byte of Integrated SRAM,

Operating at 50 MHz

– Fully-programmable External Bus Interface (EBI)

Maximum External Address Space of 4 M Bytes

Up to 4 Chip Selects

Software-programmable 8/16-bit External Data Bus

– 8-channel Peripheral Data Controller (PDC)

– 8-level Priority, Individually Maskable Vectored Interrupt Controller

4 External, 20 Internal Interrupt Sources, Including a High-priority, Low-latency

Interrupt Request

– 28 Programmable I/O Lines

– 8-channel 11-bit Programmable Clock Prescaler Feeding the Timer, Watchdog,

USARTs, SPIs

– 3-channel 16-bit Timer/Counter

5 Internal Clock Sources and 3 Configurable Sources (External Source or

Cascaded Timer Configuration)

2 Multi-purpose Output Pins plus 1 Output Dedicated to the ADDA Interface plus

3 Outputs Dedicated to the mAgic DSP

– 2 USARTs

2 Dedicated Peripheral Data Controller (PDC) Channels per USART

1 USART Supporting Full Modem Interface

– 2 Master/Slave SPI Interfaces

2 Dedicated Peripheral Data Controller (PDC) Channels per SPI

8- to 16-bit Programmable Data Length

4 External Slave Chip Selects for each SPI

– Programmable Watchdog Timer

– ADDA (A/D and D/A Converters) Interface Supporting up to 4 Analog to Digital and

4 Digital to Analog, Stereo 24-bit Converters

– IEEE 1149.1 JTAG Boundary Scan on all Active Pins

• Efficient ARM - DSP Interface Based on 1K x 40-bit Dual Ported Shared Memory,

Memory Mapped Register Access, and Interrupt Lines

• 1.8 V Core Operating Voltage, 3.3 V I/O Operating Voltage

• On-chip PLL for 100 Mhz Operation from 25 Mhz Reference Clock

• 352-ball PBGA Package

DIOPSIS 740

Dual Core DSP

AT572D740

Summary

7001AS–DSP–03/04

Note: This is a summary document. A complete document

is not available at this time. For more information, please

contact your local Atmel sales office.

1 page

AT572D740

Table 3. D740 Ball Assignment (VDDI = 1.8V)

B18 B12 B6

T1

E23

W3

AD6

AF11

AF19

AF23

W26

Table 4. D740 Ball Assignment (VDDPLL = 1.8V)

P25 R26

Table 5. D740 Ball Assignment (GND)

A1

C3

D23

W23

AD3

AF25

A2

C24 AC4

H4

AF26

A26

D4

AC8 J23

AE1 B2

D9

AC13

AE2

B25

AE25

AC18

P23

D14

B26

AF1

D19 V4

All balls not comprised in Tables 1 to 5 are “not connected”.

AD24

N4

AC23

Pin name conventions

Pin names are built using the following structure:

(functional block name) _ (activity level) (line name) (bus index)

where:

– functional block name = name of the functional block to which the pin

belongs

– activity level = “n” for low active lines; blank for high active lines

– line name = name of the function of the pin line

– bus index = number (in [ ]) corresponding to the index when the pin line is an

element of a bus

7001AS–DPS–03/04

5

5 Page

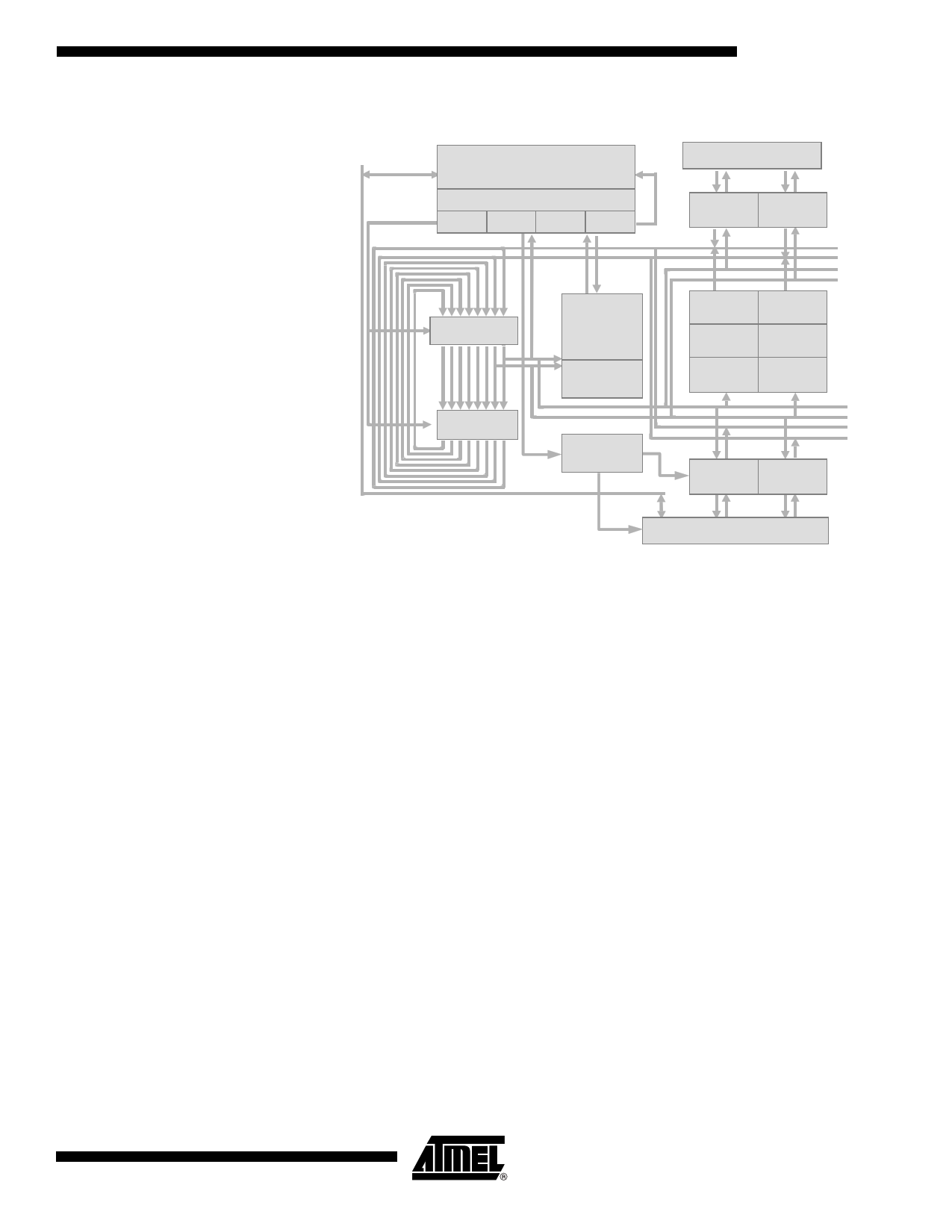

Figure 2. mAgic DSP Block Diagram

AT572D740

VLIW Program Memory

Local Controller and VLIW Decoder

Instruction

Decoder

Condition

Generation

Status

Register

Program

Counter

mAgic – ARM I/F

PARM

PARM

Memory

Memory

Left 512x40 Right 512x40

7001AS–DPS–03/04

Data Register

File

Operator

Block

Multiple

Address

Generation

Unit

Address

Register File

DMA

Controller

Data

Memory

Left 6Kx40

Data

Memory

Right 6Kx40

Buffer Data Buffer Data

Memory Left Memory

2Kx40

Right 2Kx40

External Memory I/F

The operators block, the register file, the address generation unit and the program-

sequencing unit compose the core processor. The Operators Block contains the hard-

ware that performs arithmetical operations. It works on 32-bit integers and IEEE 754

extended precision 40-bit floating-point data.

The Operators Block is composed of four integer/floating point multipliers, an adder, a

subtractor and two add-subtract integer/floating point units; moreover, it has two

shift/logic units, a Min/Max operator and two seed generators for efficient division and

inverse square root computation. The operators block is arranged in order to natively

support complex arithmetic (single cycle complex multiply or multiply and add), fast FFT

(single cycle butterfly computation) and vectorial computations. The peak performance

of mAgic is achieved during single cycle FFT butterfly execution, when mAgic delivers

10 floating-point operations per clock cycle.

mAgic is equipped with two independent address generation units. It is able to generate

up to two pairs of addresses, one to access the left and the right memory for reading

and one to access the left and the right memory for writing. It is also used in the loop

control to test if the end of a loop is reached. The Multiple Address Generation Unit

(MAGU) supports linear addressing with stride, circular addressing and bit reversed

addressing. The address generation unit has 16 registers.

The Program Address Generation Unit is devoted to control the correct Program

Counter generation according to the program flow. It generates addresses for linear

code execution as well as for non-sequential program flow. The Condition Generation

Unit combines the flags generated by the operators to produce complex conditions flags

used to control the program execution. Predicated instruction execution is supported for

different groups of instructions: arithmetical instructions, memory write, immediate load,

or all of them. The Program Address Generation Unit also allows to perform conditioned

and unconditioned branch instructions, loops, call to subroutines and return from sub-

routines.

11

11 Page | ||

| Páginas | Total 22 Páginas | |

| PDF Descargar | [ Datasheet AT572D740.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AT572D740 | DIOPSIS 740 Dual Core DSP | ATMEL Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |