|

|

PDF UDA1340 Data sheet ( Hoja de datos )

| Número de pieza | UDA1340 | |

| Descripción | Low-voltage low-power stereo audio CODEC with DSP features | |

| Fabricantes | Philips | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de UDA1340 (archivo pdf) en la parte inferior de esta página. Total 24 Páginas | ||

|

No Preview Available !

INTEGRATED CIRCUITS

DATA SHEET

UDA1340

Low-voltage low-power stereo

audio CODEC with DSP features

Preliminary specification

Supersedes data of 1997 May 20

File under Integrated Circuits, IC01

1997 Jul 09

1 page

Philips Semiconductors

Low-voltage low-power stereo audio

CODEC with DSP features

Preliminary specification

UDA1340

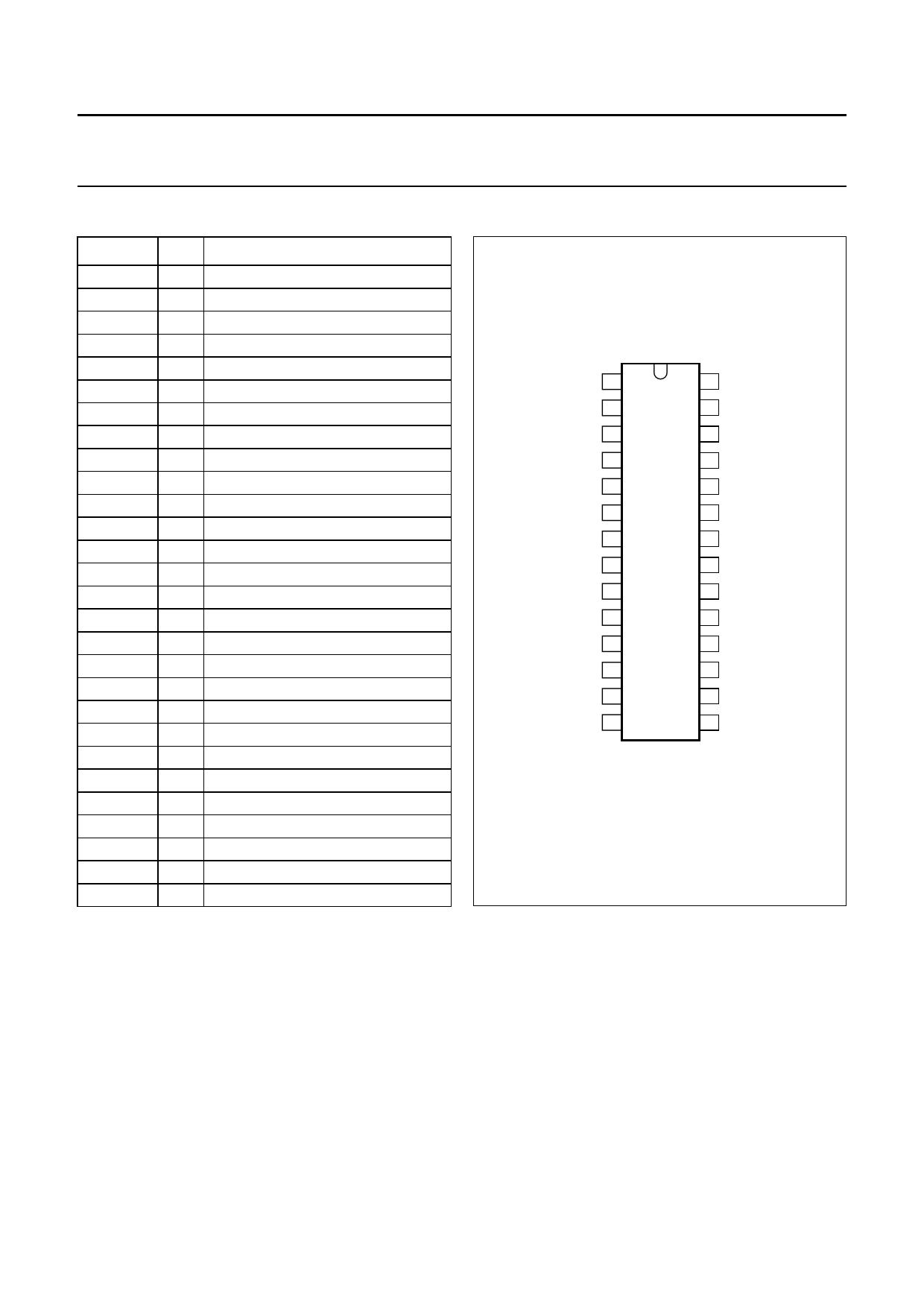

PINNING

SYMBOL PIN

Description

VSSA(ADC)

VDDA(ADC)

VINL

1 ADC analog ground

2 ADC analog supply voltage

3 ADC input left

Vref(A)

VINR

4 ADC reference voltage

5 ADC input right

VADCN

6 ADC negative reference voltage

VADCP

TEST1

7 ADC positive reference voltage

8 test control 1 (pull-down)

OVERFL 9 overload flag output

VDDD

VSSD

SYSCLK

10 digital supply voltage

11 digital ground

12 system clock 256, 384 or 512fs

L3MODE 13 L3-bus mode input

L3CLOCK 14 L3-bus clock input

L3DATA 15 L3-bus data input

BCK

16 bit clock input

WS 17 word selection input

DATAO

18 data output

DATAI

19 data input

TEST3

20 test output

TEST2

21 test control 2 (pull-down)

VSSA(DAC)

VDDA(DAC)

VOUTR

22 DAC analog ground

23 DAC analog supply voltage

24 DAC output right

VDDO

VOUTL

25 operational amplifier supply voltage

26 DAC output left

VSSO

27 operational amplifier ground

Vref(D)

28 DAC reference voltage

handbook, halfpage

VSSA(ADC) 1

VDDA(ADC) 2

VINL 3

28 Vref(D)

27 VSSO

26 VOUTL

Vref(A) 4

VINR 5

25 VDDO

24 VOUTR

VADCN 6

VADCP 7

TEST1 8

23 VDDA(DAC)

22 VSSA(DAC)

UDA1340

21 TEST2

OVERFL 9

20 TEST3

VDDD 10

VSSD 11

SYSCLK 12

19 DATAI

18 DATAO

17 WS

L3MODE 13

16 BCK

L3CLOCK 14

15 L3DATA

MGG838

Fig.2 Pin configuration.

1997 Jul 09

5

5 Page

Philips Semiconductors

Low-voltage low-power stereo audio

CODEC with DSP features

Preliminary specification

UDA1340

handbook, full pagewidth

L3MODE

thalt

L3CLOCK

L3DATA

address

data byte #1

data byte #2

address

MGD018

Fig.6 Multibyte transfer.

Table 5 Data transfer of type ‘status’; note 1

BIT 7

0

1

BIT 6

X

X

BIT 5

SC1

X

BIT 4

SC0

X

BIT 3

IF2

X

BIT 2

IF1

X

BIT 1

IF0

X

BIT 0

REGISTER SELECTED

DC System Clock frequency (1 : 0)

data Input Format (2 : 0)

DC-filter

X not used

Note

1. X = don’t care.

Table 6 Data transfer of type ‘data’; note 1

BIT 7

0

0

1

1

BIT 6

0

1

0

1

BIT 5

VC5

BB3

X

X

BIT 4

VC4

BB2

DE1

X

BIT 3

VC3

BB1

DE0

X

BIT 2

VC2

BB0

MT

X

BIT 1

VC1

TR1

M1

PC1

BIT 0

REGISTER SELECTED

VC0 Volume Control (5 : 0)

TR0 Bass Boost (3 : 0)

Treble (1 : 0)

M0 DE-emphasis (1 : 0)

MuTe

Mode (1 : 0)

PC0 Power Control (1 : 0)

Note

1. X = don’t care.

1997 Jul 09

11

11 Page | ||

| Páginas | Total 24 Páginas | |

| PDF Descargar | [ Datasheet UDA1340.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| UDA1340 | Low-voltage low-power stereo audio CODEC with DSP features | Philips |

| UDA1341TS | Economy audio CODEC | NXP Semiconductors |

| UDA1342TS | Audio CODEC | Philips |

| UDA1343TT | Economy audio CODEC | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |