|

|

PDF 74FR1074PC Data sheet ( Hoja de datos )

| Número de pieza | 74FR1074PC | |

| Descripción | Dual D-Type Flip-Flop | |

| Fabricantes | Fairchild | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de 74FR1074PC (archivo pdf) en la parte inferior de esta página. Total 8 Páginas | ||

|

No Preview Available !

March 1992

Revised August 1999

74FR74 • 74FR1074

Dual D-Type Flip-Flop

General Description

The 74FR74 and 74FR1074 are dual D-type flip-flops with

true and complement (Q/Q) outputs. On the 74FR74, data

at the D inputs is transferred to the outputs on the rising

edge of the clock input (CPn). The 74FR1074 is the nega-

tive edge triggered version of this device. Both parts fea-

ture asynchronous clear (CDn) and set (SDn) inputs which

are low level enabled.

Features

s 74FR74 is pin-for-pin compatible with the 74F74

s True 150 MHz fMAX capability on 74FR74

s Outputs sink 24 mA and source 24 mA

s Guaranteed pin-to-pin skew specifications

Ordering Code:

Order Number Package Number

Package Description

74FR74SC

M14A

14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150 Narrow

74FR74PC

N14A

14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

74FR1074SC

M14A

14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150 Narrow

74FR1074PC

N14A

14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

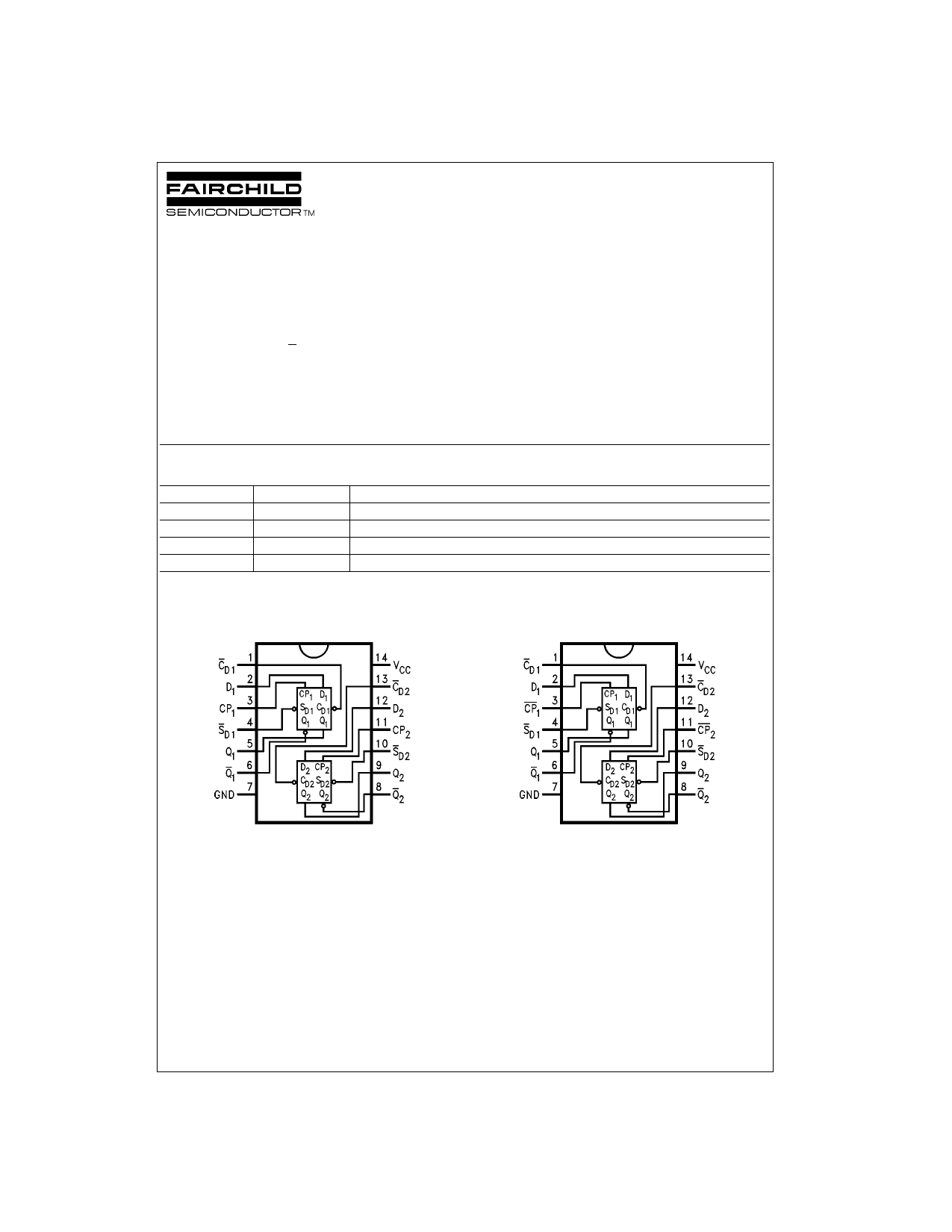

Connection Diagrams

74FR74

74FR1074

© 1999 Fairchild Semiconductor Corporation DS010977

www.fairchildsemi.com

1 page

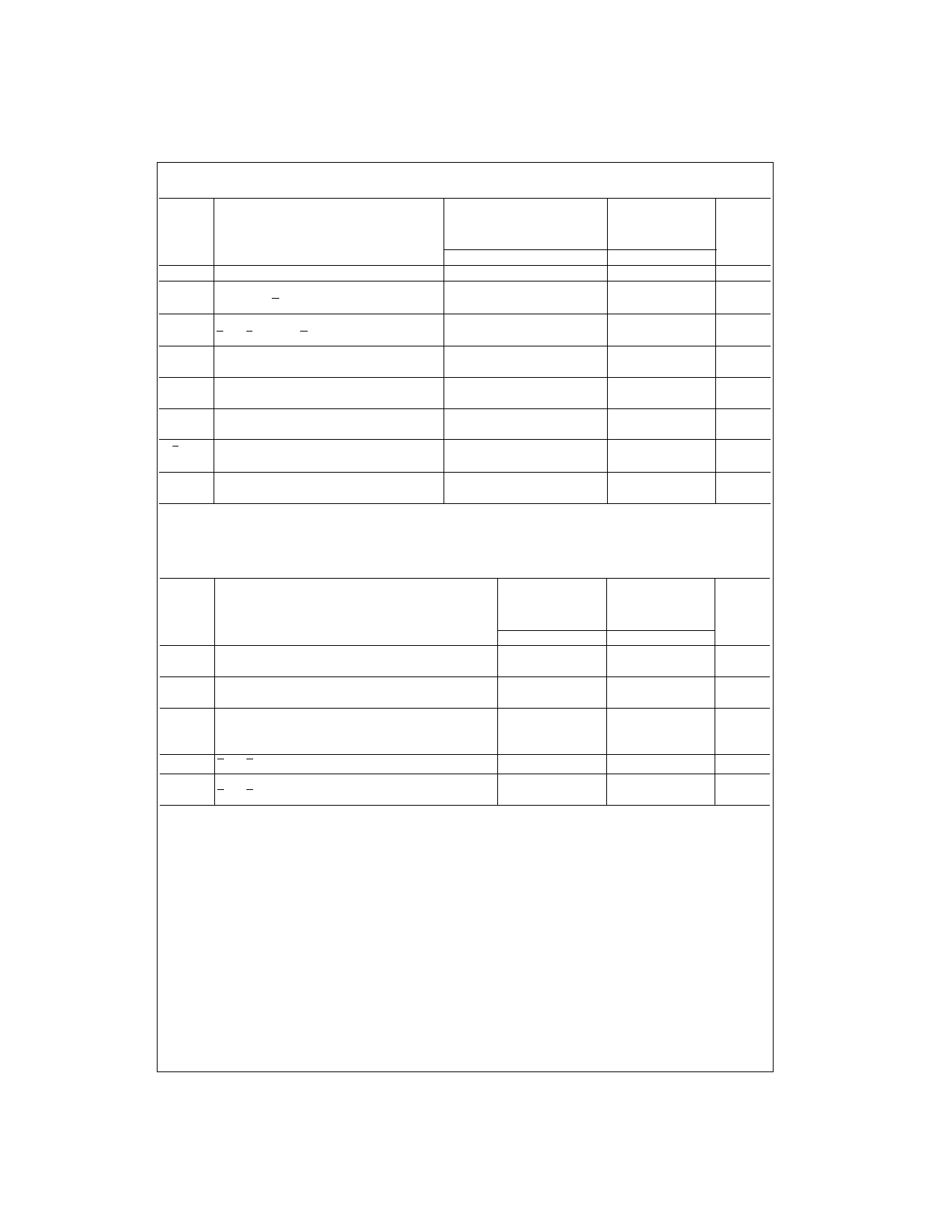

AC Electrical Characteristics 74FR74

Symbol

Parameter

TA = +25°C

VCC = +5.0V

CL = 50 pF

Min Typ Max

TA = 0°C to +70°C

VCC = +5.0V

CL = 50 pF

Min Max

Units

fMAX

tPLH

tPHL

tPLH

tPHL

tOSHL

(Note 3)

Maximum Clock Frequency

Propagation Delay

CPn to Qn or Qn

Propagation Delay

CDn or SDn to Qn or Qn

Pin to Pin Skew

for HL Transitions

150 190 150 MHz

2.5 3.5 5.0 2.5 5.0

ns

2.5 4.5 6.0 2.5 6.0

1.5 3.5 5.5 1.5 5.5

ns

2.0 5.5 7.0 2.0 7.0

1.0 ns

tOSLH

(Note 3)

Pin to Pin Skew

for LH Transitions

1.0 ns

tOST

(Note 3)

Pin to Pin Skew

for HL/LH Transitions

3.0 ns

tQ/Q

(Note 3)

True/Complement

Output Skew

1.8 ns

tPS

(Note 3)

Pin (Signal)

Transition Variation

1.8 ns

Note 3: Pin-to-Pin Skew is defined as the absolute value of the difference between the actual propagation delay for any outputs within the same packaged

device. The specifications apply to any outputs switching in the same direction either HIGH-to-LOW (tOSHL) or LOW-to-HIGH (tOSLH) or in opposite directions

both HL and LH (tOST). tOST is guaranteed by design.

AC Operating Requirements 74FR74

Symbol

Parameter

tS(H)

tS(L)

tH(H)

tH(L)

tW(H)

tW(L)

(Note 4)

Setup Time, HIGH or LOW

Dn to CPn

Hold Time, HIGH or LOW

Dn to CPn

CPn Pulse Width

HIGH or LOW

tW(L)

SDn or CDn Pulse Width

tREC

Recovery Time

SDn or CDn to CPn

Note 4: This specification is guaranteed by design.

TA = +25°C

VCC = +5.0V

CL = 50 pF

Min Max

2.5

2.5

0

0

3.3

3.3

4.0

2.0

TA = 0°C to +70°C

VCC = +5.0V

CL = 50 pF

Min Max

2.5

2.5

0

0

3.3

3.3

4.0

2.0

Units

ns

ns

ns

ns

ns

5 www.fairchildsemi.com

5 Page | ||

| Páginas | Total 8 Páginas | |

| PDF Descargar | [ Datasheet 74FR1074PC.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 74FR1074PC | Dual D-Type Flip-Flop | Fairchild |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |