|

|

PDF 82C54 Data sheet ( Hoja de datos )

| Número de pieza | 82C54 | |

| Descripción | CMOS Programmable Interval Timer | |

| Fabricantes | Intersil Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de 82C54 (archivo pdf) en la parte inferior de esta página. Total 23 Páginas | ||

|

No Preview Available !

Data Sheet

September 15, 2015

82C54

FN2970.6

CMOS Programmable Interval Timer

The Intersil 82C54 is a high performance CMOS

Programmable Interval Timer manufactured using an

advanced 2 micron CMOS process.

The 82C54 has three independently programmable and

functional 16-bit counters, each capable of handling clock

input frequencies of up to 8MHz (82C54) or 10MHz

(82C54-10) or 12MHz (82C54-12).

The high speed and industry standard configuration of the

82C54 make it compatible with the Intersil 80C86, 80C88,

and 80C286 CMOS microprocessors along with many

other industry standard processors. Six programmable

timer modes allow the 82C54 to be used as an event

counter, elapsed time indicator, programmable one-shot,

and many other applications. Static CMOS circuit design

insures low power operation.

The Intersil advanced CMOS process results in a significant

reduction in power with performance equal to or greater than

existing equivalent products.

Pinouts

82C54 (PDIP, CERDIP)

TOP VIEW

D7 1

D6 2

D5 3

D4 4

D3 5

D2 6

D1 7

D0 8

CLK 0 9

OUT 0 10

GATE 0 11

GND 12

24 VCC

23 WR

22 RD

21 CS

20 A1

19 A0

18 CLK 2

17 OUT 2

16 GATE 2

15 CLK 1

14 GATE 1

13 OUT 1

Features

• 8MHz to 12MHz Clock Input Frequency

• Compatible with NMOS 8254

- Enhanced Version of NMOS 8253

• Three Independent 16-Bit Counters

• Six Programmable Counter Modes

• Status Read Back Command

• Binary or BCD Counting

• Fully TTL Compatible

• Single 5V Power Supply

• Low Power

- ICCSB. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10µA

- ICCOP . . . . . . . . . . . . . . . . . . . . . . . . . . 10mA at 8MHz

• Operating Temperature Ranges

- CX82C54 . . . . . . . . . . . . . . . . . . . . . . . . . 0°C to +70°C

- IX82C54 . . . . . . . . . . . . . . . . . . . . . . . . . -40°C to +85°C

- MD82C54 . . . . . . . . . . . . . . . . . . . . . . . -55°C to +125°C

• Pb-Free Plus Anneal Available (RoHS Compliant)

82C54 (PLCC/CLCC)

TOP VIEW

4 3 2 1 28 27 26

D4 5

D3 6

D2 7

D1 8

D0 9

CLK 0 10

NC 11

25 NC

24 CS

23 A1

22 A0

21 CLK2

20 OUT 2

19 GATE 2

12 13 14 15 16 17 18

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774 | Intersil (and design) is a registered trademark of Intersil Americas LLC.

Copyright © Intersil Americas LLC 2003, 2005, 2013, 2015. All Rights Reserved.

All other trademarks mentioned are the property of their respective owners.

1 page

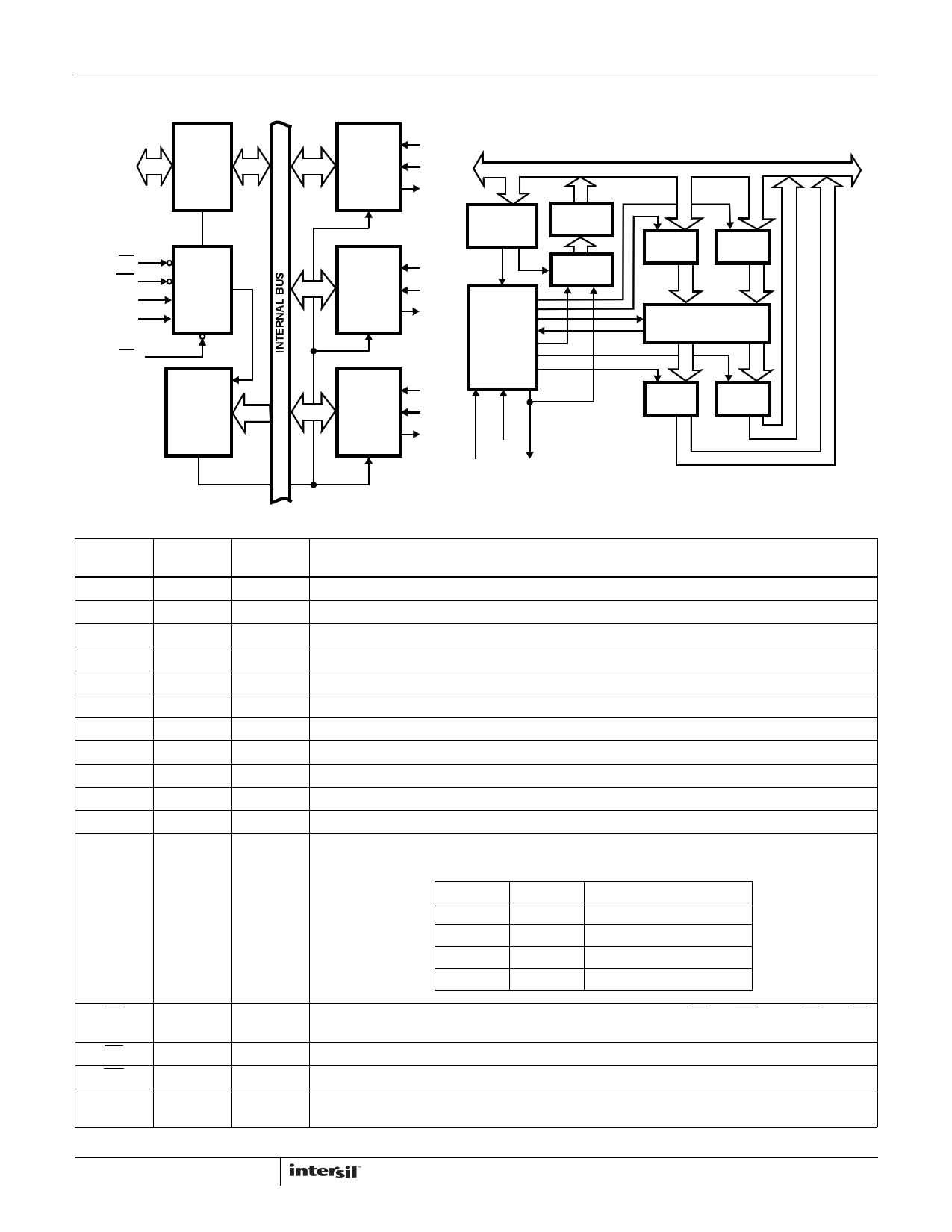

Functional Diagram

82C54

D7 - D0 8

DATA/

BUS

BUFFER

RD

WR

READ/

WRITE

A0 LOGIC

A1

CS

CONTROL

WORD

REGISTER

Pin Description

SYMBOL

DIP PIN

NUMBER

D7 - D0

1-8

CLK 0

9

OUT 0

10

GATE 0

11

GND

12

OUT 1

13

GATE 1

14

CLK 1

15

GATE 2

16

OUT 2

17

CLK 2

18

A0, A1

19 - 20

TYPE

I/O

I

O

I

O

I

I

I

O

I

I

COUNTER

0

COUNTER

1

CLK 0

GATE 0

OUT 0

CONTROL

WORD

REGISTER

CLK 1

GATE 1

OUT 1

CONTROL

LOGIC

STATUS

LATCH

STATUS

REGISTER

INTERNAL BUS

CRM

CRL

CE

COUNTER

2

CLK 2

GATE 2

OUT 2

GATE n

CLK n OUT n

OLM

OLL

COUNTER INTERNAL BLOCK DIAGRAM

DEFINITION

DATA: Bi-directional three-state data bus lines, connected to system data bus.

CLOCK 0: Clock input of Counter 0.

OUT 0: Output of Counter 0.

GATE 0: Gate input of Counter 0.

GROUND: Power supply connection.

OUT 1: Output of Counter 1.

GATE 1: Gate input of Counter 1.

CLOCK 1: Clock input of Counter 1.

GATE 2: Gate input of Counter 2.

OUT 2: Output of Counter 2.

CLOCK 2: Clock input of Counter 2.

ADDRESS: Select inputs for one of the three counters or Control Word Register for read/write

operations. Normally connected to the system address bus.

A1 A0

SELECTS

0 0 Counter 0

0 1 Counter 1

1 0 Counter 2

1 1 Control Word Register

CS

RD

WR

VCC

21

22

23

24

I CHIP SELECT: A low on this input enables the 82C54 to respond to RD and WR signals. RD and WR

are ignored otherwise.

I READ: This input is low during CPU read operations.

I WRITE: This input is low during CPU write operations.

- VCC: The +5V power supply pin. A 0.1F capacitor between pins VCC and GND is recommended for

decoupling.

5

5 Page

82C54

COMMANDS

D7 D6 D5 D4 D3 D2 D1 D0

DESCRIPTION

RESULT

1 1 0 0 0 0 1 0 Read-Back Count and Status of Counter 0 Count and Status Latched for Counter 0

1 1 1 0 0 1 0 0 Read-Back Status of Counter 1

Status Latched for Counter 1

1 1 1 0 1 1 0 0 Read-Back Status of Counters 2, 1

Status Latched for Counter 2,

But Not Counter 1

1 1 0 1 1 0 0 0 Read-Back Count of Counter 2

Count Latched for Counter 2

1 1 0 0 0 1 0 0 Read-Back Count and Status of Counter 1 Count Latched for Counter 1,

But Not Status

1 1 1 0 0 0 1 0 Read-Back Status of Counter 1

Command Ignored, Status Already

Latched for Counter 1

FIGURE 7. READ-BACK COMMAND EXAMPLE

CS RD WR A1 A0

0 1 0 0 0 Write into Counter 0

0 1 0 0 1 Write into Counter 1

0 1 0 1 0 Write into Counter 2

0 1 0 1 1 Write Control Word

0 0 1 0 0 Read from Counter 0

0 0 1 0 1 Read from Counter 1

0 0 1 1 0 Read from Counter 2

0 0 1 1 1 No-Operation (Three-State)

1 X X X X No-Operation (Three-State)

0 1 1 X X No-Operation (Three-State)

FIGURE 8. READ/WRITE OPERATIONS SUMMARY

MODE DEFINITIONS

The following are defined for use in describing the operation

of the 82C54.

CLK PULSE - A rising edge, then a falling edge, in that

order, of a Counter’s CLK input.

TRIGGER - A rising edge of a Counter’s Gate input.

COUNTER LOADING - The transfer of a count from the CR

to the CE (See “Functional Description”)

MODE 0: INTERRUPT ON TERMINAL COUNT

Mode 0 is typically used for event counting. After the Control

Word is written, OUT is initially low, and will remain low until

the Counter reaches zero. OUT then goes high and remains

high until a new count or a new Mode 0 Control Word is

written to the Counter.

GATE = 1 enables counting; GATE = 0 disables counting.

GATE has no effect on OUT.

After the Control Word and initial count are written to a

Counter, the initial count will be loaded on the next CLK

pulse. This CLK pulse does not decrement the count, so for

an initial count of N, OUT does not go high until N + 1 CLK

pulses after the initial count is written.

If a new count is written to the Counter it will be loaded on

the next CLK pulse and counting will continue from the new

count. If a two-byte count is written, the following happens:

1. Writing the first byte disables counting. Out is set low

immediately (no clock pulse required).

2. Writing the second byte allows the new count to be

loaded on the next CLK pulse.

This allows the counting sequence to be synchronized by

software. Again OUT does not go high until N + 1 CLK

pulses after the new count of N is written.

11

11 Page | ||

| Páginas | Total 23 Páginas | |

| PDF Descargar | [ Datasheet 82C54.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 82C50 | CMOS Asynchronous Communications Element | Intersil Corporation |

| 82C50 | VOLTAGE DETECTORS | Unisonic Technologies |

| 82C501 | Ethernet Serial Interface | Intel |

| 82C50A | CMOS Asynchronous Communications Element | Intersil Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |