|

|

PDF M74HC181 Data sheet ( Hoja de datos )

| Número de pieza | M74HC181 | |

| Descripción | ARITHMETIC LOGIC UNIT/FUNCTION GENERATOR | |

| Fabricantes | ST Microelectronics | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de M74HC181 (archivo pdf) en la parte inferior de esta página. Total 13 Páginas | ||

|

No Preview Available !

M74HC181

ARITHMETIC LOGIC UNIT/FUNCTION GENERATOR

. HIGH SPEED

tPD = 13 ns (TYP.) AT VCC = 5 V

. LOW POWER DISSIPATION

ICC = 4 µA (MAX.) at TA = 25 °C

. HIGH NOISE IMMUNITY

VNIH = VNIL = 28 % VCC (MIN.)

. OUTPUT DRIVE CAPABILITY

10 LSTTL LOADS

. SYMMETRICAL OUTPUT IMPEDANCE

IOH = IOL = 4 mA (MIN.)

. BALANCED PROPAGATION DELAYS

tPLH = tPHL

. WIDE OPERATING VOLTAGE RANGE

VCC (OPR) = 2 V to 6 V

. PIN AND FUNCTION COMPATIBLE

WITH 54/74LS181

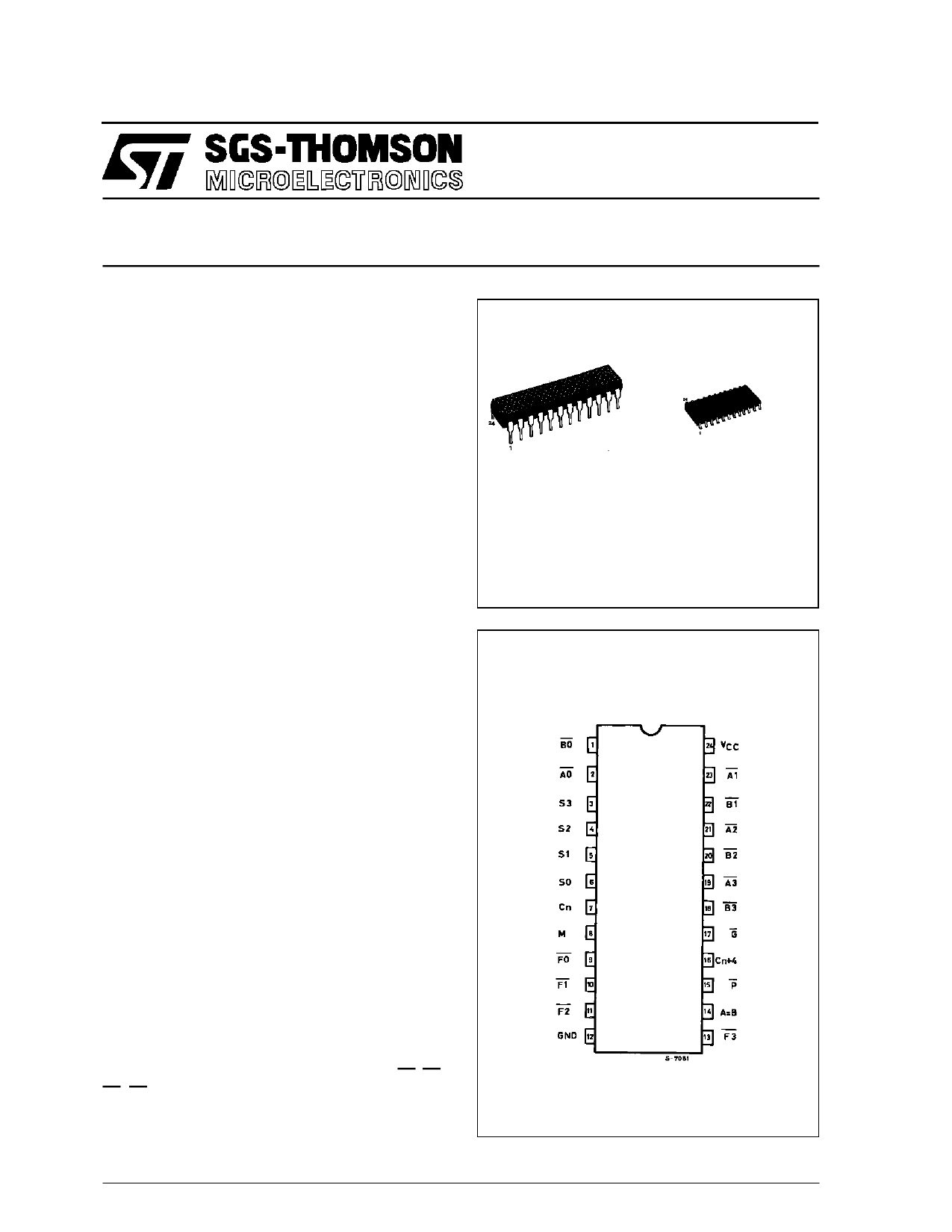

B1R

(Plastic Package)

M1R

(Micro Package)

ORDER CODES :

M 74HC 18 1M 1R

M 74 HC 181B 1R

DESCRIPTION

The 74HC181 is a high speed CMOS ARITHMETIC

LOGIC UNIT/FUNCTION GENERATOR fabricated

with silicon gate C2MOS technology. It has the same

high speed performance of LSTTL combined with true

CMOS low power consumption. These circuits per-

form 16 binary arithmetic operations on two 4-bit

words as shown in tables 1 and 2. These operations

are selected by the four function-select lines (S0, S1,

S2, S3) and include addition, subtraction, decrement,

and straight transfer. When performing arithmetic

manipulations, the internal carries must be enabled by

applying a low-level voltage to the mode control input

(M). A full carry look-ahead scheme is made available

in these devices for fast, simultaneous carry gener-

ation by means of two cascade-outputs (pins 15 and

17) for the four bits in the package. When used in con-

junction with the M54HC182 or M74HC182, full carry

look-ahead circuits, high-speed arithmetic operations

can be performed. These circuits will accomodate ac-

tive-high or active-low data, if the pin designations are

interpreted as shown below. Subtraction is accom-

plished by 1,s complement addition where the 1’s

complement of the subtrahend is generated internally.

The resultant output is 1–B–1, which requires an end-

around or forced carry to produce A–B. The 181 can

also be utilized as a comparator. The A = B output is

internally decoded from the function outputs (F0, F1,

F2, F3) so that when two words of equal magnitude

are applied at the A and B inputs, it will assume a high

level to indicated equality (A = B). The ALU should be

PIN CONNECTIONS (top view)

* Open drain Output Structure

October 1993

1/13

1 page

LOGIC DIAGRAM

M74HC181

5/13

5 Page

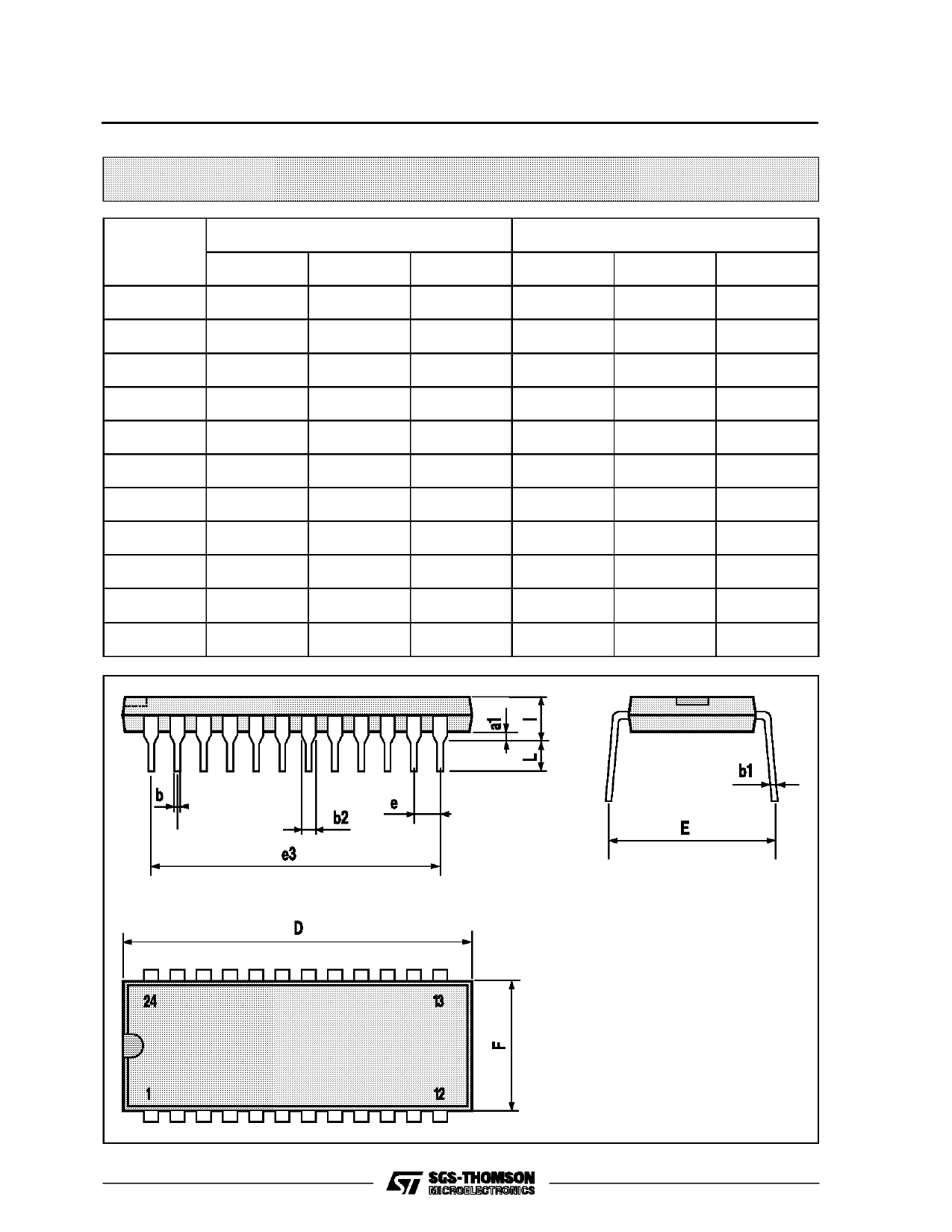

DIM.

a1

b

b1

b2

D

E

e

e3

F

I

L

M74HC181

Plastic DIP24 (0.25) MECHANICAL DATA

MIN.

0.23

15.2

mm

TYP.

0.63

0.45

1.27

2.54

27.94

4.445

3.3

MAX.

0.31

32.2

16.68

14.1

MIN.

0.009

0.598

inch

TYP.

0.025

0.018

0.050

0.100

1.100

0.175

0.130

MAX.

0.012

1.268

0.657

0.555

P043A

11/13

11 Page | ||

| Páginas | Total 13 Páginas | |

| PDF Descargar | [ Datasheet M74HC181.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| M74HC181 | ARITHMETIC LOGIC UNIT/FUNCTION GENERATOR | ST Microelectronics |

| M74HC182 | FUNCTION LOOK AHEAD CARRY GENERATOR | ST Microelectronics |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |