|

|

PDF HYS72V4120GU-10 Data sheet ( Hoja de datos )

| Número de pieza | HYS72V4120GU-10 | |

| Descripción | 3.3V 4M x 64-Bit 2 BANK SDRAM Module 3.3V 4M x 72-Bit 2 BANK SDRAM Module | |

| Fabricantes | Siemens | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de HYS72V4120GU-10 (archivo pdf) en la parte inferior de esta página. Total 11 Páginas | ||

|

No Preview Available !

3.3V 4M x 64-Bit 2 BANK SDRAM Module

3.3V 4M x 72-Bit 2 BANK SDRAM Module

168 pin unbuffered DIMM Modules

HYS64V4120GU-10

HYS72V4120GU-10

• 168 Pin JEDEC Standard, Unbuffered 8 Byte Dual-In-Line SDRAM Module

for PC main memory applications

• 2 bank 4M x 64, 4M x 72 organisation

• Optimized for byte-write non-parity or ECC applications

• Fully PC66 layout compatible

• JEDEC standard Synchronous DRAMs (SDRAM)

• Performance:

fCK Max. Clock frequency

tAC Max. access time from clock

-10

66 MHz @ CL=2

100 MHz @ CL=3

9 ns @ CL=2

8 ns @ CL=3

• Single +3.3V(± 0.3V ) power supply

• Programmable CAS Latency, Burst Length and Wrap Sequence

(Sequential & Interleave)

• Auto Refresh (CBR) and Self Refresh

• Decoupling capacitors mounted on substrate

• All inputs, outputs are LVTTL compatible

• Serial Presence Detect with E2PROM

• Utilizes 16 / 18 2M x 8 SDRAMs in TSOPII-44 packages

• 4096 refresh cycles every 64 ms

• Gold contact pad

• Card Size: 133,35 mm x 29.21 mm x 4,00 mm for HYS64(72)V4120GU

Semiconductor Group

1

2.98

1 page

HYS64(72)V4120GU-10

4M x 64/72 SDRAM-Module

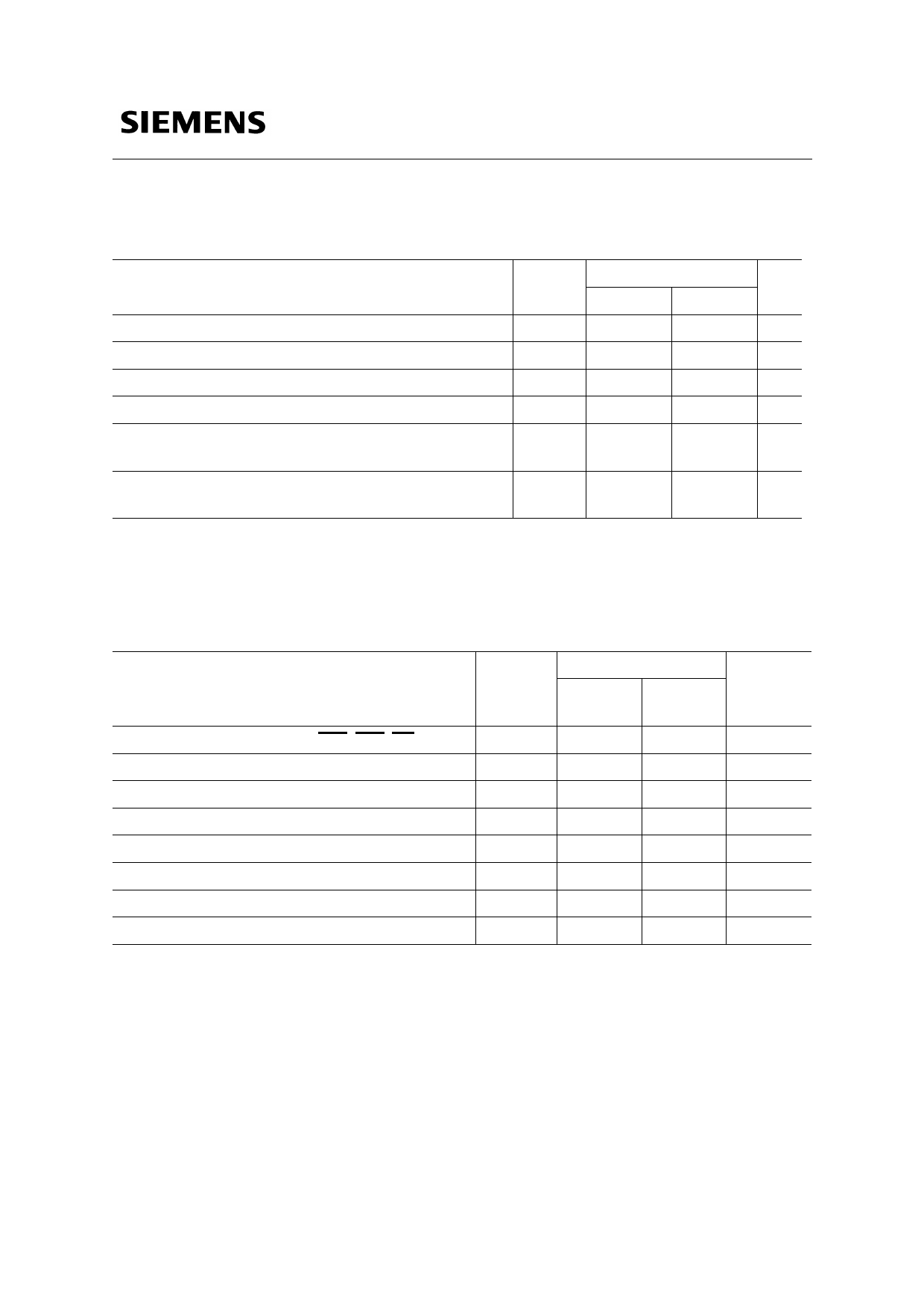

DC Characteristics

TA = 0 to 70 °C; VSS = 0 V; V VDD, DDQ = 3.3 V ± 0.3 V

Parameter

Input high voltage

Input low voltage

Output high voltage (IOUT = – 2.0 mA)

Output low voltage (IOUT = 2.0 mA)

Input leakage current, any input

(0 V < VIN < 3.6 V, all other inputs = 0 V)

Output leakage current

(DQ is disabled, 0 V < VOUT < VCC)

Symbol

VIH

VIL

VOH

VOL

II(L)

IO(L)

Limit Values

min.

max.

2.0 Vcc+0.3

– 0.5

0.8

2.4 –

– 0.4

– 40 40

Unit

V

V

V

V

µA

– 40

40 µA

Capacitance

TA = 0 to 70 °C; VDD = 3.3 V ± 0.3 V, f = 1 MHz

Parameter

Symbol

Input capacitance (A0 to A11, RAS, CAS, WE)

Input capacitance (CS0 -CS3, )

Input capacitance (CLK0 - CLK3)

Input capacitance (CKE0, CKE1)

Input capacitance (DQMB0 - DQMB7)

Input / Output capacitance (DQ0-DQ63,CB0-CB7)

Input Capacitance (SCL,SA0-2)

Input/Output Capacitance

CI1

CI2

CICL

CI3

CI4

CIO

Csc

Csd

Limit Values

max.

(x64)

max.

(x72)

80 90

30 35

38 38

50 55

15 20

20 20

88

10 10

Unit

pF

pF

pF

pF

pF

pF

pF

pF

Semiconductor Group

5

5 Page

HYS64(72)V4120GU-10

4M x 64/72 SDRAM-Module

SPD-Table (contd’ ):

Byte#

Description

29 Minimum RAS to CAS delay tRCD

30 Minimum Ras pulse width tRAS

31 Module Bank Density (per bank)

32-61 Superset information (may be used in

future)

62 SPD Revision

63 Checksum for bytes 0 - 62

64- Manufacturess’ information (optional)

127 (FFh if not used)

128+ Unused storage locations

SPD Entry Value

30 ns

45 ns

16 MByte

Hex

x64 x72

-10 -10

1E 1E

2D 2D

04 04

FF FF

Revision 1

01 01

F4 06

FF FF

FF FF

L-DIM-168-25 HYS64(72)V4120GU-10

SDRAM DIMM Module package

133,35

127,35

x)

1 10 11

42,18

66,68

A

85 94 95

40 41

B

124 125

x)

C

4,0

84

168

6,35

2,0

Detail A

6,35

2,0

Detail B

1,27 1,0 +- 0.5

Detail C

0,2 +- 0,15

x) on ECC modules only

DM168-25.WMF

Semiconductor Group

11

11 Page | ||

| Páginas | Total 11 Páginas | |

| PDF Descargar | [ Datasheet HYS72V4120GU-10.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HYS72V4120GU-10 | 3.3V 4M x 64-Bit 2 BANK SDRAM Module 3.3V 4M x 72-Bit 2 BANK SDRAM Module | Siemens |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |