|

|

PDF UPD31172 Data sheet ( Hoja de datos )

| Número de pieza | UPD31172 | |

| Descripción | VRC4172TM COMPANION CHIP FOR VR4121TM | |

| Fabricantes | NEC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de UPD31172 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

DATA SHEET

MOS INTEGRATED CIRCUIT

µPD31172

VRC4172TM

COMPANION CHIP FOR VR4121TM

DESCRIPTION

The µPD31172 (commercial name: VRC4172) is a companion chip designed for NEC’s µPD30121 microprocessor

(commercial name: VR4121).

The VRC4172 has the following functions available on chip: a USB host controller, an IEEE1284 parallel controller,

a 16550 serial controller, a PS/2 controller, general-purpose ports (GPIO), programmable chip select (PCS), and a

PWM controller (a duty modulated light pulse generation function for LCD backlighting).

The VRC4172 can be directly connected to the VR4121, allowing a reduction in the man-hours required for

development of a Windows™ CE system.

Detailed function descriptions are provided in the following user’s manual. Be sure to read it before

designing.

• VRC4172 User’s Manual (U14386E)

FEATURES

• Directly connectable to VR4121

• On-chip USB host controller

• USB ports: 2

• Compliant with the USB OpenHCI specifications, release 1.0

• Communicates with USB device asynchronously with host CPU

• Full-speed (12 Mbps) and low-speed (1.5 Mbps) modes supported

• System clock: 48 MHz

• On-chip PS/2 controller

• On-chip IEEE1284 parallel controller

• On-chip 16550 serial controller

• General-purpose ports (GPIO): 24

• On-chip PWM controller

• Duty modulated light pulse generation function for LCD backlighting

• Internal maximum operating frequency: 48 MHz

• Power supply voltage: VDD = 3.3 V ± 0.3 V

• Package: 208-pin plastic FBGA

APPLICATIONS

• Battery-driven portable information devices

• Peripheral devices for PCs, etc.

The information in this document is subject to change without notice. Before using this document, please

confirm that this is the latest version.

Not all devices/types available in every country. Please check with local NEC representative for

availability and additional information.

Document No. U14388EJ2V0DS00 (2nd edition)

Date Published May 2000 N CP(K)

Printed in Japan

The mark shows major revised points.

1 page

µPD31172

PIN IDENTIFICATION

ACK#:

AD (0:24):

ARBCLKSEL:

AUTOFEED#:

BUSAK (0:1)#:

BUSCLK:

BUSRQ (0:1)#:

BUSY:

CD (0:7):

CKE:

CLKOUT48M:

CTS#:

DATA (0:31):

DCD#:

DIR1284:

DN (1:2):

DP (1:2):

DSR#:

DTR#:

ERROR#:

EXCS (0:5)#:

GND:

GPIO (0:23):

HOLDAK#:

HOLDRQ#:

IEN:

INIT#

INTRP:

IOCHRDY:

IOCS16#:

IOR#:

IOW#:

IRQ:

LCAS#:

LCDBAK:

LCDCS#:

LCDRDY:

Acknowledge

Address Bus

Arbitration Clock Select

Autofeed

Bus Acknowledge

System Bus Clock

Bus Request

Busy

Centronics Data

Clock Enable

Clock Out of 48 MHz

Clear to Send

Data Bus

Data Carrier Detect

Direction of 1284

USB D−

USB D+

Data Set Ready

Data Terminal Ready

Error

External CS

Ground

General Purpose I/O

Hold Acknowledge

Hold Request

USB Input Enable

Initialize

Interrupt

I/O Channel Ready

IO Chip Select 16

I/O Read

I/O Write

I/O Request

Lower Column Address Strobe

LCD Back Light

LCD Chip Select

LCD Ready

Remark # indicates active low.

MRAS (0:1)#:

OCI (1:2):

PE:

PPON (1:2):

PS2CLK:

PS2DATA:

PS2INT:

RD#:

RESET:

RI#:

ROMCS (2:3)#:

RTS#:

RXD:

SCAS#:

SCLK:

SELECT:

SELECTIN#:

SMI#:

SRAS#:

STROBE#:

TXD:

UCAS#:

ULCAS#:

USBINT#:

USBRST#:

UUCAS#:

VDD:

WAKE:

WR#:

XIN48M:

XOUT48M:

DRAM Row Address Strobe

Over Current Interrupt

Paper End

Port Power ON

PS2 Clock

PS2 Data

PS2 Interrupt

Read

Reset

Ring Indicator

ROM Chip Select

Request to Send

Receive Data

Column Address Strobe for

SDRAM

SDRAM Clock

Select

Select in

USB System Interrupt

Row Address Strobe for

SDRAM

Strobe

Transmit Data

Upper Column Address Strobe

Lower Byte of Upper Column

Address Strobe

USB Interrupt

USB Reset

Upper Byte of Upper Column

Address Strobe

Power Supply Voltage

Wake Up Interrupt

Write

Clock In of 48 MHz

Clock Out of 48 MHz

Data Sheet U14388EJ2V0DS00

5

5 Page

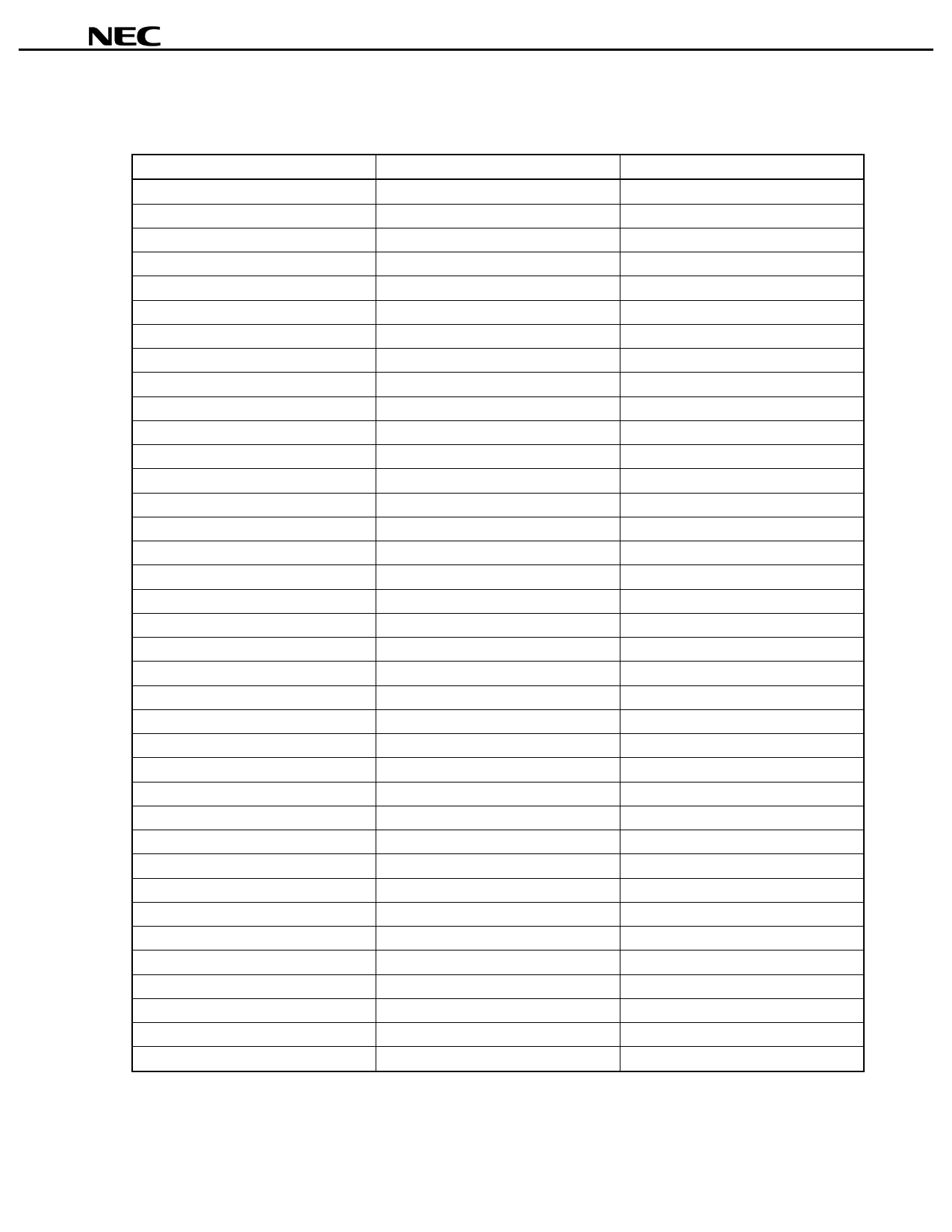

1.2 Special Status Pins

Signal Name

SCLK

AD (0:24)

DATA (0:31)

LCDCS#

RD#

WR#

LCDRDY

ROMCS (2:3)#

CKE

UUCAS#

ULCAS#

MRAS (0:1)#

UCAS#

LCAS#

IOR#

IOW#

RESET

IOCS16#

IOCHRDY

HOLDRQ#

HOLDAK#

SRAS#

SCAS#

BUSRQ (0:1)#

BUSAK (0:1)#

INTRP

IRQ

USBINT#

PS2INT

BUSCLK

ARBCLKSEL

DP (1:2)

DN (1:2)

PPON (1:2)

OCI (1:2)

IEN

WAKE

After Reset

Hi-Z

Hi-Z

Hi-Z

−

Hi-Z

Hi-Z

Hi-Z

Hi-Z

Hi-Z

Hi-Z

Hi-Z

Hi-Z

Hi-Z

Hi-Z

−

−

−

Hi-Z

Hi-Z

1

−

Hi-Z

Hi-Z

−

1

0

0

1

0

−

−

1

0

0

−

−

0

Remark 0: Low level, 1: High level, Hi-Z: High impedance

Data Sheet U14388EJ2V0DS00

µPD31172

When HOLDAK# = 1

Hi-Z

Hi-Z

Hi-Z

−

Hi-Z

Hi-Z

Hi-Z

Hi-Z

Hi-Z

Hi-Z

Hi-Z

Hi-Z

Hi-Z

Hi-Z

−

−

−

Hi-Z

Hi-Z

1

−

Hi-Z

Hi-Z

−

Normal operation

Normal operation

Normal operation

Normal operation

Normal operation

−

−

Normal operation

Normal operation

Normal operation

−

−

Normal operation

(1/2)

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet UPD31172.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| UPD31172 | VRC4172TM COMPANION CHIP FOR VR4121TM | NEC |

| UPD31172F1-48-FN | VRC4172TM COMPANION CHIP FOR VR4121TM | NEC |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |