|

|

PDF XCS05XL Data sheet ( Hoja de datos )

| Número de pieza | XCS05XL | |

| Descripción | Spartan and Spartan-XL Families Field Programmable Gate Arrays | |

| Fabricantes | Xilinx | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de XCS05XL (archivo pdf) en la parte inferior de esta página. Total 70 Páginas | ||

|

No Preview Available !

0

R Spartan and Spartan-XL Families

Field Programmable Gate Arrays

DS060 (v1.6) September 19, 2001

0 0 Product Specification

Introduction

The Spartan™ and the Spartan-XL families are a high-vol-

ume production FPGA solution that delivers all the key

requirements for ASIC replacement up to 40,000 gates.

These requirements include high performance, on-chip

RAM, core solutions and prices that, in high volume,

approach and in many cases are equivalent to mask pro-

grammed ASIC devices.

The Spartan series is the result of more than 14 years of

FPGA design experience and feedback from thousands of

customers. By streamlining the Spartan series feature set,

leveraging advanced process technologies and focusing on

total cost management, the Spartan series delivers the key

features required by ASIC and other high-volume logic

users while avoiding the initial cost, long development

cycles and inherent risk of conventional ASICs. The Spar-

tan and Spartan-XL families in the Spartan series have ten

members, as shown in Table 1.

• System level features

- Available in both 5V and 3.3V versions

- On-chip SelectRAM™ memory

- Fully PCI compliant

- Full readback capability for program verification

and internal node observability

- Dedicated high-speed carry logic

- Internal 3-state bus capability

- Eight global low-skew clock or signal networks

- IEEE 1149.1-compatible Boundary Scan logic

- Low cost plastic packages available in all densities

- Footprint compatibility in common packages

• Fully supported by powerful Xilinx development system

- Foundation Series: Integrated, shrink-wrap

software

- Alliance Series: Dozens of PC and workstation

third party development systems supported

- Fully automatic mapping, placement and routing

Spartan and Spartan-XL Features

Note: The Spartan series devices described in this data

sheet include the 5V Spartan family and the 3.3V

Spartan-XL family. See the separate data sheet for the 2.5V

Spartan-II family.

• First ASIC replacement FPGA for high-volume

production with on-chip RAM

• Density up to 1862 logic cells or 40,000 system gates

• Streamlined feature set based on XC4000 architecture

• System performance beyond 80 MHz

• Broad set of AllianceCORE™ and LogiCORE™

predefined solutions available

• Unlimited reprogrammability

• Low cost

Additional Spartan-XL Features

• 3.3V supply for low power with 5V tolerant I/Os

• Power down input

• Higher performance

• Faster carry logic

• More flexible high-speed clock network

• Latch capability in Configurable Logic Blocks

• Input fast capture latch

• Optional mux or 2-input function generator on outputs

• 12 mA or 24 mA output drive

• 5V and 3.3V PCI compliant

• Enhanced Boundary Scan

• Express Mode configuration

• Chip scale packaging

Table 1: Spartan and Spartan-XL Field Programmable Gate Arrays

Device

Max

Logic System

Typical

Gate Range

Cells Gates (Logic and RAM)(1)

CLB

Matrix

Max.

Total

Total No. of Avail. Distributed

CLBs Flip-flops User I/O RAM Bits

XCS05 and XCS05XL 238 5,000

2,000-5,000

10 x 10 100

360

77

3,200

XCS10 and XCS10XL 466 10,000

3,000-10,000

14 x 14 196

616

112

6,272

XCS20 and XCS20XL 950 20,000

7,000-20,000

20 x 20 400

1,120

160

12,800

XCS30 and XCS30XL 1368 30,000

10,000-30,000 24 x 24 576

1,536

192

18,432

XCS40 and XCS40XL 1862 40,000

13,000-40,000 28 x 28 784

2,016

224

25,088

Notes:

1. Max values of Typical Gate Range include 20-30% of CLBs used as RAM.

© 2001 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at http://www.xilinx.com/legal.htm.

All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

DS060 (v1.6) September 19, 2001

Product Specification

www.xilinx.com

1-800-255-7778

1

1 page

R Spartan and Spartan-XL Families Field Programmable Gate Arrays

.

Table 2: CLB Storage Element Functionality

Mode

CK EC SR

D

Q

Power-Up or

GSR

XX

X X SR

Flip-Flop

Operation

X X 1 X SR

1* 0* D D

0 X 0* X Q

Latch

1 1* 0* X Q

Operation

(Spartan-XL)

0

1* 0*

D

D

Both

X 0 0* X Q

Legend:

X Don’t care

Rising edge (clock not inverted).

SR Set or Reset value. Reset is default.

0* Input is Low or unconnected (default

value)

1* Input is High or unconnected (default

value)

SR

GND

GSR

D

SD

DQ

Q

CK

EC

Vcc

RD

Multiplexer Controlled

by Configuration Program

DS060_03_041901

Figure 3: CLB Flip-Flop Functional Block Diagram

Clock Input

Each flip-flop can be triggered on either the rising or falling

clock edge. The CLB clock line is shared by both flip-flops.

However, the clock is individually invertible for each flip-flop

(see CK path in Figure 3). Any inverter placed on the clock

line in the design is automatically absorbed into the CLB.

Clock Enable

The clock enable line (EC) is active High. The EC line is

shared by both flip-flops in a CLB. If either one is left discon-

nected, the clock enable for that flip-flop defaults to the

active state. EC is not invertible within the CLB. The clock

enable is synchronous to the clock and must satisfy the

setup and hold timing specified for the device.

Set/Reset

The set/reset line (SR) is an asynchronous active High con-

trol of the flip-flop. SR can be configured as either set or

reset at each flip-flop. This configuration option determines

the state in which each flip-flop becomes operational after

configuration. It also determines the effect of a GSR pulse

during normal operation, and the effect of a pulse on the SR

line of the CLB. The SR line is shared by both flip-flops. If

SR is not specified for a flip-flop the set/reset for that flip-flop

defaults to the inactive state. SR is not invertible within the

CLB.

CLB Signal Flow Control

In addition to the H-LUT input control multiplexers (shown in

box "A" of Figure 2, page 4) there are signal flow control

multiplexers (shown in box "B" of Figure 2) which select the

signals which drive the flip-flop inputs and the combinatorial

CLB outputs (X and Y).

Each flip-flop input is driven from a 4:1 multiplexer which

selects among the three LUT outputs and DIN as the data

source.

Each combinatorial output is driven from a 2:1 multiplexer

which selects between two of the LUT outputs. The X output

can be driven from the F-LUT or H-LUT, the Y output from

G-LUT or H-LUT.

Control Signals

There are four signal control multiplexers on the input of the

CLB. These multiplexers allow the internal CLB control sig-

nals (H1, DIN, SR, and EC in Figure 2 and Figure 4) to be

driven from any of the four general control inputs (C1-C4 in

Figure 4) into the CLB. Any of these inputs can drive any of

the four internal control signals.

DS060 (v1.6) September 19, 2001

Product Specification

www.xilinx.com

1-800-255-7778

5

5 Page

R Spartan and Spartan-XL Families Field Programmable Gate Arrays

PSM

PSM

PSM

CLB

PSM

CLB

PSM

8 Singles

2 Doubles

3 Longs

PSM

3 Longs

2 Doubles

2 Doubles

3 Longs 8 Singles 3 Longs

2 Doubles

DS060_09_041901

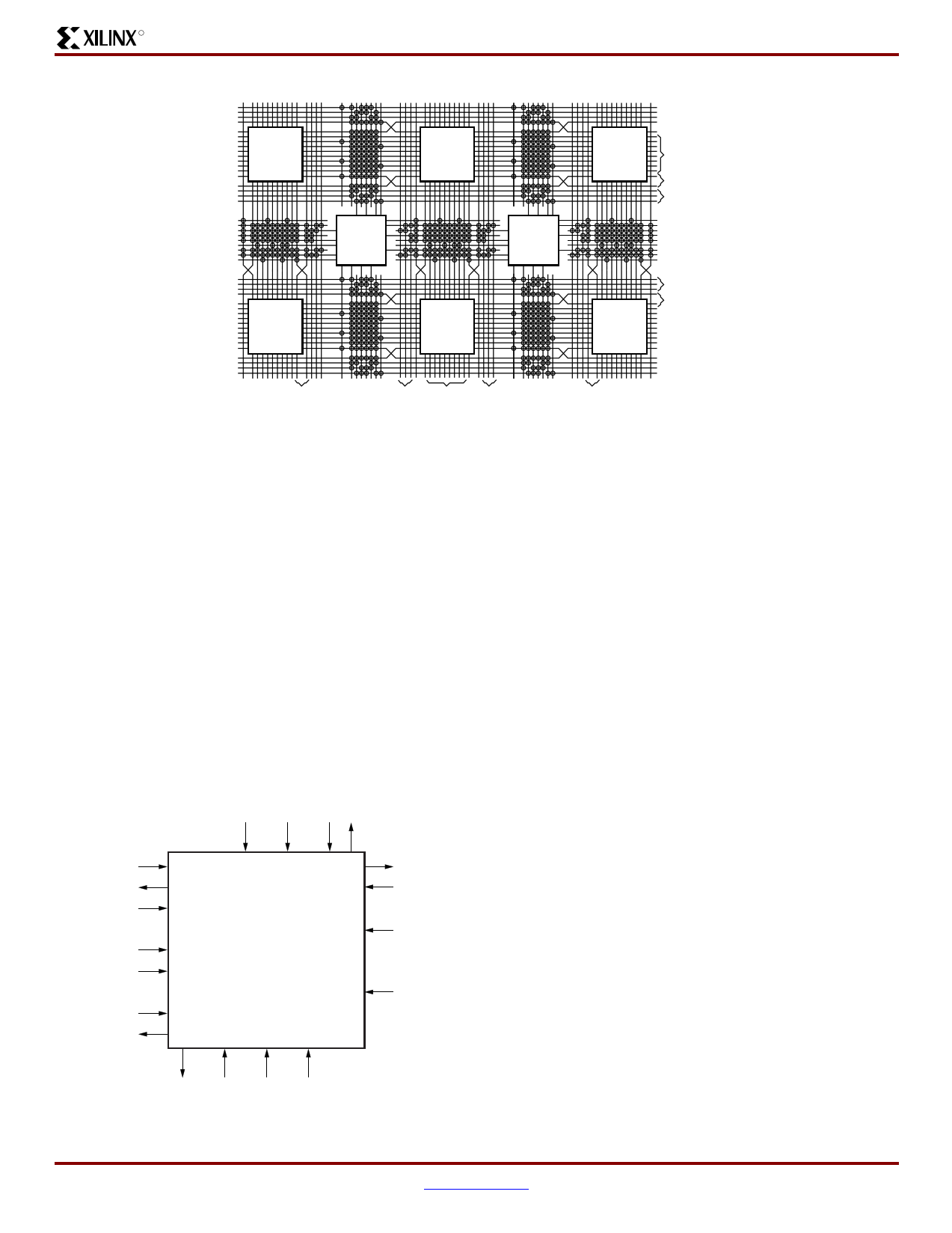

Figure 8: Spartan/XL CLB Routing Channels and Interface Block Diagram

CLB Interface

A block diagram of the CLB interface signals is shown in

Figure 9. The input signals to the CLB are distributed evenly

on all four sides providing maximum routing flexibility. In

general, the entire architecture is symmetrical and regular.

It is well suited to established placement and routing algo-

rithms. Inputs, outputs, and function generators can freely

swap positions within a CLB to avoid routing congestion

during the placement and routing operation. The exceptions

are the clock (K) input and CIN/COUT signals. The K input

is routed to dedicated global vertical lines as well as four

single-length lines and is on the left side of the CLB. The

CIN/COUT signals are routed through dedicated intercon-

nects which do not interfere with the general routing struc-

ture. The output signals from the CLB are available to drive

both vertical and horizontal channels.

CIN

COUT

G1

C1

K

F1

X

CLB

Rev 1.1

Y

G3

C3

F3

Programmable Switch Matrices

The horizontal and vertical single- and double-length lines

intersect at a box called a programmable switch matrix

(PSM). Each PSM consists of programmable pass transis-

tors used to establish connections between the lines (see

Figure 10).

For example, a single-length signal entering on the right

side of the switch matrix can be routed to a single-length

line on the top, left, or bottom sides, or any combination

thereof, if multiple branches are required. Similarly, a dou-

ble-length signal can be routed to a double-length line on

any or all of the other three edges of the programmable

switch matrix.

Single-Length Lines

Single-length lines provide the greatest interconnect flexibil-

ity and offer fast routing between adjacent blocks. There are

eight vertical and eight horizontal single-length lines associ-

ated with each CLB. These lines connect the switching

matrices that are located in every row and column of CLBs.

Single-length lines are connected by way of the program-

mable switch matrices, as shown in Figure 10. Routing con-

nectivity is shown in Figure 8.

Single-length lines incur a delay whenever they go through

a PSM. Therefore, they are not suitable for routing signals

for long distances. They are normally used to conduct sig-

nals within a localized area and to provide the branching for

nets with fanout greater than one.

DS060_08_081100

Figure 9: CLB Interconnect Signals

DS060 (v1.6) September 19, 2001

Product Specification

www.xilinx.com

1-800-255-7778

11

11 Page | ||

| Páginas | Total 70 Páginas | |

| PDF Descargar | [ Datasheet XCS05XL.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| XCS05XL | Spartan and Spartan-XL Families Field Programmable Gate Arrays | Xilinx |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |