|

|

PDF ISL6532C Data sheet ( Hoja de datos )

| Número de pieza | ISL6532C | |

| Descripción | ACPI Regulator/Controller for Dual Channel DDR Memory Systems | |

| Fabricantes | Intersil Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ISL6532C (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

®

Data Sheet

December 2003

ISL6532C

FN9121.1

ACPI Regulator/Controller for

Dual Channel DDR Memory Systems

The ISL6532C provides a complete ACPI compliant power

solution for up to 4 DIMM dual channel DDR/DDR2 Memory

systems. Included are both a synchronous buck controller

and integrated LDO to supply VDDQ with high current during

S0/S1 states and standby current during S3 state. During

S0/S1 state, a fully integrated sink-source regulator

generates an accurate (VDDQ/2) high current VTT voltage

without the need for a negative supply. A buffered version of

the VDDQ/2 reference is provided as VREF. An LDO

controller is also integrated for AGP core voltage regulation.

The switching PWM controller drives two N-Channel

MOSFETs in a synchronous-rectified buck converter

topology. The synchronous buck converter uses voltage-

mode control with fast transient response. Both the switching

regulator and standby LDO provide a maximum static

regulation tolerance of ±2% over line, load, and temperature

ranges. The output is user-adjustable by means of external

resistors down to 0.8V.

Switching memory core output between the PWM regulator

and the standby LDO during state transitions is

accomplished smoothly via the internal ACPI control

circuitry. The NCH signal provides synchronized switching of

a backfeed blocking switch during the transitions eliminating

the need to route 5V Dual to the memory supply.

An integrated soft-start feature brings all outputs into

regulation in a controlled manner when returning to S0/S1

state from any sleep state. During S0 the PGOOD signal

indicates VTT is within spec and operational.

Each output is monitored for under and over-voltage events.

The switching regulator has over current protection. Thermal

shutdown is integrated.

Pinout

ISL6532C (QFN) TOP VIEW

28 27 26 25 24 23 22

GNDP 1

21 PGOOD

5VSBY 2

20 PHASE

GNDQ 3

19 DRIVE2

GNDQ 4

18 FB2

VTT 5

17 GNDA

VTT 6

16 COMP

VDDQ 7

15 FB

8 9 10 11 12 13 14

Features

• Generates 3 Regulated Voltages

- Synchronous Buck PWM Controller with Standby LDO

- 3A Integrated Sink/Source Linear Regulator with

Accurate VDDQ/2 Divider Reference.

- Glitch-free Transitions During State Changes

- LDO Regulator for 1.5V Video and Core voltage

• ACPI compliant sleep state control

• Integrated VREF Buffer

• PWM Controller Drives Low Cost N-Channel MOSFETs

• 250kHz Constant Frequency Operation

• Tight Output Voltage Regulation

- All Outputs: ±2% Over Temperature

• 5V or 3.3V Down Conversion

• Fully-Adjustable Outputs with Wide Voltage Range: Down

to 0.8V supports DDR and DDR2 Specifications

• Simple Single-Loop Voltage-Mode PWM Control Design

• Fast PWM Converter Transient Response

• Under and Over-voltage Monitoring on All Outputs

• OCP on the Switching Regulator and VTT

• Integrated Thermal Shutdown Protection

• QFN Package Option

- QFN Compliant to JEDEC PUB95 MO-220 QFN - Quad

Flat No Leads - Product Outline

- QFN Near Chip Scale Package Footprint; Improves

PCB Efficiency, Thinner in Profile

Applications

• Single and Dual Channel DDR Memory Power Systems in

ACPI compliant PCs

• Graphics cards - GPU and memory supplies

• ASIC power supplies

• Embedded processor and I/O supplies

• DSP supplies

Ordering Information

TEMP. RANGE

PART NUMBER

(oC)

PACKAGE PKG. DWG. #

ISL6532CCR

0 to 70

28 Ld 6x6 QFN L28.6x6

1 CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143 | Intersil (and design) is a registered trademark of Intersil Americas Inc.

Copyright © Intersil Americas Inc. 2003. All Rights Reserved.

All other trademarks mentioned are the property of their respective owners.

1 page

ISL6532C

Absolute Maximum Ratings

5VSBY, P5VSBY . . . . . . . . . . . . . . . . . . . . . . . . . GND - 0.3V to +7V

P12V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . GND - 0.3V to +14V

UGATE, LGATE, NCH . . . . . . . . . . . . . . GND - 0.3V to P12V + 0.3V

All other Pins . . . . . . . . . . . . . . . . . . . . GND - 0.3V to 5VCC + 0.3V

ESD Classification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Level 1

Recommended Operating Conditions

Supply Voltage on 5VSBY . . . . . . . . . . . . . . . . . . . . . . . . +5V ±10%

Supply Voltage on P12V . . . . . . . . . . . . . . . . . . . . . . . . +12V ±10%

Supply Voltage on P5VSBY. . . . . . . . . . . . . . . . . . . . . . . +5V ±10%

Ambient Temperature Range. . . . . . . . . . . . . . . . . . . . 0oC to 70oC

Junction Temperature Range . . . . . . . . . . . . . . . . . . 0oC to 125oC

Thermal Information

Thermal Resistance (Typical, Notes 1, 2) θJA (oC/W) θJC (oC/W)

QFN Package . . . . . . . . . . . . . . . . . . .

32

5

Maximum Junction Temperature (Plastic Package) . . . . . . . 150oC

Maximum Storage Temperature Range . . . . . . . . . -65oC to 150oC

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . 300oC

(SOIC - Lead Tips Only)

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTES:

1. θJA is measured in free air with the component mounted on a high effective thermal conductivity test board with “direct attach” features. See

Tech Brief TB379.

2. For θJC, the “case temp” location is the center of the exposed metal pad on the package underside.

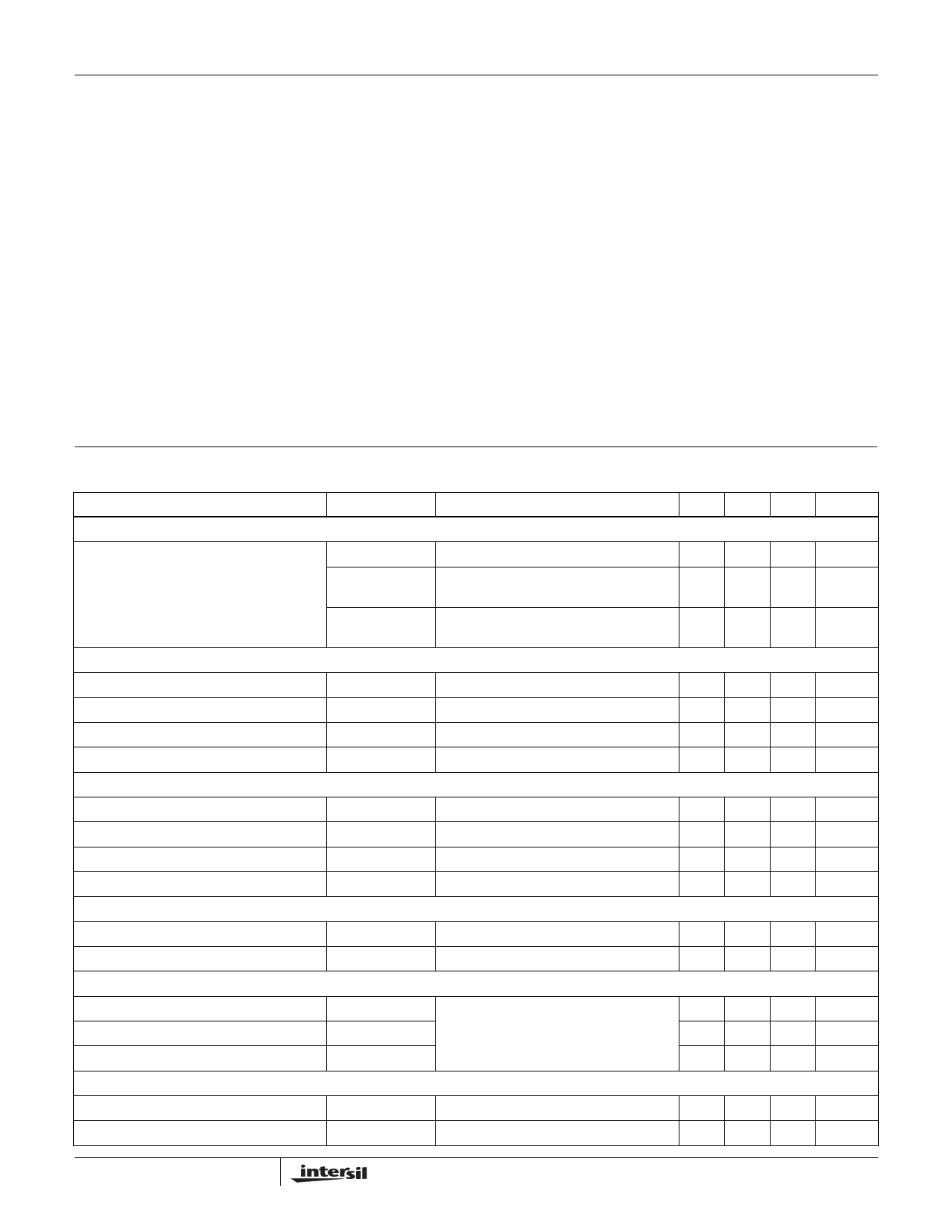

Electrical Specifications Recommended Operating Conditions, Unless Otherwise Noted. Refer to Block and Simplified Power System

Diagrams and Typical Application Schematics

PARAMETER

SYMBOL

TEST CONDITIONS

MIN TYP MAX UNITS

5VSBY SUPPLY CURRENT

Nominal Supply Current

ICC_S0

ICC_S3

S3# & S5# HIGH, UGATE/LGATE Open

S3# LOW, S5# HIGH, UGATE/LGATE

Open

3.00 5.25 7.25

3.50 - 4.75

mA

mA

ICC_S5

S5# LOW, S3# Don’t Care,

UGATE/LGATE Open

300 - 800

µA

POWER-ON RESET

Rising 5VSBY POR Threshold

4.00 - 4.35

V

Falling 5VSBY POR Threshold

3.60 - 3.95

V

Rising P12V POR Threshold

10.0 - 10.5

V

Falling P12V POR Threshold

8.80 - 9.75

V

OSCILLATOR AND SOFT-START

PWM Frequency

Ramp Amplitude

Error Amp Reset Time

VDDQ Soft-Start Interval

REFERENCE VOLTAGE

fOSC

∆VOSC

tRESET

tSS

Mechanical Off/S5 to S0

Mechanical Off/S5 to S0

220 250 280

- 1.5 -

6.5 - 9.5

6.5 - 9.5

kHz

V

ms

ms

Reference Voltage

System Accuracy

VREF

- 0.800 -

-2.0 - +2.0

V

%

PWM CONTROLLER ERROR AMPLIFIER

DC Gain

Guaranteed By Design

- 80 -

dB

Gain-Bandwidth Product

GBWP

15 -

- MHz

Slew Rate

SR

- 6 - V/µs

STATE LOGIC

S3# Transition Level

S5# Transition Level

VS3

VS5

- 1.5 -

- 1.5 -

V

V

5

5 Page

ISL6532C

Application Guidelines

Layout Considerations

Layout is very important in high frequency switching

converter design. With power devices switching efficiently at

250kHz, the resulting current transitions from one device to

another cause voltage spikes across the interconnecting

impedances and parasitic circuit elements. These voltage

spikes can degrade efficiency, radiate noise into the circuit,

and lead to device over-voltage stress. Careful component

layout and printed circuit board design minimizes these

voltage spikes.

As an example, consider the turn-off transition of the control

MOSFET. Prior to turn-off, the MOSFET is carrying the full

load current. During turn-off, current stops flowing in the

MOSFET and is picked up by the lower MOSFET. Any

parasitic inductance in the switched current path generates a

large voltage spike during the switching interval. Careful

component selection, tight layout of the critical components,

and short, wide traces minimizes the magnitude of voltage

spikes.

There are two sets of critical components in the ISL6532C

switching converter. The switching components are the most

critical because they switch large amounts of energy, and

therefore tend to generate large amounts of noise. Next are

the small signal components which connect to sensitive

nodes or supply critical bypass current and signal coupling.

A multi-layer printed circuit board is recommended. Figure 4

shows the connections of the critical components in the

converter. Note that capacitors CIN and COUT could each

represent numerous physical capacitors. Dedicate one solid

layer, usually a middle layer of the PC board, for a ground

plane and make all critical component ground connections

with vias to this layer. Dedicate another solid layer as a

power plane and break this plane into smaller islands of

common voltage levels. Keep the metal runs from the

PHASE terminals to the output inductor short. The power

plane should support the input power and output power

nodes. Use copper filled polygons on the top and bottom

circuit layers for the phase nodes. Use the remaining printed

circuit layers for small signal wiring. The wiring traces from

the GATE pins to the MOSFET gates should be kept short

and wide enough to easily handle the 1A of drive current.

In order to dissipate heat generated by the internal VTT

LDO, the ground pad, pin 29, should be connected to the

internal ground plane through at least four vias. This allows

the heat to move away from the IC and also ties the pad to

the ground plane through a low impedance path.

The switching components should be placed close to the

ISL6532C first. Minimize the length of the connections

between the input capacitors, CIN, and the power switches

by placing them nearby. Position both the ceramic and bulk

input capacitors as close to the upper MOSFET drain as

12VATX

P12V

GNDP

ISL6532C

NCH

CBP

VIN_DDR

P5VSBY

5VSBY

CBP

GNDP

UGATE

PHASE

5VSBY

CIN

Q1 LOUT

VDDQ

LGATE

COMP

FB

Q2

C2

R2

C1

R1

R4 C3 R3

COUT1

VDDQ(3)

VTT(2)

VDDQ

VTT

COUT2

DRIVE2

FB2

GND PAD

R5

R6

VIN_AGP

Q3

VAGP

COUT3

KEY

ISLAND ON POWER PLANE LAYER

ISLAND ON CIRCUIT PLANE LAYER

VIA CONNECTION TO GROUND PLANE

FIGURE 4. PRINTED CIRCUIT BOARD POWER PLANES

AND ISLANDS

possible. Position the output inductor and output capacitors

between the upper and lower MOSFETs and the load.

The critical small signal components include any bypass

capacitors, feedback components, and compensation

components. Place the PWM converter compensation

components close to the FB and COMP pins. The feedback

resistors should be located as close as possible to the FB

pin with vias tied straight to the ground plane as required.

Feedback Compensation - PWM Buck Converter

Figure 5 highlights the voltage-mode control loop for a

synchronous-rectified buck converter. The output voltage

(VOUT) is regulated to the Reference voltage level. The error

amplifier output (VE/A) is compared with the oscillator (OSC)

triangular wave to provide a pulse-width modulated (PWM)

wave with an amplitude of VIN at the PHASE node.

11

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet ISL6532C.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ISL6532 | ACPI Regulator/Controller for Dual Channel DDR Memory Systems | Intersil Corporation |

| ISL6532A | ACPI Regulator/Controller for Dual Channel DDR Memory Systems | Intersil Corporation |

| ISL6532B | ACPI Regulator/Controller for Dual Channel DDR Memory Systems | Intersil Corporation |

| ISL6532C | ACPI Regulator/Controller for Dual Channel DDR Memory Systems | Intersil Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |