|

|

PDF ISL6420 Data sheet ( Hoja de datos )

| Número de pieza | ISL6420 | |

| Descripción | Advanced Single Synchronous Buck Pulse-Width Modulation (PWM) Controller | |

| Fabricantes | Intersil Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ISL6420 (archivo pdf) en la parte inferior de esta página. Total 17 Páginas | ||

|

No Preview Available !

®

Data Sheet

July 2004

ISL6420

FN9151.2

Advanced Single Synchronous Buck

Pulse-Width Modulation (PWM) Controller

The ISL6420 makes simple work out of implementing a

complete control and protection scheme for a high-

performance DC-DC buck converter. Designed to drive

N-channel MOSFETs in a synchronous rectified buck

topology, the ISL6420 integrates control, output adjustment,

monitoring and protection functions into a single package.

Additionally, the IC features an external reference voltage

tracking mode for externally referenced buck converter

applications and DDR termination supplies, as well as a

voltage margining mode for system testing in networking

DC-DC converter applications.

The ISL6420 provides simple, single feedback loop, voltage

mode control with fast transient response. The output

voltage of the converter can be precisely regulated to as low

as 0.6V, with a maximum tolerance of ±1.0% over

temperature and line voltage variations.

The operating frequency is fully adjustable from 100kHz to

1.4MHz. High frequency operation offers cost and space

savings.

The error amplifier features a 15MHz gain-bandwidth

product and 6V/µs slew rate that enables high converter

bandwidth for fast transient response. The PWM duty cycle

ranges from 0% to 100% in transient conditions. Selecting

the capacitor value from the ENSS pin to ground sets a fully

adjustable PWM soft start. Pulling the ENSS pin LOW

disables the controller.

The ISL6420 monitors the output voltage and generates a

PGOOD (power good) signal when soft start sequence is

complete and the output is within regulation. A built-in over

voltage protection circuit prevents the output voltage from

going above typically 115% of the set point. Protection from

overcurrent conditions is provided by monitoring the rDS(ON)

of the upper MOSFET to inhibit the PWM operation

appropriately. This approach simplifies the implementation

and improves efficiency by eliminating the need for a current

sensing resistor.

Features

• Operates from 4.5V to 16V Input

• Excellent Output Voltage Regulation

- 0.6V Internal Reference

- ±1.0% Reference Accuracy Over Line and Temperature

• Resistor-Selectable Switching Frequency

- 100kHz to 1.4MHz

• Voltage Margining and External Reference Tracking

Modes

• Output Can Sink or Source Current

• Lossless, Programmable Overcurrent Protection

- Uses Upper MOSFET‘s rDS(ON)

• Programmable Soft Start

• Drives N-Channel MOSFETs

• Simple Single-Loop Control Design

- Voltage-Mode PWM Control

• Fast Transient Response

- High-Bandwidth Error Amplifier

- Full 0% to 100% Duty Cycle

• Extensive Circuit Protection Functions

- PGOOD, overvoltage, overcurrent, Shutdown

• QFN (4x4) Package

- QFN Compliant to JEDEC PUB95 MO-220 QFN - Quad

Flat No Leads - Product Outline

- QFN Near Chip Scale Package Footprint; Improves

PCB Efficiency, Thinner in Profile

• Pb-free available

Applications

• Power Supplies for Microprocessors/ASICs

- Embedded Controllers

- DSP and Core Processors

- DDR SDRAM Bus Termination

• Ethernet Routers and Switchers

• High-Power DC-DC Regulators

• Distributed DC-DC Power Architecture

• Personal Computer Peripherals

• Externally Referenced Buck Converters

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143 | Intersil (and design) is a registered trademark of Intersil Americas Inc.

Copyright © Intersil Americas Inc. 2004. All Rights Reserved

All other trademarks mentioned are the property of their respective owners.

1 page

ISL6420

Absolute Maximum Ratings (Note 1)

Bias Voltage, VIN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .+18V

BOOT and Ugate Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +24V

ESD Classification

Human Body Model (Per MIL-STD-883 Method 3015.7) . . 1500V

Charged Device Model (Per EOS/ESD DS5.3, 4/14/93) . . 2000V

Thermal Information

Thermal Resistance (Typical)

θJA (°C/W) θJC (°C/W)

QFN Package (Notes 2, 3) . . . . . . . . .

47

8.5

Maximum Junction Temperature (Plastic Package) . . . . . . . . 150°C

Maximum Storage Temperature Range . . . . . . . . . . . -65°C to 150°C

Ambient Temperature Range. . . . . . . . . -40°C to 85°C (for “I” suffix)

Junction Temperature Range. . . . . . . . . . . . . . . . . . . -40°C to 125°C

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTES:

1. All voltages are with respect to GND.

2. θJA is measured in free air with the component mounted on a high effective thermal conductivity test board with “direct attach” features. See

Tech Brief TB379.

3. For θJC, the “case temp” location is the center of the exposed metal pad on the package underside.

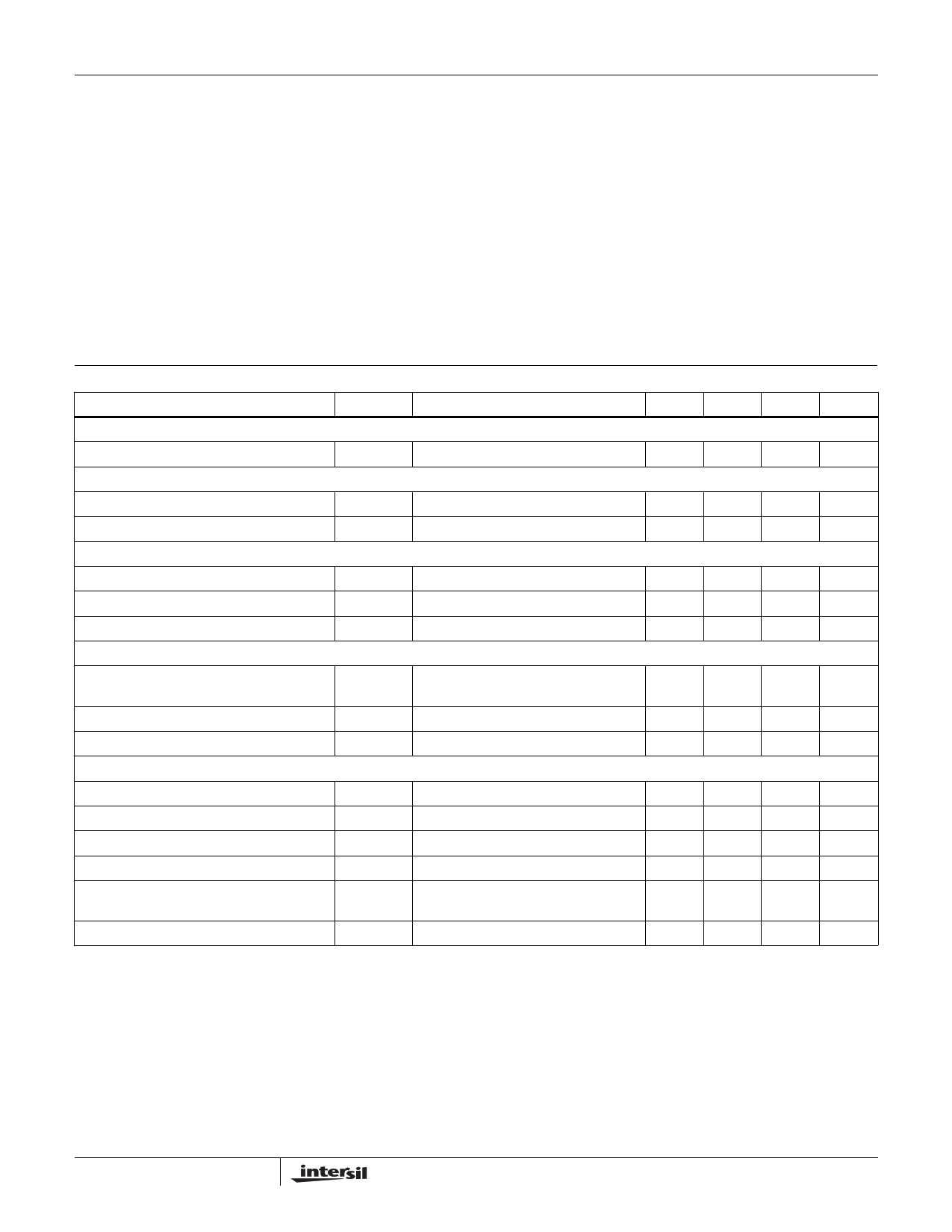

Electrical Specifications

PARAMETER

VIN SUPPLY

Input Voltage Range

VIN SUPPLY CURRENT

Shutdown Current (Note 4)

Operating Current (Notes 4, 5)

VCC5 SUPPLY (Notes 5, 6)

Input Voltage Range

Output Voltage

Maximum Output Current

POWER-ON RESET

Rising VCC5 Threshold

Falling VCC5 Threshold

UVLO Threshold Hysteresis

PWM CONVERTERS

Output Voltage (Note 7)

Maximum Duty Cycle

Minimum Duty Cycle

FB pin bias current

Undervoltage Protection

Operating Conditions, Unless Otherwise Noted: VIN = 12V, PVCC shorted with VCC5, TA = 25°C

SYMBOL

TEST CONDITIONS

MIN TYP MAX

UNITS

5.6 12 16

V

ENSS = GND

- 1.4 - mA

- 2.0 3.0 mA

VIN = VCC5 for 5V configuration

4.5 5.0 5.5

V

VIN = 5.6V to 16V, IL = 3mA to 50mA 4.5 5.0 5.5

V

VIN = 12V

50 -

- mA

VIN connected to VCC5, 5V input

operation

4.32 4.4 4.45

4.09 4.1 4.25

0.16 -

-

V

V

V

VUV1

F = 300kHz

F = 300kHz

Fraction of the set point; ~3µs noise filter

0.6

90

-

-

75

- VIN - 0.5 V

96 - %

- 0%

80 - nA

- 85 %

Overvoltage Protection

VOVP1 Fraction of the set point; ~1µs noise filter 112 - 120 %

5

5 Page

ISL6420

Functional Description

Initialization

The ISL6420 automatically initializes upon receipt of power.

The Power-On Reset (POR) function monitors the internal

bias voltage generated from LDO output (VCC5) and the

ENSS pin. The POR function initiates the soft start operation

after the VCC5 exceeds the POR threshold. The POR

function inhibits operation with the chip disabled (ENSS pin

<1V).

The device can operate from an input supply voltage of 5.6V

to 16V connected directly to the VIN pin using the internal 5V

linear regulator to bias the chip and supply the gate drivers.

For 5V ±10% applications, connect VIN to VCC5 to bypass

the linear regulator.

Soft Start / Enable

The ISL6420 soft start function uses an internal current

source and an external capacitor to reduce stresses and

surge current during startup.

When the output of the internal linear regulator reaches the

POR threshold, the POR function initiates the soft start

sequence. An internal 10µA current source charges an

external capacitor on the ENSS pin linearly from 0V to 3.3V.

When the ENSS pin voltage reaches 1V typically, the

internal 0.6V reference begins to charge following the dv/dt

of the ENSS voltage. As the soft start pin charges from 1V to

1.6V, the reference voltage charges from 0V to 0.6V.

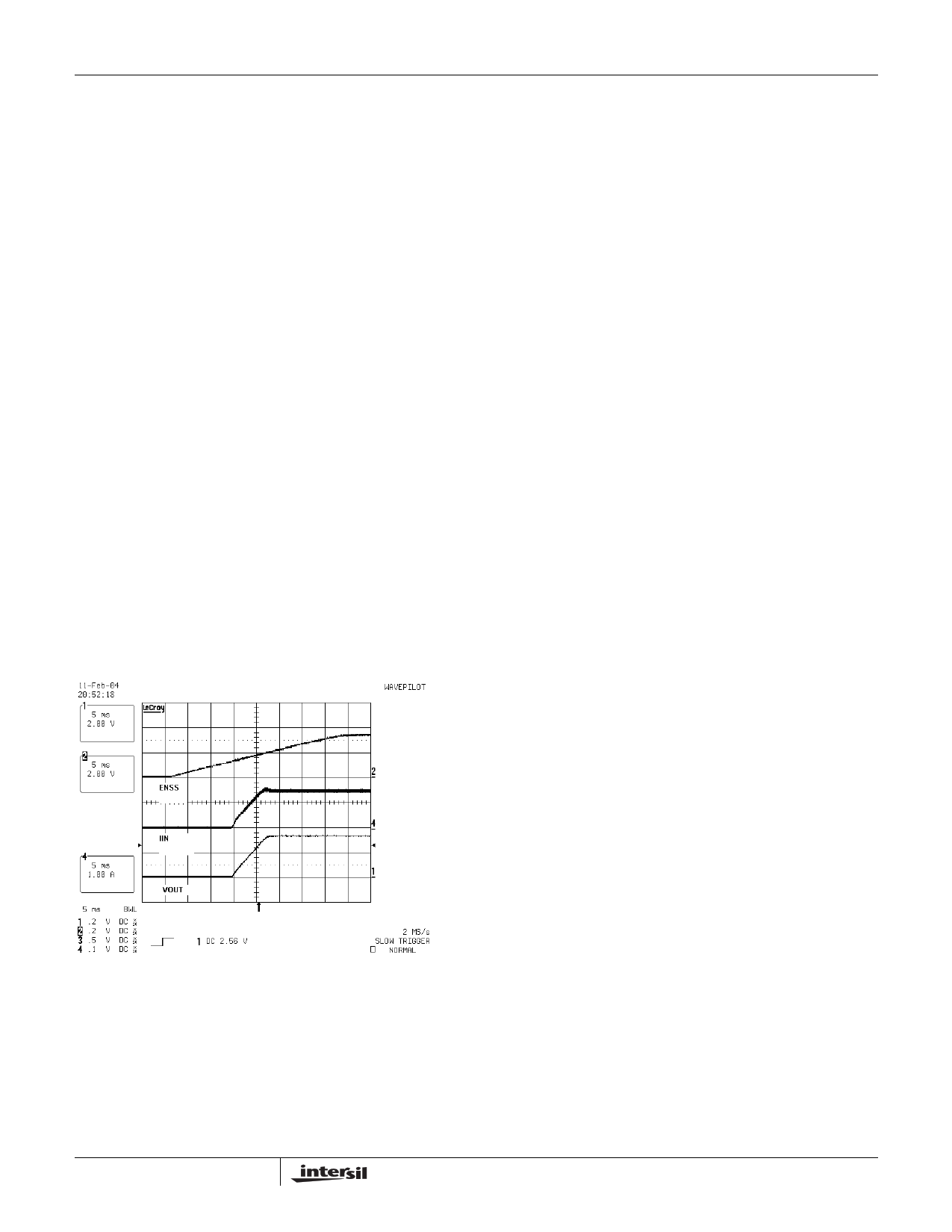

Figure 8 shows a typical soft start sequence.

FIGURE 8. TYPICAL SOFT START WAVEFORM

Overcurrent Protection

The overcurrent function protects the converter from a

shorted output by using the upper MOSFET’s on-resistance,

rDS(ON) to monitor the current. This method enhances the

converter’s efficiency and reduces cost by eliminating a

current sensing resistor.

The overcurrent function cycles the soft-start function in a

hiccup mode to provide fault protection. A resistor connected

to the drain of the upper FET and the OCSET pin programs

the overcurrent trip level. The PHASE node voltage will be

compared against the voltage on the OCSET pin, while the

upper FET is on. A current (100µA typically) is pulled from

the OCSET pin to establish the OCSET voltage. If PHASE is

lower than OCSET while the upper FET is on then an over

current condition is detected for that clock cycle. The upper

gate pulse is immediately terminated, and a counter is

incremented. If an overcurrent condition is detected for

8 consecutive clock cycles, and the circuit is not in soft start,

the ISL6420 enters into the soft start hiccup mode. During

hiccup, the external capacitor on the ENSS pin is

discharged. After the cap is discharged, it is released and a

soft start cycle is initiated. During soft start, pulse termination

current limiting is enabled, but the 8-cycle hiccup counter is

held in reset until soft start is completed.

The overcurrent function will trip at a peak inductor current

(IOC) determined from Equation 1, where IOCSET is the

internal OCSET current source.

The OC trip point varies mainly due to the upper MOSFETs

rDS(ON) variations. To avoid overcurrent tripping in the

normal operating load range, find the ROCSET resistor from

the equation above with:

1. The maximum rDS(ON) at the highest junction

temperature.

2. Determine IOC for IOC > IOUT(MAX) + (∆I) ⁄ 2 ,

where ∆I is the output inductor ripple current.

A small ceramic capacitor should be placed in parallel with

ROCSET to smooth the voltage across ROCSET in the

presence of switching noise on the input voltage.

Voltage Margining

The ISL6420 has a voltage margining mode that can be

used for system testing. The voltage margining percentage

is resistor selectable up to ±10%. The voltage margining

mode can be enabled by connecting a margining set resistor

from VMSET pin to ground and using the control pins

GPIO1/2 to toggle between positive and negative margining

(Refer to Table 2). With voltage margining enabled, the

VMSET resistor to ground will set a current, which is

switched to the FB pin. The current will be equal to 2.468V

divided by the value of the external resistor tied to the

VMSET pin.

IVM = R---2--V-.--4-M--6---S-8---EV----T-

(EQ. 2)

∆VVM = 2.468V R-----V--R--M--F---S-B---E----T-

(EQ. 3)

The power supply output increases when GPIO2 is HIGH

and decreases when GPIO1 is HIGH. The amount that the

11

11 Page | ||

| Páginas | Total 17 Páginas | |

| PDF Descargar | [ Datasheet ISL6420.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ISL6420 | Advanced Single Synchronous Buck Pulse-Width Modulation (PWM) Controller | Intersil Corporation |

| ISL6420A | Advanced Single Synchronous Buck Pulse-Width Modulation (PWM) Controller | Intersil |

| ISL6420B | Advanced Single Synchronous Buck Pulse-Width Modulation (PWM) Controller | Intersil Corporation |

| ISL6421 | Single Output LNB Supply and Control Voltage Regulator with I2C Interface for Advanced Satellite Set-top Box Designs | Intersil Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |