|

|

PDF ISL5314 Data sheet ( Hoja de datos )

| Número de pieza | ISL5314 | |

| Descripción | Direct Digital Synthesizer | |

| Fabricantes | Intersil Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ISL5314 (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

TM

Data Sheet

Direct Digital Synthesizer

The 14-bit ISL5314 provides a

complete Direct Digital Synthesizer

(DDS) system in a single 48-pin

LQFP package. A 48-bit Programmable Carrier NCO

(numerically controlled oscillator) and a high speed 14-bit

DAC (digital to analog converter) are integrated into a stand

alone DDS.

The DDS accepts 48-bit center and offset frequency control

information via a parallel processor interface. A 40-bit

frequency tuning word can also be loaded via an asynchronous

serial interface. Modulation control is provided by 3 external

pins. The PH0 and PH1 pins select phase offsets of 0, 90,

180 and 270 degrees, while the ENOFR pin enables or

zeros the offset frequency word to the phase accumulator.

The parallel processor interface has an 8-bit write-only data

input C(7:0), a 4-bit address A(3:0) bus, a Write Strobe

(WR), and a Write Enable (WE). The processor can update

all registers simultaneously by loading a set of master

registers, then transfer all master registers to the slave

registers by asserting the UPDATE pin.

Ordering Information

PART

NUMBER

TEMP. RANGE

(oC)

PACKAGE

PKG. NO.

ISL5314IN

-40 to 85 48 LQFP

Q48.7X7A

ISL5314EVAL2

25 Evaluation Board

Block Diagram

C(7:0)

A(3:0)

WR

WE

UPDATE

SDATA

SSYNC

SCLK

ENOFR

PH(1:0)

RESET

CLK

PHASE

ACCUM.

∑

SINE

WAVE

ROM

+-

14 BIT

DAC

INT

REF

IN-

IN+

COMP1

COMP2

IOUTA

IOUTB

REFIO

REFLO

ISL5314

September 2001

File Number 4901.1

Features

• 125MSPS output sample rate with 5V digital supply

• 100MSPS output sample rate with 3.3V digital supply

• 14-bit digital-to-analog (DAC) with internal reference

• Parallel control interface for fast tuning (50MSPS control

register write rate) and serial control interface

• 48-bit programmable frequency control

• Offset frequency register and enable pin for fast FSK

• Small 48-pin LQFP packaging

Applications

• Programmable local oscillator

• FSK, PSK modulation

• Direct digital synthesis

• Clock generation

Pinout

48-PIN LQFP (Q48.7X7A)

TOP VIEW

C2

C1

C0

ENOFR

DGND

CLK

DVDD

RESET

UPDATE

COMPOUT

REFLO

REFIO

48 47 46 45 44 43 42 41 40 39 38 37

1 36

2 35

3 34

4 33

5 32

6

ISL5314

31

7 30

8 29

9 28

10 27

11 26

1213

14

15

16

17

18

19

20

21

22

23

25

24

A2

A3

PH0

PH1

SSYNC

DVDD

SCLK

DGND

DGND

SDATA

DVDD

DGND

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143 | Intersil and Design is a trademark of Intersil Corporation. | Copyright © Intersil Corporation 2000

CommLink™ is a trademark of Intersil Corporation.

1 page

ISL5314

IOUT(Full Scale) = (VFSADJ/RSET) X 32.

Analog Output

IOUTA and IOUTB are complementary current outputs. They

are generated by a 14-bit DAC that is capable of running at the

full 125MSPS rate. The DDS clock also clocks the DAC. The

sum of the two output currents is always equal to the full scale

output current minus one LSB. If single-ended use is desired, a

load resistor can be used to convert the output current to a

voltage. It is recommended that the unused output be equally

terminated. The voltage developed at the output must not

violate the output voltage compliance range of -1.0V to +1.25V.

RLOAD (the impedance loading each current output) should be

chosen so that the desired output voltage is produced in

conjunction with the output full scale current. If a known line

impedance is to be driven, then the output load resistor should

be chosen to match this impedance. The output voltage

equation is:

VOUT = IOUT X RLOAD .

These outputs can be used in a differential-to-single-ended

arrangement. This is typically done to achieve better harmonic

rejection. Because of a mismatch in IOUTA and IOUTB, the

transformer does not improve the harmonic rejection. However,

it can provide voltage gain without adding distortion. The SFDR

measurements in this data sheet were performed with a 1:1

transformer on the output of the DDS (see Figure 1). With the

center tap grounded, the output swing of pins 17 and 18 will be

biased at zero volts. The loading as shown in Figure 1 will result

in a 500mVP-P signal at the output of the transformer if the full

scale output current of the DAC is set to 20mA.

REQ IS THE IMPEDANCE

LOADING EACH OUTPUT

PIN 17

IOUTB

PIN 18

ISL5314

IOUTA

50Ω

100Ω

50Ω

VOUT = (2 x IOUT x REQ)VPP

50Ω

50Ω REPRESENTS THE

SPECTRUM ANALYZER

FIGURE 1. TRANSFORMER OUTPUT CIRCUIT OPTION

VOUT = 2 x IOUT x REQ, where REQ is 12.5Ω. Allowing the

center tap to float will result in identical transformer output,

however the output pins of the DAC will have positive DC

offset, which could limit the voltage swing available due to

the output voltage compliance range. The 50Ω load on the

output of the transformer represents the load at the end of a

‘transmission line’, typically a spectrum analyzer,

oscilloscope, or the next function in the signal chain. The

necessity to have a 50Ω impedance looking back into the

transformer is negated if the DDS is only driving a short

trace. The output voltage compliance range does limit the

impedance that is loading the DDS output.

Application Considerations

Ground Plane

Separate digital and analog ground planes should be used. All

of the digital functions of the device and their corresponding

components should be located over the digital ground plane

and terminated to the digital ground plane. The same is true for

the analog components and the analog ground plane. Pins 11

through 24 are analog pins, while all the others are digital.

Noise Reduction

To minimize power supply noise, 0.1µF capacitors should be

placed as close as possible to the power supply pins, AVDD

and DVDD . Also, the layout should be designed using

separate digital and analog ground planes and these

capacitors should be terminated to the digital ground for

DVDD and to the analog ground for AVDD . Additional

filtering of the power supplies on the board is recommended.

Power Supplies

The DDS will provide the best SFDR (spurious free dynamic

range) when using +5V analog and +5V digital power

supply. The analog supply must always be +5V (±10%). The

digital supply can be either a +3.3V (±10%), a +5V (±10%)

supply, or anything in between. The DDS is rated to

125MSPS when using a +5V digital supply and 100MSPS

when using a +3.3V digital supply.

Improving SFDR

+5V power supplies provides the best SFDR. Under some

clock and output frequency combinations, particularly when

the fCLK/fOUT ratio is less than 4, the user can improve

SFDR even further by connecting the COMP2 pin (19) of the

DDS to the analog power supply. The digital supply must be

+5V if this option is explored. Improvements as much as

6dBc in the SFDR-to-Nyquist measurement were seen in the

lab.

FSK Modulation

Binary frequency shift keying (BFSK) can be done by using

the offset frequency register and the ENOFR pin. M-ary FSK

or GFSK (Gaussian) can be done by continuously loading in

new frequency words. The maximum FSK data rate of the

ISL5314 depends on the way the user programs the device

to do FSK, and the form of FSK.

For example, simple BFSK is efficiently performed with the

ISL5314 by loading the center frequency register with one fre-

quency, the offset frequency register with another frequency,

and toggling the ENOFR (enable offset frequency register)

pin. The latency is fourteen CLK cycles between assertion of

the ENOFR pin and the change occurring at the analog out-

put. However, the change in frequency can be pipelined such

that the ENOFR can be toggled at a rate up to

ENOFRMAX = fCLK/2,

where fCLK is the frequency of the master CLK.

5

5 Page

ISL5314

from the value measured at room temperature to the value

m(fuelal sscuareledraatnegieth)epreTrMoICN. or TMAX . The units are ppm of FSR

Full Scale Gain Error is the error from an ideal ratio of 32

between the DAC output current and the full scale adjust

current (through RSET).

Internal Reference Voltage Drift is defined as the

maximum deviation from the value measured at room

temperature to the value measured

The units are ppm per oC.

at

either

TMIN

or

TMAX .

Offset Drift is measured by setting the DAC inputs to all

logic low (all 0’s) and measuring the output voltage through a

known resistance as the temperature is varied from TMIN to

TMAX . It is defined as the maximum deviation from the value

measured at room temperature to the value measured at

either TMIN

Range) per

doer gTrMeeAXo.CT. he

units

are

ppm

of

FSR

(Full

Scale

Offset Error is measured by setting the DAC inputs to all

logic low (all 0’s) and measuring the output voltage through a

known resistance. Offset error is defined as the maximum

deviation of the output current from a value of 0mA.

Output Settling Time is the time required for the output

voltage to settle to within a specified error band measured

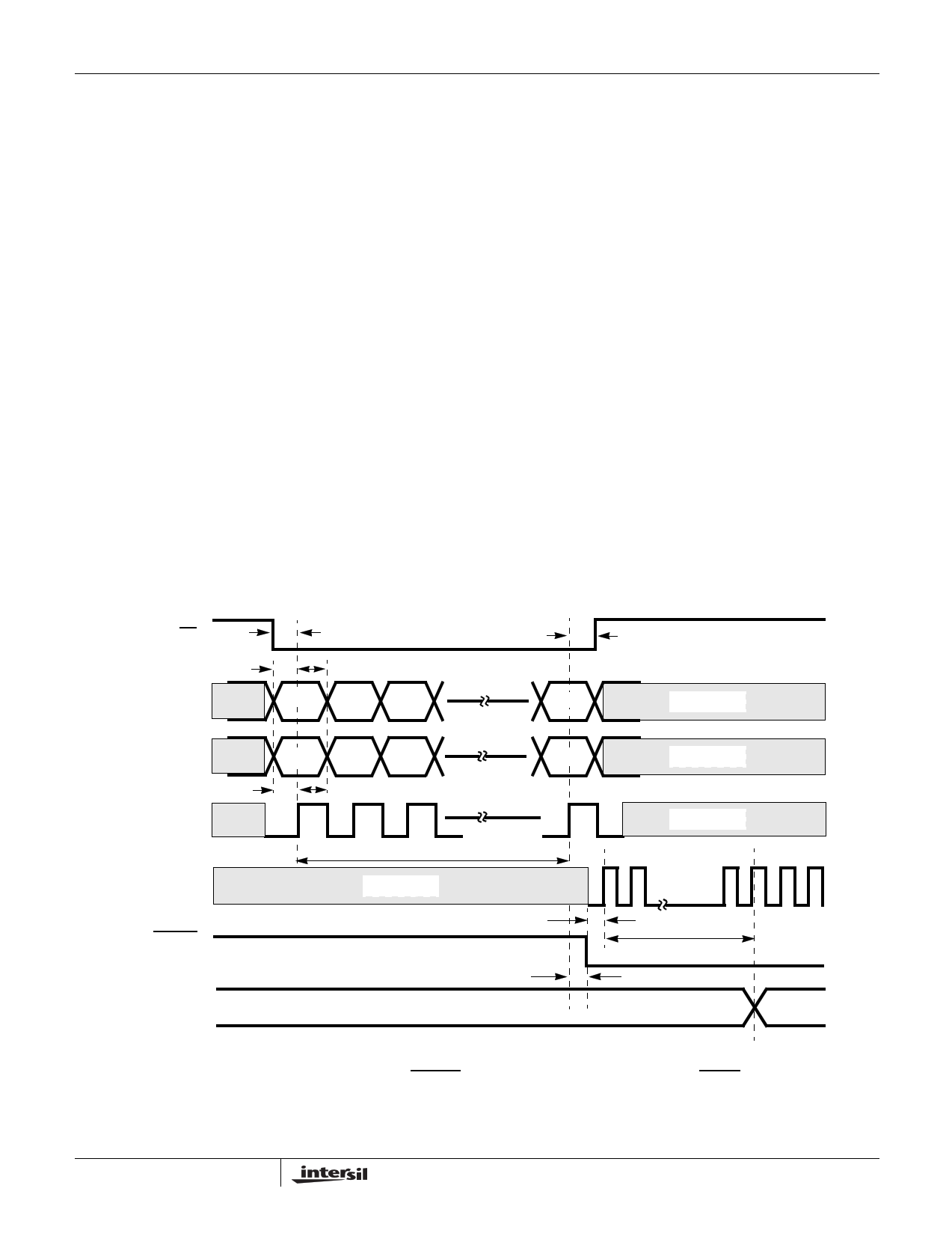

Timing Diagrams

from the beginning of the output transition. The

measurement is done by switching quarter scale.

Termination impedance was 25Ω due to the parallel

resistance of the 50Ω loading on the output and the

oscilloscope’s 50Ω input. This also aids the ability to resolve

the specified error band without overdriving the oscilloscope.

Output Voltage Compliance Range is the voltage limit

imposed on the output. The output impedance should be

chosen such that the voltage developed at either IOUTA or

IOUTB does not violate the compliance range.

Power Supply Rejection is measured using a single power

supply. The nominal supply is varied ±10% and the change

in the DAC full scale output current is noted.

Reference Input Multiplying Bandwidth is defined as the

3dB bandwidth of the voltage reference input. It is measured

by using a sinusoidal waveform as the external reference

with the digital inputs to the DAC set to all 1’s. The frequency

is increased until the amplitude of the output waveform is

0.707 (-3dB) of its original value.

Spurious Free Dynamic Range (SFDR) is the amplitude

difference from the fundamental signal to the largest

harmonically or non-harmonically related spur within the

specified frequency window.

WE

ADDR

tWS

tAS

A0

tAH

A1

A2

tWH

AN

DON’T CARE

DATA

WRITE

CLK (fCLK)

UPDATE

ANALOG OUT

W0

tDS

W1

tDH

W2

WN

1 WRITE CYCLE FOR EVERY REGISTER

DON’T CARE

DON’T CARE

DON’T CARE

tUS

tUD

tUL = 14 CLK RISING EDGES

OLD FREQ

NEW FREQ

FIGURE 3. PARALLEL-LOAD METHOD 1, UPDATE ACTIVE AFTER LOADING REGISTERS (RESET = HIGH)

11

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet ISL5314.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ISL5314 | Direct Digital Synthesizer | Intersil Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |