|

|

PDF ISB35389 Data sheet ( Hoja de datos )

| Número de pieza | ISB35389 | |

| Descripción | HCMOS STRUCTURED ARRAY | |

| Fabricantes | STMicroelectronics | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ISB35389 (archivo pdf) en la parte inferior de esta página. Total 15 Páginas | ||

|

No Preview Available !

ISB35000 SERIES

HCMOS STRUCTURED ARRAY

FEATURES

0.5 micron triple layer metal HCMOS process

featuring retrograde well technology, low

resistance salicided active areas, polysilicide

gates and thin metal oxide.

3.3 V optimized transistor with 5 V I/O interface

capability

2 - input NAND delay of 0.210 ns (typ) with

fanout = 2.

Broad I/O functionality including LVCMOS,

LVTTL, GTL, PECL, and LVDS.

High drive I/O; capability of sinking up to 48 mA

with slew rate control, current spike suppression

and impedance matching.

Metallised generators to support SPRAM and

DPRAM, plus an extensive embedded function

library.

Combines Standard Cell Features with Sea of

Gates time to market.

PRELIMINARY DATA

Fully independent power and ground

configurations for inputs, core and outputs.

Programmable I/O ring capability up to 1000

pads.

Output buffers capable of driving ISA, EISA,

PCI, MCA, and SCSI interface levels.

Active pull up and pull down devices.

Buskeeper I/O functions.

Oscillators for wide frequency spectrum.

Broad range of 400 SSI cells.

300 element macrofunction library.

Design For Test includes LSSD macro library

option and IEEE 1149.1 JTAG Boundary Scan

architecture built in.

Cadence and Mentor based design system with

interfaces from multiple workstations.

Broad ceramic and plastic package range.

Latchup trigger current +/- 500 mA.

ESD protection +/- 4000 volts.

Table 1. Product range

Internal

Device Name

Total Sites1

Estimated 2

Gates

Total Usable3

Gates

Maximum4

Device Pads

Maximum5

I/O

ISB35083

124,416

82,944

58,060

188

172

ISB35130

ISB35166

ISB35208

ISB35279

194,400

249,696

311,904

418,176

129,600

166,464

207,936

278,784

90,720

116,524

145,555

195,148

232

260

288

332

216

244

272

316

ISB35389

ISB35484

ISB35666

ISB35832

584,064

726,624

998,784

1,247,616

389,376

484,416

665,856

831,744

253,094

314,870

399,513

499,046

388

432

504

560

372

416

488

544

Notes : 1. Internal sites is based on the number of placement sites available to the route and place software

2. A factor of 1.5 is used to derive the gate complexity from the total available sites. This number is in Nand2 equivalents

3. Factors of 70%, 65%, and 60% have been used to calculate the routing efficiency. This number may vary depending on the

design.

4. 16 corner pads are dedicated to internal and external power supplies. I/O pads may be configured for additional power.

5. Maximum I/O = total device pads minus power pads.

May 1994

1/15

1 page

ISB35000 SERIES

buffers can be tristated by this function including

buffers that normally do not tristate. This test func-

tion also turns off all pull up or down devices and

shuts down all differential receivers and converts

them into standard CMOS receivers. Inside the

predriver is a section of specialized transistors used

to create the receiver functions. This section in-

cludes specialized non salicide protection resistor

diodes to further protect the gates of the receiver

devices from ESD and latch up. Also present in this

section are devices that can be utilized to form

various parameteriseable pull up, pull down and

buskeeper functions. A full set of standard receivers

with pull up and pull down devices is present in the

library. The technologies supported match the out-

put buffer capabilities and include, LVCMOS,

LVTTL, GTL, CTL, Differential, etc. and a five volt

interface capability. The last section of devices that

make up the I/O ring is a set of custom designed

(for compactness) scan latches and supporting cir-

cuits that can be utilized to form various types of

scan circuits conforming to the standard that the

customer is utilizing in his systems. These circuits

can be combined with internal transistors ifneeded.

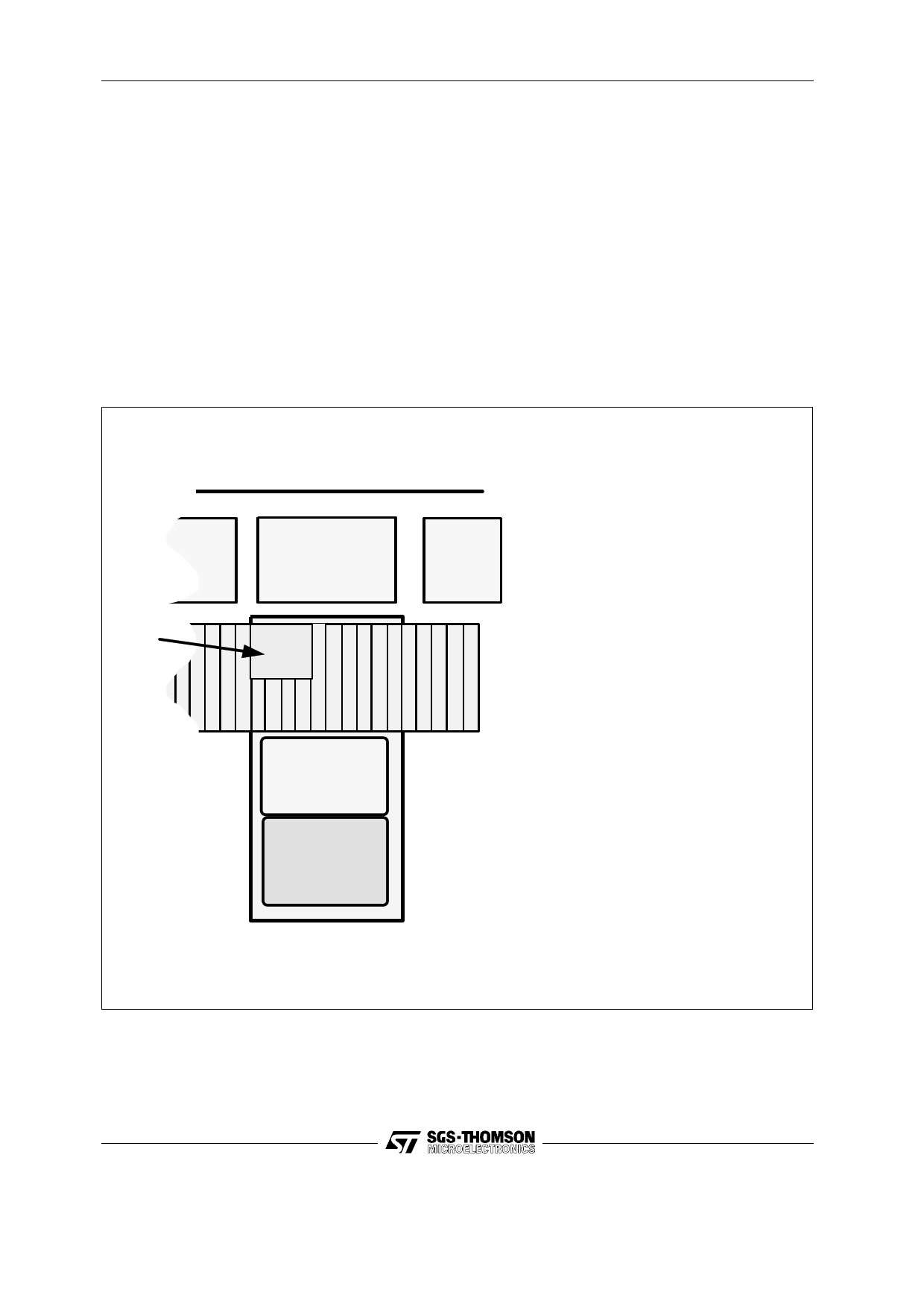

Figure 3. ISB35000 I/O Technology

4mA

selected

Edge of Die

Guardring

Programmable

Pitch Bond

Pad

Segmented

Output

River of Drive

Transistors

Input &

Control

SlewRate

Tristate

Buskeeper

Level Shifter

JTAG

Die Core

ISB35_PB

5/15

5 Page

ISB35000 SERIES

DESIGN ENVIRONMENT

Several interface levels are possible between SGS-

THOMSON and the customer in the undertaking of

an ASIC design. The four levels of interface are

shown in Figure 7. Level 1 is characterized by

SGS-THOMSON receiving the system specification

and taking the design through to validation and

fabrication. At level 2 interface the designer sup-

plies a complete logic design implemented in a

standard generic logic family. SGS-THOMSON

then takes the design through to layout, validation

and fabrication.

Level 3 is the most common and preferred interface

level. Logic capture and pre-layout simulation are

performed by the designer using an SGS-THOM-

SON supported design kit. The design is then taken

through layout, validation and fabrication by SGS-

THOMSON.

The SGS-THOMSON design system validates all

designs before fabrication. Design kits areprovided

that allow schematic capture entry via Mentor

Graphics and Cadence Amadeus. Simulation is

supported on Cadence Amadeus and Mentor

Graphics. Full support is also provided for Cadence

Verilog, Synopsys VSS and System Hilo simula-

tors. Figure 8 shows the SGS-THOMSON Design

Flow.

Figure 7. Customer/SGS-THOMSON Interface Levels

SYSTEM

SYSTEM

SPECIFICATION

LOGIC

DESIGN

SCHEMATIC

CAPTURE

DESIGN

VERIFICATION

PRE-LAYOUT

SIMULATION

LAYOUT

POST-LAYOUT

SIMULATION

MANUFACTURE

AND TEST

CUSTOMER

LEVEL 1

LEVEL 2

CUSTOMER

LEVEL 3

LEVEL 4

CUSTOMER

CUSTOMER

ISB35_VC

11/15

11 Page | ||

| Páginas | Total 15 Páginas | |

| PDF Descargar | [ Datasheet ISB35389.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ISB35389 | HCMOS STRUCTURED ARRAY | STMicroelectronics |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |