|

|

PDF IXPD610 Data sheet ( Hoja de datos )

| Número de pieza | IXPD610 | |

| Descripción | Bus Compatible Digital PWM Controller | |

| Fabricantes | IXYS Corp | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de IXPD610 (archivo pdf) en la parte inferior de esta página. Total 8 Páginas | ||

|

No Preview Available !

Bus Compatible Digital PWM Controller, IXDP 610

IXDP 610

Description

The IXDP610 Digital Pulse Width

Modulator (DPWM) is a programmable

CMOS LSI device which accepts digital

pulse width data from a microprocessor

and generates two complementary,

non-overlapping, pulse width modula-

ted signals for direct digital control of

switching power bridge. The DPWM is

designed to be operated under the

direct control of a microprocessor and

interfaces easily with most standard

microprocessor and microcomputer

buses. The IXDP610 is packaged in an

18-Pin slim DP.

The PWM waveform generated by the

IXDP610 results from comparing the

output of the Pulse Width counter to

the number stored in the Pulse Width

Latch (see below). A programmable

"dead-time" is incorporated into the

PWM waveform. The Dead-Time Logic

disables both outputs on each

transition of the Comparator output for

the required dead-time interval.

The output stage provides complemen-

tary PWM output signals capable of

sinking and sourcing 20 mA at TTL

voltage levels. The Output Disable

logic can be activated either by

software or hardware. This facilitates

cycle-by-cycle current-limit, short-

circuit, over-temperature, and

desaturation protection schemes.

The IXDP610 is capable of operating at

PWM frequencies from zero to 390kHz;

the dead-time is programmable from

zero to 14 clock cycles (0 to 11 % of

the PWM cycle), which allows

operation with fast power MOSFETs,

IGBTs, and bipolar power transistors. A

trade-off between PWM frequency and

resolution is provided by selecting the

counter resolution to be 7-bit or 8-bit.

The 20 mA output drive makes the

IXDP610 capable of directly driving

opto isolators and Smart Power

devices. The fast response to pulse

width commands is achieved by

instantaneous change of the outputs to

correspond to the new command. This

eliminates the one-cycle delay usually

associated with other digital PWM

implementations.

Features

G Microcomputer bus compatible

G Two complementary outputs for

direct control of a switching power

bridge

G Dynamically programmable pulse

width ranges from 0 to 100 %

G Two modes of operation: 7-bit or 8-

bit resolution

G Switching frequency range up to

390 kHz

G Programmable Dead-time Counter

prevents switching overlap

G Cycle-by-Cycle disable input to

protect against over-current, over-

temperature, etc.

G Outputs may be disabled under

software control

G Special locking bit prevents damage

to the stage in the event of a

software failure

G 18-pin slim DIP package

Dimensions in inch and mm

18-Pin Slim DIP

Symbol

VCC

VIN

Vout

PD

Tstg

1

Definition

Supply voltage

Input voltage

Output voltage

Maximum power dissipation

Storage temperature range

Maximum Ratings

-0.3 ... 5.5

-0.3 ... VCC + 0.3

-0.3 ... VCC + 0.3

500

V

V

V

mW

-40 ... 125 °C

© 2001 IXYS/DEI All rights reserved

1 page

IXDP 610

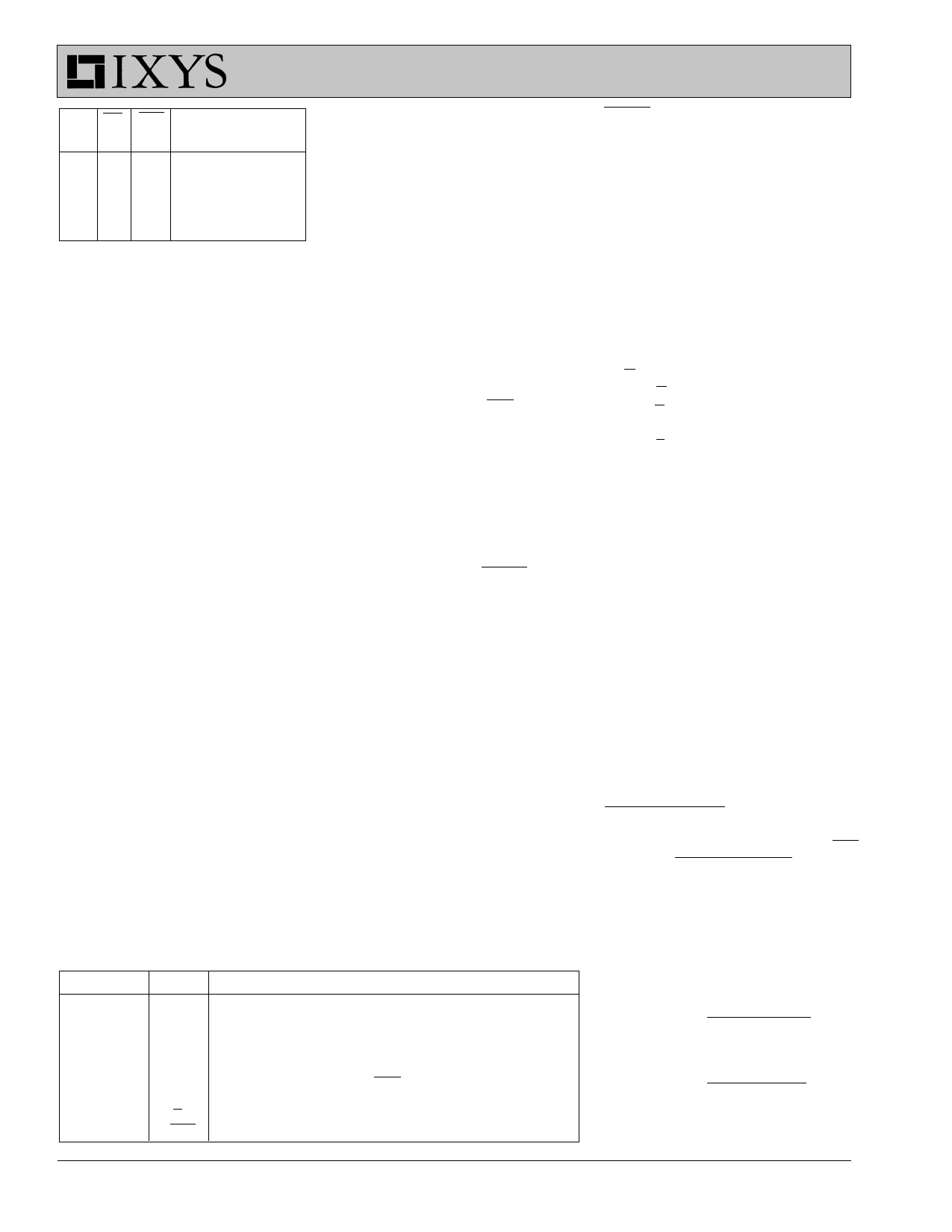

SEL CS WR Resulting

Function

X 1 X No Action

00

Load D0-D7

into PW latch

10

Load D0-D7

into Control Latch

Table 1 Bus Transaction Truth Table

operating parameters. Those bits are

summarized in Table 2.

Dead-time counter bits - these three

bits determine the dead-time period, as

defined by Fig. 2. Dead-time is that

period of time when both OUT1 and

OUT2 are low. Any binary number from

000 through 111 is valid. Thus, eight

different dead-time periods can be

programmed. DT0 is the least signifi-

cant bit and DT2 is the most significant

bit. A 000 binary means no dead-time

and a 111 means maximum dead-time.

Each dead-time count corresponds to

two CLOCK periods. For instance, if a

binary three (3) is programmed into the

dead-time bits, the dead-time will be six

external CLOCK cycles long.

The dead-time is provided to aid in

preventing switch overlap. The Dead-

time Counter delays turning on the

switch connected to OUT1 until the

switch connected to OUT2 has had

sufficient time to turn off; the comple-

ment is also true, the dead-time counter

delays turning on the switch connected

to OUT2 until the switch connected to

OUT1 has had sufficient time to turn off.

Since the dead-time counter is pro-

grammable, the user can optimize the

dead-time delay to suit their specific

application.

In a typical PWM cycle (refer to Fig. 2)

two dead-time periods will occur. One

follows the turnoff of OUT2. The dead-

time counter is triggered by an output

turning off. During a dead-time period,

both outputs are guaranteed to be off

(no dead-time periods occur during 0 %

and 100 % duty-cycle states). The dead-

time period overlaps the ontime of an

output, therefore, it shortens the on-time

without affecting the base PWM cycle

time. A dead-time period is only inserted

if an output changes from high to low (on

to off). Thus, if a PWM duty cycle is

chosen such that an output would be on

for a period of time equal to or less than

one dead-time period, the switch

associated with that output will not be

turned on during the PWM cycle. In this

special case, one will observe only dead-

time period per PWM cycle time, rather

than the two dead-time periods shown in

Fig. 2.

Lock bit - writing a one to this bit pre-

vents further writes to all bits in the

control latch, except the Stop bit. Thus, a

one should not be written to this bit until

the IXDP610 has been program-med.

Those writes that follow a one being

written to the Lock bit have no effect on

D0 through D6. The locking feature

provided by this bit prevents modification

of the control latch due to a software

error, thereby helping prevent damage to

the bridge being controlled by the

IXDP610. Asserting the RESET pin is

the only method by which the lock bit

can be cleared.

Divide bit - this bit sets the frequency of

the internal PWM clock. Writing a one to

this bit causes the external CLOCK to be

divided by two before being presented to

the PW counter. Writing a zero to this

bit results in no division of the external

CLOCK before it is presented to the PW

counter (“divide by one”). The Divide bit

has no affect on the dead-time Counter.

Resolution bit - writing a zero to this bit

chooses 7-bit counter resolution, while

writing a one chooses 8-bit PWM

counter resolution. Choosing 7-bit

resolution doubles the achieveable

PWM base frequency at the expense of

decreased duty cycle resolution. The

combination of the Divide bit and the

Resolution bit provides the user with

three different PWM base periods for a

given external CLOCK frequency. A

Control Bits Name Description

bit 0 DT0 for setting the dead-time period, all combinations are valid,

bit 1 DT1 0 is no dead-time delay and 7 is maximum dead-time.

bit 2 DT2

bit 3 not used, reserved; always write a zero to this bit

bit 4 Lock setting this bit prevents further access to all bits in the

Control latch, except the Stop bit.

bit 5 DIV determines frequency of the internal PWM clock.

bit 6 7/8 chooses between 7-bit and 8-bit resolution.

bit 7 Stop disables (turns off) the complementary outputs.

Table 2 Control Latch Bits

5

RESET programs the IXDP610 to

operate in the 8-bit resolution mode.

When the IXDP610 is programmed in 8-

bit mode, the PWM base period is equal

to 256 PWM clock cycles. In 7-bit mode

the PWM base period is equal to 128

PWM clock cycles. A PWM clock cycle

is equal to one external CLOCK period

when the Divide bit in the control latch is

a zero and is equal to two external

CLOCK periods when the Divide bit is a

one.

The following formula can be used to

determine the PWM base period:

If ((7/8 bit = 0) And (DIV bit = 0))

PWM base period CLOCK period x 128

else If ((7/8 bit = 0) And (DIV bit = 1))

PWM base period = CLOCK period x 256

else If ((7/8 bit = 1) And (DIV bit = 0))

PWM base period = CLOCK period x 256

else If ((7/8 bit = 1) And (DIV bit = 1))

PWM base period = CLOCK period x 512

The Pulse Width number that is written

to the Pulse Width latch represents the

high time of OUT1 (the low time of

OUT2). The Dead-time Counter

decreases the on-time (output high) of

an output by one dead-time period (tDT).

See Fig. 2 and the description of the

dead-time bits in the Control latch to

determine the duration of one dead-time

period.

Stop bit - writing a zero to this bit

immediately disables the complemen-

tary outputs (OUT1 and OUT2 are forced

to zero). As long as this bit is a zero, the

complementary outputs will be disabled.

This bit is not affected by the Lock bit.

This bit is equivalent in function to the

OUTPUT DISABLE input. The outputs

will not be re-enabled until the start of

the PWM period which has both the Stop

bit and the OUTPUT DISABLE input set

to ones.

PW latch - The binary number written to

the PW latch represents the duty cycle

of the complementary PWM outputs.

Percent duty cycle is defined as follows:

(assuming zero dead-time)

For OUT1:

% duty cycle =

time at 1

x 100

PWM cycle time

For OUT2:

% duty cycle =

time at 0

x 100

PWM cycle time

“PWM cycle time” is tCYCLE in Fig. 2.

© 2001 IXYS/DEI All rights reserved

5 Page | ||

| Páginas | Total 8 Páginas | |

| PDF Descargar | [ Datasheet IXPD610.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| IXPD610 | Bus Compatible Digital PWM Controller | IXYS Corp |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |