|

|

PDF ISP1181 Data sheet ( Hoja de datos )

| Número de pieza | ISP1181 | |

| Descripción | Full-speed Universal Serial Bus interface device | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de ISP1181 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

ISP1181

Full-speed Universal Serial Bus interface device

Rev. 01 — 13 March 2000

Objective specification

1. General description

c

c

2. Features

The ISP1181 is a Universal Serial Bus (USB) interface device which complies with

Universal Serial Bus Specification Rev. 1.1. It provides full-speed USB

communication capacity to microcontroller or microprocessor-based systems. The

ISP1181 communicates with the system’s microcontroller or microprocessor through

a high-speed general-purpose parallel interface.

The fully autonomous Direct Memory Access (DMA) operation - auto download, auto

repeat, auto execution - removes the need for the device to re-enable or re-initialize

the DMA operation every time.

The modular approach to implementing a USB interface device allows the designer to

select the optimum system microcontroller from the wide variety available. The ability

to re-use existing architecture and firmware investments shortens development time,

eliminates risks and reduces costs. The result is fast and efficient development of the

most cost-effective USB peripheral solution.

The ISP1181 is ideally suited for application in many personal computer peripherals,

such as printers, scanners, external mass storage (zip drive) devices and digital still

cameras. It offers an immediate cost reduction for applications that currently use

SCSI implementations.

s Complies with Universal Serial Bus Specification Rev. 1.1 and most Device Class

specifications

s High performance USB interface device with integrated Serial Interface Engine

(SIE), FIFO memory, transceiver and 3.3 V voltage regulator

s Interrupt endpoint can be configured in ‘rate feedback’ mode

s High speed (11.1 Mbyte/s or 90 ns read/write cycle) parallel interface

s Fully autonomous and multi-configuration DMA operation

s Up to 14 programmable USB endpoints with 2 fixed control IN/OUT endpoints

s Integrated physical 2462 bytes of multi-configuration FIFO memory

s Endpoints with double buffering to increase throughput and ease real-time data

transfer

s Seamless interface with most microcontrollers/microprocessors

s Bus-powered capability with low power consumption and low ‘suspend’ current

s 6 MHz crystal oscillator with integrated PLL for low EMI

1 page

Philips Semiconductors

ISP1181

Full-speed USB interface

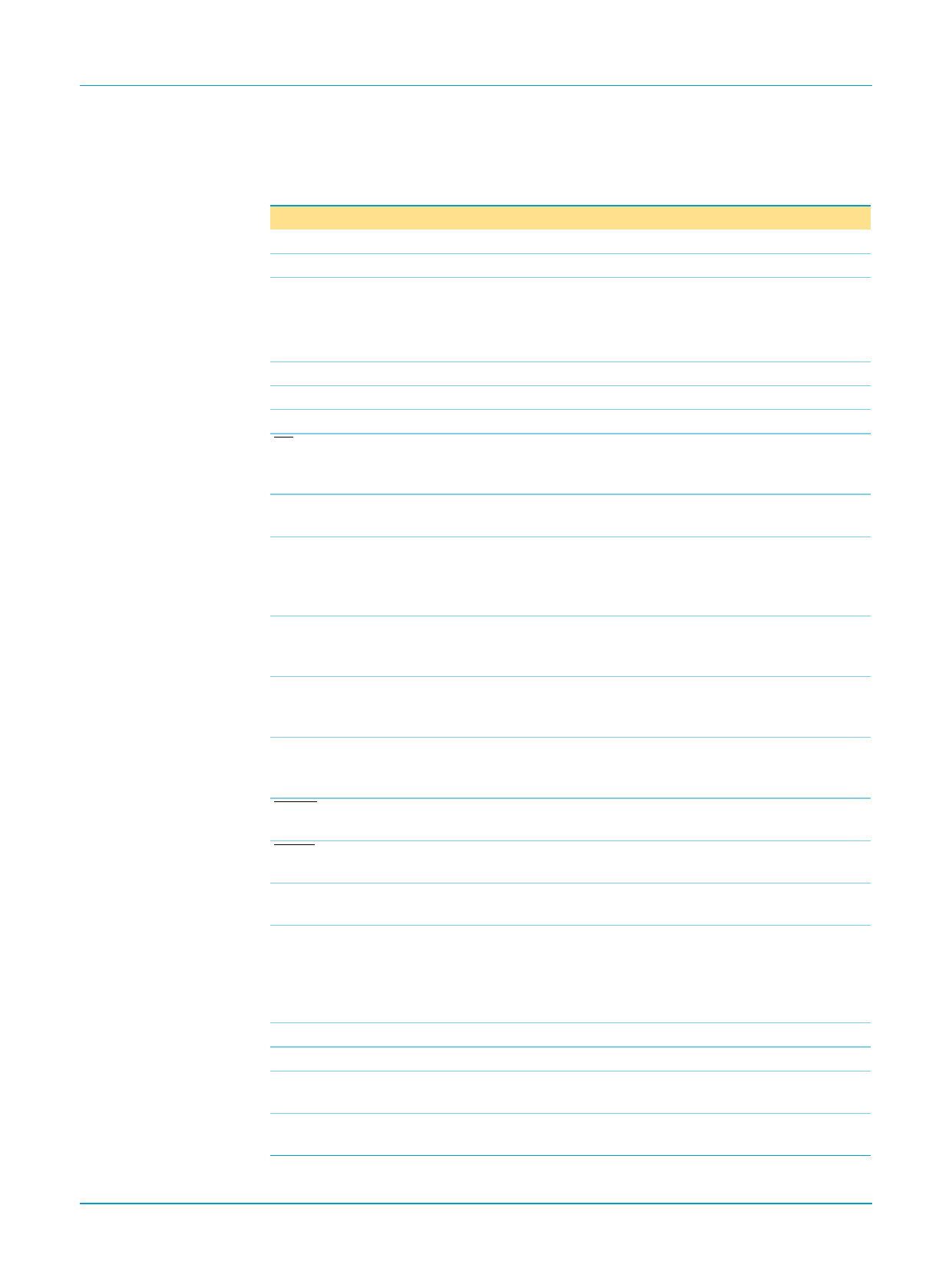

6.2 Pin description

Table 2: Pin description for TSSOP48

Symbol [1]

Pin Type Description

VCC(5.0)

REGGND

1-

2-

supply voltage (3.0 to 5.5 V)

voltage regulator ground supply

Vreg(3.3)

3-

regulated supply voltage (3.3 V ± 10%) from internal

regulator; used to connect decoupling capacitor and pull-up

resistor on D+ line;

Remark: Cannot be used to supply external devices.

D− 4 AI/O USB D− connection (analog)

D+ 5 AI/O USB D+ connection (analog)

VBUS

GL

6I

VBUS sensing input

7 O GoodLink LED indicator output (open-drain, 8 mA); the LED

is default ON, blinks OFF upon USB traffic; to connect an

LED use a 330 Ω series resistor;

WAKEUP

8I

wake-up input (edge triggered, LOW to HIGH); generates a

remote wake-up from ‘suspend’ state

SUSPEND 9

O ‘suspend’ state indicator output (4 mA); used as power switch

control output (active LOW) for powered-off application or as

resume signal to the CPU (active HIGH) for powered-on

application

EOT

10 I

End-Of-Transfer input (programmable polarity, see Table 23);

used by the DMA controller to force the end of a DMA transfer

by the ISP1181

DREQ

11 O

DMA request output (4 mA; programmable polarity, see

Table 23); signals to the DMA controller that the ISP1181

wants to start a DMA transfer

DACK

12 I

DMA acknowledge input (programmable polarity, see

Table 23); used by the DMA controller to signal the start of a

DMA transfer requested by the ISP1181

SDWR

13 I

DMA write strobe input; used only in bus configuration

mode 1 (separate PIO and DMA ports)

SDRD

14 I

DMA read strobe input; used only in bus configuration

mode 1 (separate PIO and DMA ports)

INT

15 O

interrupt output; programmable polarity (active HIGH or LOW)

and signalling (level or pulse); see Table 23

READY

16 O

I/O ready output; a LOW level indicates that ISP1181 is

processing a previous command or data and is not ready for

the next PIO command or data transfer; a HIGH level signals

that ISP1181 will complete a PIO data transfer; applies only

to a PIO port or a PIO port shared with a DMA port

BUS_CONF1 17 I

bus configuration selector; see Table 3

BUS_CONF0 18 I

bus configuration selector; see Table 3

DATA15

19 I/O bit 15 of D[15:0]; bi-directional data line (slew-rate controlled

output, 4 mA)

DATA14

20 I/O bit 14 of D[15:0]; bi-directional data line (slew-rate controlled

output, 4 mA)

9397 750 06896

Objective specification

Rev. 01 — 13 March 2000

© Philips Electronics N.V. 2000. All rights reserved.

5 of 69

5 Page

Philips Semiconductors

ISP1181

Full-speed USB interface

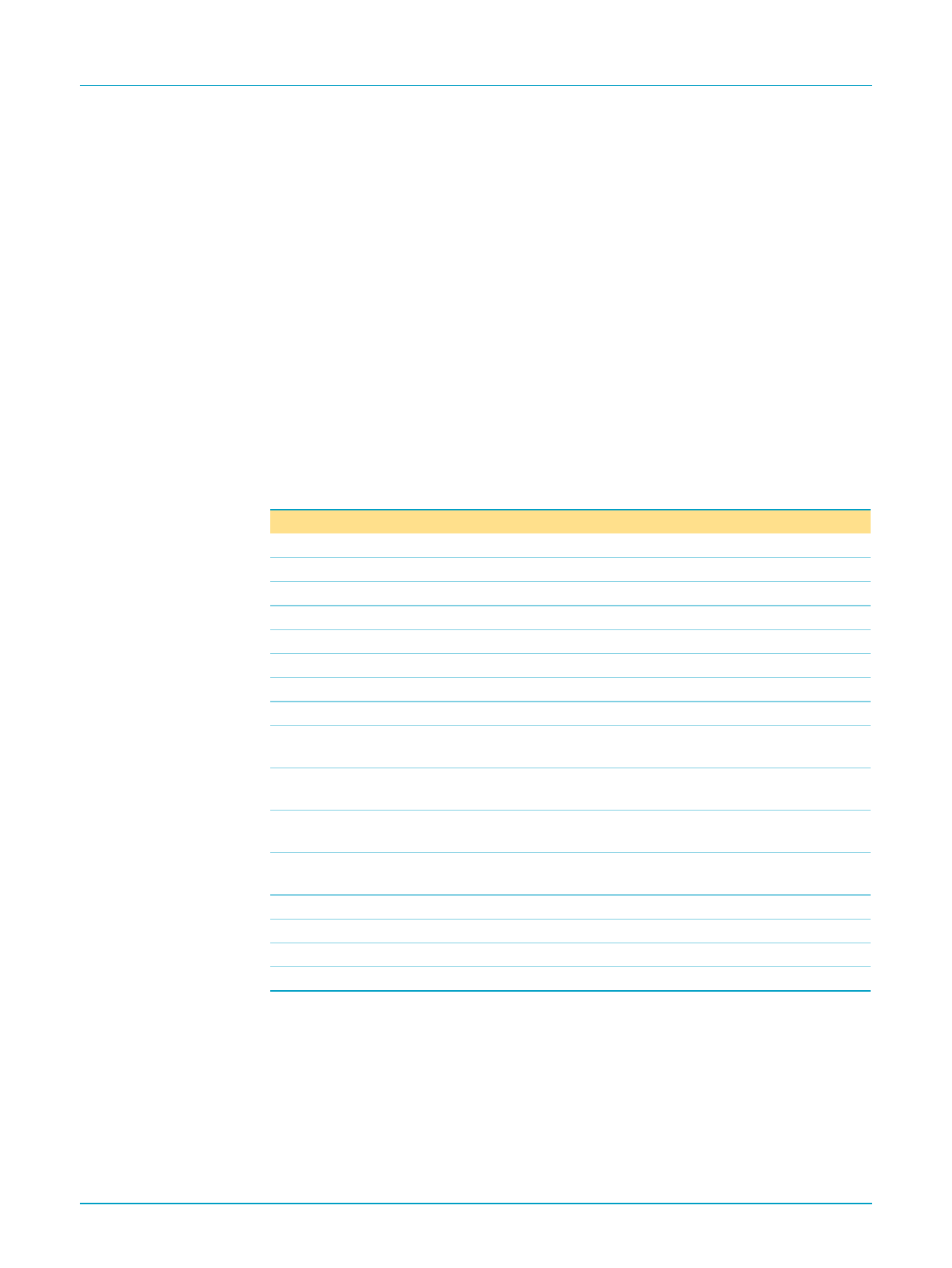

9.2 Endpoint FIFO size

The size of the FIFO determines the maximum packet size that the hardware can

support for a given endpoint. Only enabled endpoints are allocated space in the

shared FIFO storage, disabled endpoints have zero bytes. Table 5 lists the

programmable FIFO sizes.

The following bits in the Endpoint Configuration Register (ECR) affect FIFO

allocation:

• endpoint enable bit (FIFOEN)

• size bits of an enabled endpoint (FFOSZ[3:0])

• isochronous bit of an enabled endpoint (FFOISO).

Remark: Register changes that affect the allocation of the shared FIFO storage

among endpoints must not be made while valid data is present in any FIFO of the

enabled endpoints. Such changes will render all FIFO contents undefined.

Table 5: Programmable FIFO size

FFOSZ[3:0]

Non-isochronous

0000

8 bytes

0001

16 bytes

0010

32 bytes

0011

64 bytes

0100

reserved

0101

reserved

0110

reserved

0111

reserved

1000

interrupt IN 8 bytes,

rate feedback mode

1001

interrupt IN 16 bytes,

rate feedback mode

1010

interrupt IN 32 bytes,

rate feedback mode

1011

interrupt IN 64 bytes,

rate feedback mode

1100

reserved

1101

reserved

1110

reserved

1111

reserved

Isochronous

16 bytes

32 bytes

48 bytes

64 bytes

96 bytes

128 bytes

160 bytes

192 bytes

256 bytes

320 bytes

384 bytes

512 bytes

640 bytes

768 bytes

896 bytes

1023 bytes

Each programmable FIFO can be configured independently via its ECR, but the total

physical size of all enabled endpoints (IN plus OUT) must not exceed 2462 bytes

(512 bytes for non-isochronous FIFOs).

Table 6 shows an example of a configuration fitting in the maximum available space of

2462 bytes. The total number of logical bytes in the example is 1311. The physical

storage capacity used for double buffering is managed by the device hardware and is

transparent to the user.

9397 750 06896

Objective specification

Rev. 01 — 13 March 2000

© Philips Electronics N.V. 2000. All rights reserved.

11 of 69

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet ISP1181.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ISP1181 | Full-speed Universal Serial Bus interface device | NXP Semiconductors |

| ISP1181A | Full-speed Universal Serial Bus peripheral controller | Philips |

| ISP1183 | Low-power Universal Serial Bus interface device with DMA | NXP Semiconductors |

| ISP1183BS | Low-power Universal Serial Bus interface device with DMA | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |