|

|

PDF 73K222AL-IGT Data sheet ( Hoja de datos )

| Número de pieza | 73K222AL-IGT | |

| Descripción | V.22/ V.21/ Bell 212A/ 103 Single-Chip Modem | |

| Fabricantes | ETC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de 73K222AL-IGT (archivo pdf) en la parte inferior de esta página. Total 28 Páginas | ||

|

No Preview Available !

73K222AL

V.22, V.21, Bell 212A, 103

Single-Chip Modem

DESCRIPTION

The 73K222AL is a highly integrated single-chip

modem IC which provides the functions needed to

construct a CCITT V.22, V.21 and Bell 212A

compatible modem, capable of 1200 bit/s full-duplex

operation over dial-up lines. The 73K222AL is an

enhancement of the 73K212L/AL single-chip modem

which adds V.22 and V.21 modes to the Bell 212A and

103 operation of the 73K212AL. In Bell 212A mode,

the 73K222AL provides the normal Bell 212A and 103

functions and employs a 2225 Hz answer tone. The

73K222AL in V.22 mode produces either 550 or 1800

Hz guard tone, recognizes and generates a 2100 Hz

answer tone, and allows 600 bit/s V.22 or 0-300 bit/s

V.21 operation. The 73K222AL integrates analog,

digital, and switched-capacitor array functions on a

single substrate, offering excellent performance and a

high level of functional integration in a single 28-pin

DIP, PLCC and 44-pin TQFP configuration. The

73K222AL operates from a single +5V supply. The

73K222AL is a new version replacing the 73K222L.

The 73K222AL should be specified for all new

designs.

The 73K222AL includes the DPSK and FSK

modulator/demodulator functions, call progress and

handshake tone monitor and a tone generator capable

of tone required for European applications.

(continued)

FEATURES

April 2000

• One-chip CCITT V.22, V.21, Bell 212A and Bell

103 standard compatible modem data pump

• Full-duplex operation at 0-300 bit/s (FSK) or 600

and 1200 bit/s (DPSK)

• Pin and software compatible with other TDK

Semiconductor Corporation K-Series 1-chip

modems

• Interfaces

directly

with

standard

microprocessors (8048, 80C51 typical)

• Serial or parallel microprocessor bus for control

• Serial port for data transfer

• Both synchronous and asynchronous modes of

operation including V.22 extended overspeed

• Call progress, carrier, precise answer tone

(2100 or 2225 Hz), and long loop detectors

• DTMF, and 550 or 1800 Hz guard tone

generators

• Test modes available: ALB, DL, RDL, Mark,

Space, Alternating bit patterns

• Precise automatic gain control allows 45 dB

dynamic range

• CMOS technology for low power consumption

using 60 mW @ 5V

• Single +5 volt supply

• PLCC and PDIP packages

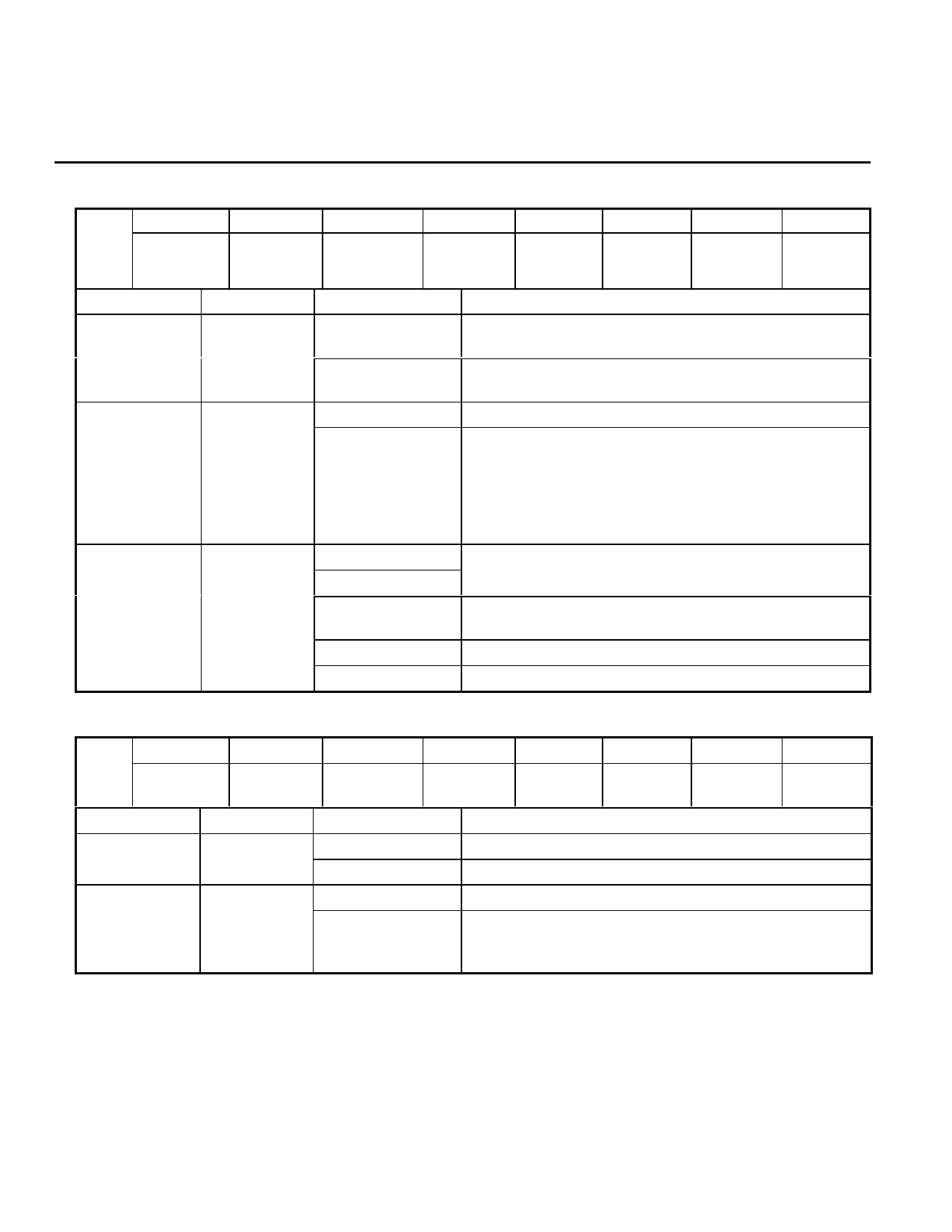

AD0-AD7

RD

WR

ALE

CS

RESET

INT

TXD

RXD

DATA

BUS

BUFFER

READ

WRITE

CONTROL

LOGIC

STATUS

AND

CONTROL

LOGIC

BLOCK DIAGRAM

8-BIT

BUS

FOR

CONTROL

AND

STATUS

SERIAL

PORT

FOR

DATA

DIGITAL

PROCESSING

TESTS:

ALB, DLB

RDLB

PATTERNS

CLOCK

GENERATOR

FSK

MODULATOR/

DEMODULATOR

PSK

MODULATOR/

DEMODULATOR

SMART

DIALING

&

DETECT

FUNCTIONS

POWER

DTMF &

TONE

GENERATORS

TRANSMIT

FILTER

RECEIVE

FILTER

TXA

RXA

1 page

73K222AL

V.22, V.21, Bell 212A, 103

Single-Chip Modem

PARALLEL MICROPROCESSOR INTERFACE (continued)

NAME

WR

28-PIN

13

TYPE

I

DESCRIPTION

Write. A low on this informs the 73K222AL that data is available on

AD0-AD7 for writing into an internal register. Data is latched on the

rising edge of WR. No data is written unless both WR and the latched

CS are low.

SERIAL MICROPROCESSOR INTERFACE

A0-A2

- I Register Address Selection. These lines carry register addresses and

should be valid during any read or write operation.

DATA

- I/O Serial Control Data. Data for a read/write operation is clocked in or out

on the falling edge of the EXCLK pin. The direction of data flow is

controlled by the RD pin. RD low outputs data. RD high inputs data.

RD - I Read. A low on this input informs the 73K222AL that data or status

information is being read by the processor. The falling edge of the RD

signal will initiate a read from the addressed register. The RD signal

must continue for eight falling edges of EXCLK in order to read all eight

bits of the referenced register. Read data is provided LSB first. Data

will not be output unless the RD signal is active.

WR - I Write. A low on this input informs the 73K222AL that data or status

information has been shifted in through the DATA pin and is available

for writing to an internal register. The normal procedure for a write is to

shift in data LSB first on the DATA pin for eight consecutive falling

edges of EXCLK and then to pulse WR low. Data is written on the

rising edge of WR.

NOTE: The serial control mode is provided by tying ALE high and CS low. In this configuration AD7 becomes

DATA and AD0, AD1 and AD2 become the address only. See timing diagrams on page 20.

5

5 Page

73K222AL

V.22, V.21, Bell 212A, 103

Single-Chip Modem

CONTROL REGISTER 1 (continued)

CR1

001

D7

TRANSMIT

PATTERN

1

D6

TRANSMIT

PATTERN

0

BIT NO.

NAME

D4 Bypass

Scrambler

D5 Enable

Detect

D7, D6

Transmit

Pattern

D5 D4 D3 D2 D1 D0

ENABLE

DETECT

INTER.

BYPASS

CLK

SCRAMB CONTROL

RESET

TEST

MODE

1

TEST

MODE

0

CONDITION DESCRIPTION

0 Selects normal operation. DPSK data is passed through

scrambler.

1 Selects Scrambler Bypass. Bypass DPSK data is routed

around scrambler in the transmit path.

0 Disables interrupt at INT pin.

1 Enables INT output. An interrupts will be generated with

a change in status of DR bits D1-D4. The answer tone

and call progress detect interrupts are masked when the

TX enable bit is set. Carrier detect is masked when TX

DTMF is activated. All interrupts will be disabled if the

device is in power down mode.

D7 D6

00

Selects normal data transmission as controlled by the

state of the TXD pin.

01

Selects an alternating mark/space transmit pattern for

modem testing.

10

Selects a constant mark transmit pattern.

11

Selects a constant space transmit pattern.

DETECT REGISTER

D7

DR

010

X

D6

X

BIT NO.

D0

NAME

Long Loop

D1 Call Progress

Detect

D5 D4 D3 D2 D1 D0

RECEIVE

DATA

UNSCR.

MARK

CARR. ANSWER

DETECT TONE

CALL

PROG.

LONG

LOOP

CONDITION

DESCRIPTION

0 Indicates normal received signal.

1 Indicates low received signal level.

0 No call progress tone detected.

1 Indicates presence of call progress tones. The call

progress detection circuitry is activated by energy in the

350 to 620 Hz call progress band.

11

11 Page | ||

| Páginas | Total 28 Páginas | |

| PDF Descargar | [ Datasheet 73K222AL-IGT.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 73K222AL-IGT | V.22/ V.21/ Bell 212A/ 103 Single-Chip Modem | ETC |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |