|

|

PDF 74F109SC Data sheet ( Hoja de datos )

| Número de pieza | 74F109SC | |

| Descripción | Dual JK Positive Edge-Triggered Flip-Flop | |

| Fabricantes | National Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de 74F109SC (archivo pdf) en la parte inferior de esta página. Total 10 Páginas | ||

|

No Preview Available !

November 1994

54F/74F109

Dual JK Positive Edge-Triggered Flip-Flop

General Description

The ’F109 consists of two high-speed, completely indepen-

dent transition clocked JK flip-flops. The clocking operation

is independent of rise and fall times of the clock waveform.

The JK design allows operation as a D flip-flop (refer to ’F74

data sheet) by connecting the J and K inputs.

Asynchronous Inputs:

LOW input to SD sets Q to HIGH level

LOW input to CD sets Q to LOW level

Clear and Set are independent of clock

Simultaneous LOW on CD and SD makes both Q and Q

HIGH

Features

n Guaranteed 4000V minimum ESD protection.

Ordering Code: See Section 0

Commercial

Military

74F109PC

74F109SC (Note 1)

54F109DM (Note 2)

74F109SJ (Note 1)

54F109FM (Note 2)

54F109LM (Note 2)

Package

Number

N16E

J16A

M16A

M16D

W16A

E20A

Package Description

16-Lead (0.300" Wide) Molded Dual-in-Line

16-Lead Ceramic Dual-in-Line

16-Lead (0.150" Wide) Molded Small Outline,

JEDEC

16-Lead (0.300" Wide) Molded Small Outline,

EIAJ

16-Lead Cerpack

16-Lead Ceramic Leadless Chip Carrier, Type C

Note 1: Devices also available in 13" reel. Use suffix = SCX and SJX.

Note 2: Military grade device with environmental and burn-in processing. Use suffix = DMQB, FMQB and LMQB.

Logic Symbols

IEEE/IEC

DSXXX

DS009471-3

DS009471-4

DS009471-6

FAST® and TRI-STATE® are registered trademarks of National Semiconductor Corporation.

© 1997 National Semiconductor Corporation DS009471

PrintDate=1997/08/28 PrintTime=11:45:22 10182 ds009471 Rev. No. 1 cmserv Proof

www.national.com

1

1

1 page

AC Electrical Characteristics (Continued)

See Section 0 for Waveforms and Load Configurations

Symbol

Parameter

74F

TA = +25˚C

VCC = +5.0V

CL = 50 pF

Min Typ Max

tPLH

tPHL

tPLH

tPHL

Propagation Delay

CPn to Qn or Qn

Propagation Delay

CDn or SDn to

Qn or Qn

3.8 5.3 7.0

4.4 6.2 8.0

3.2 5.2 7.0

3.5 7.0 9.0

54F

TA, VCC = Mil

CL = 50 pF

Min Max

3.8 9.0

4.4 10.5

3.2 9.0

3.5 11.5

74F

TA, VCC = Com

CL = 50 pF

Units

Fig.

No.

Min Max

3.8 8.0

4.4 9.2

3.2 8.0

3.5 10.5

ns kk-kk

ns kk-kk

AC Operating Requirements

See Section 0 for Waveforms

Symbol

Parameter

74F

TA = +25˚C

VCC = +5.0V

Min Max

ts(H)

ts(L)

th(H)

th(L)

tw(H)

tw(L)

tw(L)

Setup Time, HIGH or LOW

Jn or Kn to CPn

Hold Time, HIGH or LOW

Jn or Kn to CPn

CPn Pulse Width

HIGH or LOW

CDn or SDn Pulse Width,

LOW

3.0

3.0

1.0

1.0

4.0

5.0

4.0

trec Recovery Time

CDn or SDn to CP

2.0

54F

TA, VCC = Mil

Min Max

3.0

4.0

1.0

1.0

4.0

5.0

4.0

74F

TA, VCC = Com

Min Max

3.0

3.0

1.0

1.0

4.0

5.0

4.0

Units

ns

ns

ns

Fig.

No.

kk-kk

kk-kk

kk-kk

2.0 2.0 ns kk-kk

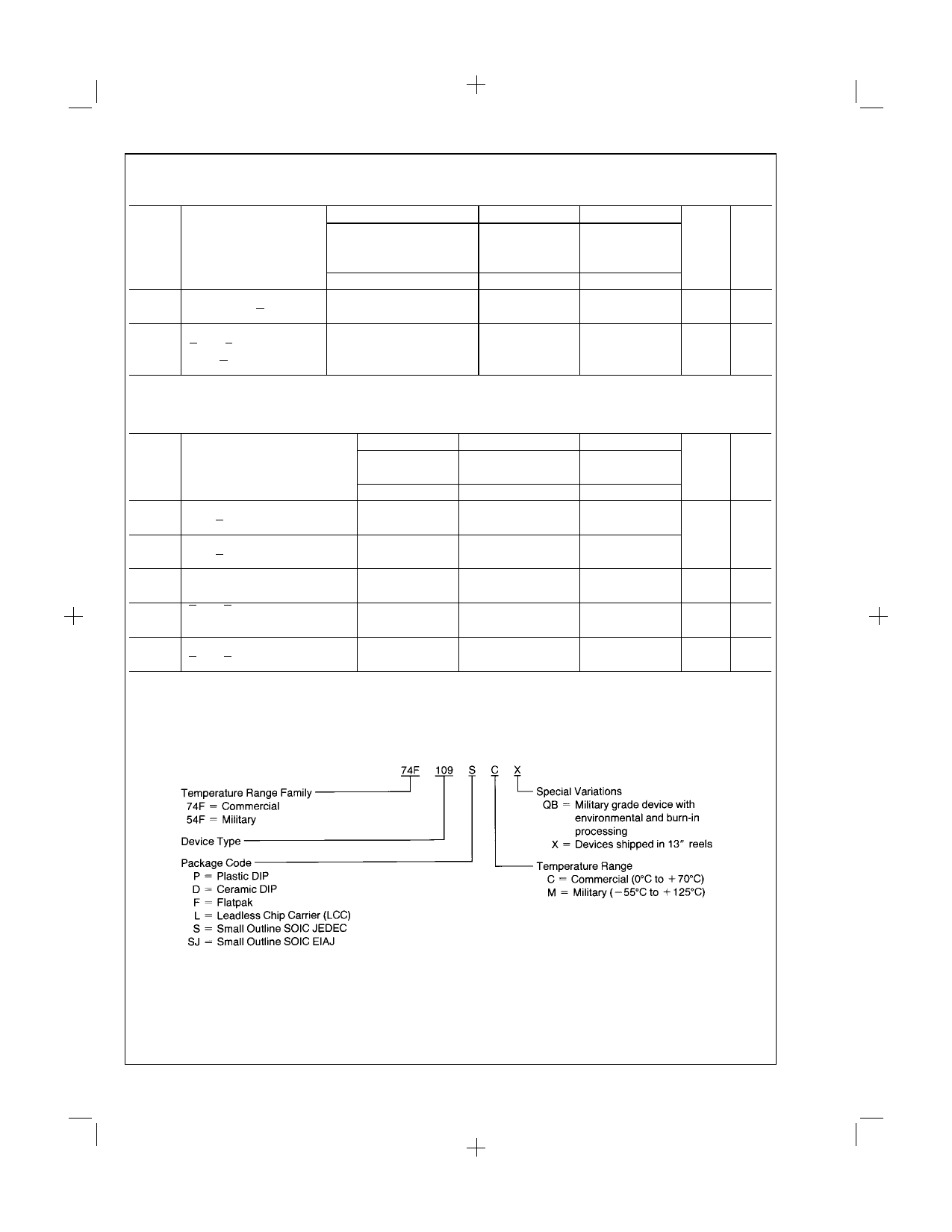

Ordering Information

The device number is used to form part of a simplified purchasing code where the package type and temperature range are de-

fined as follows:

DSXXX

DSXXX

DSXXX

DSXXX

DSXXX

DSXXX

DSXXX

DSXXX

Book

Extract

End

DS009471-7

5

PrintDate=1997/08/28 PrintTime=11:45:30 10182 ds009471 Rev. No. 1 cmserv Proof

www.national.com

5

5 Page | ||

| Páginas | Total 10 Páginas | |

| PDF Descargar | [ Datasheet 74F109SC.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 74F109SC | Dual JK Positive Edge-Triggered Flip-Flop | Fairchild Semiconductor |

| 74F109SC | Dual JK Positive Edge-Triggered Flip-Flop | National Semiconductor |

| 74F109SJ | Dual JK Positive Edge-Triggered Flip-Flop | Fairchild Semiconductor |

| 74F109SJ | Dual JK Positive Edge-Triggered Flip-Flop | National Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |